Sdr u

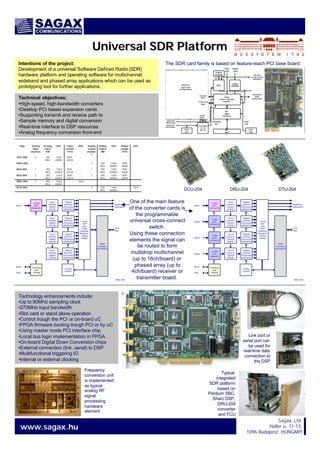

- 1. Universal SDR Platform Intentions of the project: Development of a universal Software Defined Radio (SDR) hardware platform and operating software for multichannel, wideband and phased array applications which can be used as prototyping tool for further applications. Analog input channels Analog input BW ADC Input sample FIFO DDC DIU-202 2 250 MHz 14bit 65MHz 2KW65KW 1 - 2 DRU-204 4 2KW65KW 2KW65KW - 1 2 14bit 65MHz 14bit 65MHz 14bit 65MHz - DCU-204 250 MHz 250 MHz 250 MHz Different front-end configurations CLK DRV /2, /4 X2, X4 SCLK OSC Output sample FIFO 300 MHz 300 MHz 300 MHz 14bit 80MHz 14bit 80MHz 14bit 80MHz 2KW65KW 2KW65KW 2KW65KW PCI HOST Interface 14bit 80MHz - 16ch Sampling CLK Local CLK LCLK OSC PCI BUS - 300 MHz Dedicated data connection FPGA LOGIC and DSP resource DUC 2 Config EEPROM FPGA CFG External TRG in/out External CLK in/out DAC RS-232 serial control interface MCU Clock lines Analog output BW PROM JTAG I2C Front-end BUS Analog output channel s FPGA JTAG - DCU-202 Control EEPROM Control BUS Technical objectives: •High-speed, high-bandwidth converters •Desktop PCI based expansion cards •Supporting transmit and receive path to •Sample memory and digital conversion •Real-time interface to DSP resources •Analog frequency conversion front-end Type The SDR card family is based on feature-reach PCI base board: DOU-202 4 Cross Connect Switch (CPLD) Digital Receive Processor (AD6624) Cross Connect Switch (CPLD) 14-Bit ADC (AD6644) Digital Receive Processor (AD6624) Cross Connect Switch (CPLD) RCLK TRG Clocking and Timing Digital Receive Processor (AD6624) Cross Connect Switch (CPLD) - 16ch DTU-204 RCh1 - Digital Receive Processor (AD6624) Dedicted Data ports Local DSP and Data Routing Resource (Xilinx FPGA) PCI Bus HOST Interface (PLX9054) Config Control DRU-204 DCU-204 One of the main feature of the converter cards is the programmable universal cross-connect switch. Using these connection elements the signal can be routed to form multidrop multichannel (up to 16ch/board) or phased array (up to 4ch/board) receiver or transmitter board. DRU-204 RCh1 14-Bit ADC (AD6644) Cross Connect Switch (CPLD) Digital Receive Processor (AD6624) RCh2 14-Bit ADC (AD6644) Cross Connect Switch (CPLD) Digital Receive Processor (AD6624) 14-Bit ADC (AD6644) Cross Connect Switch (CPLD) Digital Receive Processor (AD6624) 14-Bit ADC (AD664) Cross Connect Switch (CPLD) Digital Receive Processor (AD6624) RCh3 RCh4 RCLK TRG Clocking and Timing www.sagax . www.sagax.hu Dedicted Data ports Local DSP and Data Routing Resource (Xilinx FPGA) PCI Bus HOST Interface (PLX9054) Config Control DRU-204 Technology enhancements include: •Up to 80MHz sampling clock •270MHz input bandwidth •Slot card or stand alone operation •Control trough the PCI or on-board uC •FPGA firmware booting trough PCI or by uC •Using master mode PCI interface chip •Local bus logic implementation in FPGA •On-board Digital Down Conversion chips •External connection (link, serial) to DSP •Multifunctional triggering IO •Internal or external clocking Frequency conversion unit is implemented as typical analog RF signal processing hardware element DTU-204 Link port or serial port can be used for real-time data connection to the DSP Typical integrated SDR platform based on Pentium SBC, Sharc DSP, DRU-204 converter and FCU Sagax, Ltd. Sagax, Ltd. Haller u. 11-13. 1096 Budapest, HUNGARY