Bab 5 komputer sederhana sap-1

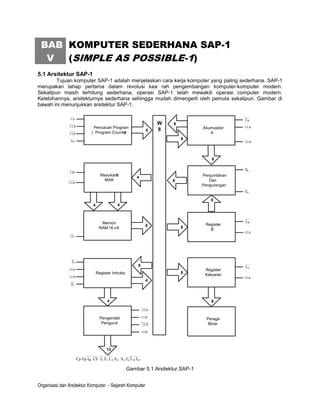

- 1. BAB KOMPUTER SEDERHANA SAP-1 V (SIMPLE AS POSSIBLE-1) 5.1 Arsitektur SAP-1 Tujuan komputer SAP-1 adalah menjelaskan cara kerja komputer yang paling sederhana. SAP-1 merupakan tahap pertama dalam revolusi kea rah pengembangan komputer-komputer modern. Sekalipun masih terhitung sederhana, operasi SAP-1 telah mewakili operasi computer modern. Kelebihannya, arsitekturnya sederhana sehingga mudah dimengerti oleh pemula sekalipun. Gambar di bawah ini menunjukkan arsitektur SAP-1. Cp LA W 8 CLK Pencacah Program CLK 8 Akumulator 4 CLR ( Program Counter ) A Ep 8 CLR 8 Su LM Masukan& Penjumlahan 4 MAR 8 Dan CLK Pengurangan Eu 8 4 4 Memori LB 8 Register RAM 16 x 8 8 B CLK CE Li 8 Lo CLK Register Register Intruksi 8 CLR Keluaran CLK 4 Ei 4 8 CLK Pengendali CLK Peraga Pengurut CLR Biner CLR 12 Cp Ep L CE Li E i L A EA S u Eu L B L0 M Gambar 5.1 Arsitektur SAP-1 Organisasi dan Arsitektur Komputer - Sejarah Komputer

- 2. Penahanan Tiga Keadaan (Three State Buffer, TSB) DIn DOut Semua keluaran register menuju W bus yang dikendalikan oleh penahan tiga keadaan (three state buffer, TSB) yang memungkinkan transfer data dari ENABLE register ke bus secara teratur. Gambar 5.2 Saklar Tiga Keadaan (Three State Buffer, TSB) Keluaran dari TSB, DOut, memungkinkan tiga kondisi : 1, 0 atau hambatan tinggi (impedansi tinggi). Pada saat ENABLE = 0 maka terjadi hambatan tinggi pada TSB sehingga tidak ada data yang mengalir dari Din menuju DOut. Pada SAP-1, TSB banyak digunakan untuk menahan data dari register menuju ke W bus atau sebaliknya. CLK, CLK, CLR, CLR Jalur kendali umum yang hampir ada pada setiap komponen dalam computer. Fungsi umum masing- masing jalur : CLK : Memicu pengaktifan komponen dengan mode active high, akan aktif jika nilainya = 1 CLK : Memicu pengaktifan komponen dengan mode active low, akan aktif jika nilainya = 0 CLR : Me-RESET komponen dengan mode active high, akan aktif jika nilainya = 1 CLR : Me-RESET komponen dengan mode active low, akan aktif jika nilainya = 0 Berikut ini adalah uraian singkat dari setiap kotak diagram dan penjelasannya : a. Pencacah Program (Program Counter – PC) Program, dalam SAP-1, disimpan pada memori RAM dengan intruksi pertama diletakan pada alam biner 0000, intruksi kedua pada alamat 0001, intruksi ketiga pada alamat 0010 dan seterusnya. Data biasanya disimpan pada bagian akhir memori. Pencacah program yang merupakan bagian dari unit kendali (control unit) bertugas mencacah dari 0000 sampai dengan 1111. Keluaran dari pencacah akan memajukan alamat intruksi berikutnya yang akan dieksekusi. Cp CLK Pencacah Program (Program Counter) 4 W CLR Ep Gambar 5.3 Pencacah Program 4 bit Ketika computer mulai bekerja, pencacah program di-RESET sehingga nilainya menjadi 0000. Nilai ini dikirimkan ke Register Alamat Memori (Memory Address Register, MAR), pada saat fetch, sebagai alamat memori yang akan diambil intruksinya. Kemudian pencacah program menaikan angka cacahnya menjadi 0001. MAR PC PC PC + 1 Setelah intruksi pertama diambil dan dilaksanakan, pencacah program mengirimkan alamat 0001 ke MAR. Pencacah program kembali meningkatkan angka cacahnya. Proses ini terus dilakukan sampai seluruh intruksi dalam memori selesai dijalankan atau menemukan intruksi untuk berhenti, seperti intruksi HLT (HALT). Jalur kendali yang ada pada Pencacah Program : Ep : mengeluarkan nilai dari Pencacah ke dalam W bus. Cp : mengendalikan increment Pencacah : PC PC + 1 b. Masukan dan MAR (Memory Address Register) Di bawah pencacah program adalah Register Masukan dan MAR. Di sini sudah termasuk register saklar untuk alamat dan data. Register-register saklar ini, yang merupakan bagian dari unit masukan memungkinkan pengiriman 4 bit alamat dan 8 bit data kepada memori (Random Access Memory, RAM). Memory Address Register (MAR) adalah bagian dari memori dalam SAP-1. Organisasi dan Arsitektur Komputer - Sejarah Komputer

- 3. LM Masukan & 4 CLK MAR 4 4 Gambar 5.4 Masukan dan MAR (Memory Address Register) Selama komputer bekerja, alamat dalam pencacah program ditahan (latched) pada MAR. Sejenak kemudian MAR mengirmkan alamat 4 bit ke dalam memori RAM, untuk membaca intruksi dalam memori. Jalur kendali yang ada pada Masukan dan MAR : LM : Mengambil data dari W BUS ke dalam MAR c. Memory RAM (Random Access Memory) 16 x 8 RAM berperan sebagai memori utama tempat menyimpan intruksi dan data. Selama komputer beroperasi, RAM menerima alamat 4 bit dari MAR dan operasi membaca dilaksanakan. Setelah memori dibaca, intruksi atau data akan keluar dari memori dan masuk ke dalam bus W. Intruksi atau data yang berada dalam bus W dapat diakses oleh register-register lain. Memori terdiri dari 16 alamat yang lebarnya 8 bit. Untuk mengakses RAM diperlukan alamat 2 dengan lebar Log 16 bit = bit. Itulah mengapa pencacah program lebarnya 4 bit. 4 4 Memori 8 RAM 16 x 8 CE Gambar 5.5 Memori RAM 16 x 8 Jalur kendali yang ada pada RAM : CE : Mengeluarkan data 8 bit dari memori bus W d. Register Intruksi (Instruction Register) Register intruksi merupakan bagian dari unit kendali. Intruksi yang akan dieksekusi, dibaca dari memori utama dan masuk ke dalam W bus. Pada waktu yang bersamaan, register intruksi diaktifkan sehingga intruksi yang dibaca dari memori akan masuk ke dalam register intruksi. Li 8 CLK Register Intruksi CLR 4 Ei 4 Gambar 5.6 Register Intruksi Organisasi dan Arsitektur Komputer - Sejarah Komputer

- 4. Register intruksi dibagi menjadi dua bagian. Bagian atassebanyak 4 bit dikirim ke blok pengendali pengurut (Controller - Sequencer). Bagian bawah sebanyak 4 bit menuju W bus dikendalikan oleh three state buffer. Awal generasi computer ditandai dengan kemampuan computer untuk menyimpan program dalam memori. Sebelumnya, baik computer mekanik atau elektrik, tidak menyimpan program dalam memori computer. Program-program ditulis dalam kartu yang dilubangi kemudian dieksekusi. Bahkan beberapa computer dibuat hanya untuk menyelesaikan satu kasus tertentu. Li : mengambil data 8 bit dari W bus Ei : mengendalikan data 4 bit dari register yang menuju ke W bus e. Pengendali – Pengurut (Controller - Sequencer) Sesuai dengan namanya, register ini berfungsi untuk mengatur seluruh jalannya computer termasuk eksekusi intruksi. Sebelum computer bekerja sinyal CLR dan CLK masing-masing dikimkan ke pencacah program di-Reset ke 0000 dan pada saat yan bersamaan intruksi terakhir dalam register intruksi dihapus. Kemudian sinyal detak CLK ke semua register buffer. Sinyal ini mensinkronkan operasi computer yang menjamin bahwa setiap langkah operasi akan terjadi sebagaimana mestinya. Semua transfer dalam register terjadi pada tepi positif dari sinyal detak CLK yang sama. Data 12 bit yang keluar dari register ini dinamakanmikrointruksi. Mikrointruksi mengendalikan kerja seluruh register. CLK Pengendali CLK Pengurut CLR CLR 12 Cp Ep LM CE Li Ei LA EA Su Eu LB L0 Gambar 5.6 Register Intruksi f. Akumulator Akumulator adalah sebuah register buffer yang menyimpan hasil sementara selama computer beroperasi. Akumulator mempunyai dua macam keluaran. Keluaran dua keadaan secara langsung diteruskan ke bagian penjumlahan-pengurang. Keluaran tiga keadaan dikirimkan ke W bus. Karena itu data sebanyak 8 bit dan akumulator secara terus menerus mengaktifkan rangkaian penjumlah- pengurang. Data yang sama muncul pada W bus jika EA tinggi. LA 8 Akumulator CLK A 8 CLR 8 Gambar 5.7 Register Akumulator A Jalur kendali yang ada pada Register Intruksi : LA : Mengambil data 8 bit bus EA : mengendalikan data 8 bit dari register yang menuju ke W bus Organisasi dan Arsitektur Komputer - Sejarah Komputer

- 5. g. Penjumlah – Pengurang SAP-1 menggunakan sebuah penjumlah – pengurang komplemen-2. Bila SU berharga rendah, maka keluaran jumlah dari penjumlah – pengurang dalam S = A + B. Apabila SU tinggi keluarannya berupa selisih A = A + B’. Rangkaian penjumlah pengurang bersifat asinkron, ini berarti isi keluarannya akan berubah bila terjadi perubahan pada data masukan. Bilamana tinggi, isi yang bersangkutan akan muncul pada W bus. 8 Su Penjumlahan 8 Dan Pengurangan Eu 8 Gambar 5.8 Penjumlah dan Pengurang Jalur kendali yang ada pada Register Intruksi : SU : Menentukan jenis operasi penjumlahan atau pengurangan. Jika SU aktif maka operasi pengurangan, jika sebaliknya, operasi penjumlahan. EU : Mengendalikan data 8 bit dari penjumlahan dan pengurangan yang menuju ke pada W bus. h. Register B Register B adalah register buffer register buffer yang digunakan dalam operasi aritmatika. Sinyal Lb’ yang rendah dan tepi positif dari sinyal detak akan menyalurkan data dari W bus ke tepi positif dari sinyal detak akan menyalurkan data dari W bus ke dalam Register B kemudian mengaktifkan penjumlahan – pengurangan, memasukan bilangan yang akan dijumlahkan dengan atau dikurangkan dari isi akumulator. 8 LB Register 8 B CLK Gambar 5.9 Register B Jalur kendali yang ada pada Register Intruksi : LB : Mengambil data 8 bit dari W bus i. Register Keluaran Pada akhir operasi computer, akumulator berisi hasil operasi yang Lo diselesaikan dalam register penjumlahan – Register 8 Keluaran pengurangan. Setelah, sementara, hasil operasi CLK disimpan dalam akumulator maka selanjutnya dipindahkan ke register keluaran. Apabila EA tinggi dan LO’ rendah tepi positif sinyal detak berikutnya akan memasukkan data dari 8 akumulator ke dalam register keluaran. Gambar 5.11 Register Keluaran Organisasi dan Arsitektur Komputer - Sejarah Komputer

- 6. Register Keluaran sering disebut output port karena data yang telah diproses dapat dikeluarkan dari computer melalui register ini. Dalam mikrokomputer output port dihubungkan dengan rangkaian perantara (interface circuits) yang menggerakan alat-alat seperti printer, monitor dan lain sebagainya. Jalur kendali yang ada pada Register Intruksi : L0 : Mengambil data 8 bit dari W bus j. Peraga Biner Peraga biner adalah suatu alat yang terdiri dari 8 buah LED. Oleh karena setiap LED dihubungkan dengan sebuah flip-flop dari output port, maka peraga biner akan menyajikan isi output port. Dengan demikian setelah kita memindahkan hasil dari bentuk biner pada peraga biner. 5.2 Perangkat Intruksi (Instruction Set) Sebelum dapat memprogram computer, kita harus mempelajari terlebih dahulu perangkat intruksi (instruction set) dari computer yang bersangkutan yaitu operasi-operasi dasar yang dapat dilaksanakan. Intruksi dalam SAP-1 terdiri dari 2 jenis : memiliki 1 operand dan tanpa operand. Operand adalah data atau alamat data yang dioperasikan. Intruksi yang memilik 1 operand adalah : LDA, ADD dan SUB. Intruksi tanpa operand adalah OUT dan HLT. Instruksi Mengacu kepada Memori (Memory Refference Intruction) Instruksi LDA, ADD dan SUB disebut instruksi-instruksi yang mengacu kepada memori, karena semua instruksi yang bersangkuran menggunakan data yang tersimpan dalam memori. Instruksi-instruksi yang terdapat dalam SAP-1 adalah sebagai berikut : LDA Intruksi LDA mengambil data dari memori dan dimasukkan ke dalam (Load The Accumulator) akumulator. Contoh : LDA AH Intruksi ini mengambil data dari alamat memori A H dan disimpan ke dalam akumulator. ADD Intruksi ADD menjumlahkan isi akumulator dengan data memori (Adder) contoh : ADD 8 H Intruksi ini menjumlahkan isi akumulator dengan data memori alamat 8 H. Hasil penjumlahan disimpan kembali dalam akumulator/ Berilut ini contoh operasi ADD yang didahului intruksi LDA. Misal isi alamat AH = 00000011, dan 8 H = 00000001 LDA AH : A = 00000011 ADD 8 H : A = A + 00000001 = 00000011 + 00000001 = 00000100 Selama pelaksanaan instruksi ADD 8 H akan berlangsung operasi sebagai berikut. Pertama isi memori alamat DH = 00000001 akan ditransfer ke dalam register B sehingga : B = 00000001 Pada waktu bersamaan register Penjumlah – Pengurang melakukan penjumlahan dari register A dan B, menghasilkan jumlah A = 00000100 Kemudian Hasil Jumlah ini diisikan ke dalam akumulator sehingga A = 00000100 SUB Intruksi SUB mengurangkan isi akumulator dengan isi register B. Contoh : (Subtract) SUB DH Intruksi ini akan mengurangkan isi akukulator dengan data pada alamat DH. Hasilnya disimpan kembali ke dalam akumulatar. Prosesnya mirip dengan intruksi ADD. Misalnya isi memori AH = 00000101 dan 5 H = 00000010 Organisasi dan Arsitektur Komputer - Sejarah Komputer

- 7. LDA AH : A = 00000101 SUB DH : A = A - 00000010 = 00000101 + 00000010 = 00000011 Isi alamat memori alamat DH diambil dan dimasukan ke dalam register B. Kemudian dilakukan proses pengurangan dan hasilna disimpan kembali di register A.. OUT Instruksi OUT adalah instruksi tanpa operand. Data dari akumulator secara otomatis akan diambil dan dimasukkan ke dalam register keluaran. HLT Instruksi HLT berfungsi untuk menghentikan proses. Instruksi ini (HALT) memberitahu kepada computer untuk berhenti memproses data. HLT menandai akhir suatu program. Intruksi ini tidak memerlukan operand memori. Setiap program dalam SAP-1 harus diakhiri dengan HLT. Tabel 5.1 Rangkuman Instruksi SAP-1 MNEMONIK OPERASI LDA Mengisikan data memori ke dalam Akumulator (Load The Accumulator) ADD Menambahkan akumulator dengan data memori (Adder) SUB Mengurangkan akumulator dengan data memori (Subtract) OUT Mengeluarkan isi akumulator HLT Menghentikan program (HALT) 5.3 Pemograman SAP 1 Di dalam pemrograman SAP-1 terdapat kode yang akan memerintahkan computer untuk melakukan suatu operasi yang disebut dengan kode operasi (operation code) yang disingkat dengan opcode. Beirkut kode operasi dari tiap intruksi pada SAP-1 Tabel 5.2 Kode Operasi SAP-1 MNEMONIK KODE OPERASI LDA 0000 ADD 0001 SUB 0010 OUT 1110 HLT 1111 Siklus Intruksi Dalam menyelesaikan setiap intruksi diperlukan tahapan. Tahapan ini disebut siklus intruksi. Siklus intruksi terdiri dari 2 tahap yaitu FETCH dan EXECUTE. Masing-masing tahap memerlukan 3 siklus detak (clock cycle) ditandai dengan T1, T2, T3, T4, T5 dan T6. Siklus detak ini diatur oleh pencacah yang disebut Ring Counter yang mengeluarkan nilai T : T = T6 T5 T4 T3 T2 T1, Pada saat computer mulai dijalankan, data keluaran pencacah tersebut adalah : T = 000001 diselesaikan dalam 6 keadaan T tersebut. Penjelasan rinci masing-masing tahap sebagai berikut : a. Siklus Fetch Pada siklus fetch dilakukan pengambilan intruksi dari memori dan diletakan di dalam register instruksi. Semua instruksi melalui tahap ini. Tiga hal yang dilakukan pada tahap ini : 1) Mengirim isi Pencacah Program (Program Counter) ke dalam register pengalamatan (MAR) 2) Menambah nilai Pencacah Program dengan 1. (increment State) Organisasi dan Arsitektur Komputer - Sejarah Komputer

- 8. 3) Mengambil intruksi dari memori dan dimasukan ke dalam register intruksi. (Memory State) T1 T2 T3 T4 T5 T6 T7 T1 T2 T3 T4 T5 T6 Gambar 5.12 Ring Countrer Digram Waktu Pencacah CLK Ring CLR T1 T2 T3 T4 T5 T6 Gambar 5.13 Simbol Ring Countrer Organisasi dan Arsitektur Komputer - Sejarah Komputer

- 9. Tahap Pengiriman Alamat (Address State) – T1 Pada tahap ini nilai dari Pencacah Program (Program Counter) dikirim ke register alamat memori (MAR). Pengendali atau Pengurut akam mengirim nilai kendali CON : CON = Cp Ep LM CE Li Ei LA EA Su Eu LB L0 CON = 0 1 0 1 1 1 1 0 0 0 1 1 Jalur yang aktif ada dua EP = 1 aktif High dan LM = 0 aktif Low Cp W CLK Pencacah Program 8 4 CLR ( Program Counter ) Ep LM Masukan & 4 MAR CLK 4 4 Gambar 5.14 Aliran Data dari Pencacah ke MAR Data dari 4 bit akan keluar dari Pencacah Program menuju W bus, bersamaan dengan itu, data dari W bus akan diambil ke dalam Masukan dan MAR. Akhir tahap ini, 4 bit alamat sudah berada dalam MAR, menunjuk ke memori RAM. Tahap Penambahan Nilai Pencacah dengan 1 (Increment State) – T2 Pada tahap ini Pencacah Program ditambahkan dengan 1 Pengendali/Pengurut akan mengirim nilai kendali CON : CON = Cp Ep LM CE Li Ei LA EA Su Eu LB L0 CON = 1 0 0 1 1 1 1 0 0 0 1 1 Jalur yang aktif Cp = 1. Nilai Pencacah ditambah 1 Tahap Pengambilan Intruksi dari Memori (Memory State) – T3 Pada tahap ini data pada memori RAM yang ditunjuk oleh MAR dikeluarkan menuju bus. Sementara itu data dari W bus masuk ke dalam register intruksi. Pengendali/pengurut akan mengirim nilai kendali CON : CON = Cp Ep LM CE Li Ei LA EA Su Eu LB L0 CON = 0 0 1 0 0 1 1 0 0 0 1 1 Jalur yang aktif CE dan Li = 0, Keduanya aktif low Organisasi dan Arsitektur Komputer - Sejarah Komputer

- 10. W Memori 8 8 RAM 16 x 8 CE Li 8 CLK Register Intruksi CLR 4 Ei 4 Gambar 5.15 Aliran Data dari Me kemori ke Register Instruksi Data 8 bit akan keluar dari memori RAM menuju W bus, bersamaan dengan itu, data W bus akan diambil ke dalam Register Instruksi. Akhir tahap ini, 8 bit instruksi sudah berada dalam Register Instruksi. Siklus Fetch Keseluruhan Tahap Pengamalamatan (Address State), penambahan nilai pencacah (increment state) dan pengambilan instruksi dari memori (memory state) disebut juga dengan siklus fetch. Berikut ini adalah gambar komponen-komponen yang aktif (warna abu-abu) pada setiap tahapan T1, T2 dan T3 : Cp LA Cp LA W 8 W 8 CLK Pencacah Program CLK CLK Pencacah Program CLK 8 Akumulator 8 Akumulator 4 4 CLR Program Counter A CLR Program Counter A Ep 8 Ep 8 CLR CLR 8 8 Su Su LM Masukan LM Masukan dan 4 Penjumlahan dan 4 Penjumlahan MAR 8 Dan MAR 8 Dan CLK CLK Pengurangan Pengurangan Eu Eu 8 8 4 4 4 4 Memori LB Memori LB 8 Register 8 Register RAM 16 x 8 8 RAM 16 x 8 8 B B CLK CLK CE CE Li Li 8 Lo 8 Lo CLK Register CLK Register Register Intruksi 8 Keluaran Register Intruksi 8 Keluaran CLR CLK CLR CLK 4 4 Ei Ei 4 8 4 8 CLK CLK Pengendali CLK Peraga Pengendali CLK Peraga Pengurut Biner Pengurut CLR Biner CLR CLR CLR 4 12 4 12 Cp Ep L CE Li E i L A EA S u Eu L B L0 M Cp Ep L CE Li E i L A EA S u Eu L B L0 M Gambar 5.16 Tahapan Siklus Fetch Tahap T1 Gambar 5.17 Tahapan Siklus Fetch Tahap T2 Organisasi dan Arsitektur Komputer - Sejarah Komputer

- 11. Cp LA W 8 CLK Pencacah Program CLK 8 Akumulator 44 CLR Program Counter A Ep 8 CLR 8 Su LM Masukan dan 4 Penjumlahan MAR 8 Dan CLK Pengurangan Eu 8 4 4 Memori LB Register RAM 16 x 8 84 8 B CLK CE Li 8 Lo CLK Register Register Intruksi 8 Keluaran CLR CLK 4 Ei 4 8 CLK Pengendali CLK Peraga Pengurut CLR Biner CLR 4 12 Cp Ep L CE Li E i L A EA S u Eu L B L0 M Gambar 5.18 Tahapan Siklus Fetch Tahap T3 Semua instruksi diawali oleh siklus fetch dengan tahapan yang sama. Perbedaan satu instruksi dengan yang lainnya terletak pada tahap eksekusi. b. Siklus Eksekusi Eksekusi instruksi dikendalikan oleh Pengendali/Pengurut (Controller/Sequencer). Masing- masing tahap eksekusi T4, T5 dan T6 berbeda-beda untuk setiap instruksi. Organisasi dan Arsitektur Komputer - Sejarah Komputer

- 12. Instruksi LDA Pada instruksi LDA hanya T4 dan T5 yang aktif, sementara tahap T6 tidak ada yang aktif. Tahapan pada instruksi LDA : Pada tahap T4 alamat memori dikirim dari register instruksi ke MAR Pada tahap T5 data dari memori diambil dari register instruksi ke akumulator Pada tahap T6 tidak melakukan apa-apa. Tahap Pengiriman Alamat – T4 Pada tahap ini nilai 4 bit operand dari register instruksi masuk ke MAR. Pengendali/Pengurut akan mengirim nilai kendali CON : CON = Cp Ep LM CE Li Ei LA EA Su Eu LB L0 CON = 0 0 0 1 0 0 1 0 0 0 1 1 Jalur yang aktif CE dan Li = 0, Keduanya aktif low W LM 8 Masukan & 4 MAR CLK 4 4 Li 8 CLK Register Intruksi CLR 4 Ei 4 Gambar 5.19 Tahapan Siklus Fetch Tahap T3 Data 4 bit keluar dari register instruksi menuju W bus, bersamaan dengan itu, data dari W bus akan diambil ke dalam MAR. Akhir tahap ini, 4 bit instruksi sudah berada dalam MAR menunjuk ke alamat memori RAM. Tahap Pengambilan Data – T5 Pada tahap ini data 8 bit dari memori diambil dan dimasukan ke dalam akumulator. Pengendali/Pengurut akan mengirim nilai kendali CON : CON = Cp Ep LM CE Li Ei LA EA Su Eu LB L0 CON = 0 0 1 0 1 1 0 0 0 0 1 1 Jalur yang aktif CE dan LA = 0, Keduanya aktif low Organisasi dan Arsitektur Komputer - Sejarah Komputer

- 13. LA W 8 Akumulator CLK 8 A 8 CLR 8 Memori RAM 16 x 8 8 CE Gambar 5.20 Aliran Data dari Memori ke Akumulator A Data 8 bit dari register instruksi menuju W bus, bersamaan dengan itu, data dari W bus akan diambil ke dalam akumulator. Akhir tahap ini, 8 bit data masuk ke akumulator. Siklus Instruksi LDA Keseluruhan Berikut ini adalah gambar komponen-komponen yang aktif (warna abu-abu) pada tahap T4 dan T5 instruksi LDA : Cp LA Cp W 8 W 8 CLK Pencacah Program CLK CLK Pencacah Program 8 Akumulator 8 Akumulator 4 4 CLR (Program Counter) A CLR (Program Counter) A Ep 8 Ep 8 CLR 8 8 Su LM LM Masukan & Penjumlahan Masukan & Penjumlahan 4 4 MAR 8 Dan MAR 8 Dan CLK CLK Pengurangan Pengurangan Eu 8 8 4 4 4 4 Memori LB Memori 8 Register 8 Register RAM 16 x 8 8 RAM 16 x 8 8 B B CLK CE CE Li Li 8 Lo 8 CLK Register CLK Register Register Intruksi 8 Register Intruksi 8 Keluaran CLR Keluaran CLR CLK 4 4 Ei Ei 4 8 4 8 CLK CLK CLK Pengendali CLK Pengendali Peraga Peraga Pengurut CLR Biner Pengurut CLR Biner CLR CLR 12 12 CON = Cp Ep LM CE Li Ei LA EA Su Eu LB L0 CON = Cp Ep LM CE Li Ei LA EA Su Eu LB L0 (a) Tahap T5 (b) Tahap T6 Gambar 5.21 Tahap T5 dan T6 Pada Siklus Eksekusi LDA Organisasi dan Arsitektur Komputer - Sejarah Komputer

- 14. Instruksi ADD dan SUB Pada Instruksi ADD dan SUB data operand diambil dari memori dan dijumlahkan dengan akumulator hasilnya disimpan kembali ke dalam akumulator. Tahapan pada Instruksi ADD dan SUB : Pada tahap T4 alamat memori dikirim dari memori dikirim ke register instruksi ke MAR Pada tahap T5 data dari memori diambil dan masuk ke register B Pada tahap T6 data dari register B dioperasikan dengan akumulator dan hasilnya disimpan dalam akumulator. Perbedaan instruksi ADD dan SUB pada tahap 6. Tahap Pengiriman Alamat – T4 Pada tahap ini sama persis dengan instruksi LDA. Nilai alamat 4 bit dari register instruksi masuk ke dalam register alamat memori (MAR). Tahap Pengambilan Data – T5 Pada tahap ini data 8 bit dari memori diambil dan dimasukan ke dalam register B. Pengendali/Pengurut akan mengirim nilai kendali CON : CON = Cp Ep LM CE Li Ei LA EA Su Eu LB L0 CON = 0 0 1 0 1 1 1 0 0 0 0 1 Jalur yang aktif CE dan LA = 0, Keduanya aktif low 8 W 8 LB Memori Register 8 8 RAM 16 x 8 B CLK CE Gambar 5.22 Aliran Data dari Memori ke Register B Data 8 bit dari memori menuju W bus, bersamaan dengan itu, data dari W bus akan diambil ke dalam register B. Akhir tahap ini, 8 bit data masuk ke register B. Tahap Pengambilan Data – T6 Pada tahap ini data 8 bit dari akumulator dan register B dioperasikan (ADD/SUB) hasilnya disimpan dalam akumulator. Pengendali/Pengurut akan mengirim nilai kendali CON : Operasi ADD CON = Cp Ep LM CE Li Ei LA EA Su Eu LB L0 CON = 0 0 1 1 1 1 0 0 0 1 1 1 Jalur yang aktif Eu = 1 aktif high dan LA = 0, Keduanya aktif low Operasi SUB CON = Cp Ep LM CE Li Ei LA EA Su Eu LB L0 CON = 0 0 1 0 1 1 1 0 0 0 0 1 Jalur yang aktif Su , Eu aktif high dan LA = 0, Keduanya aktif low Organisasi dan Arsitektur Komputer - Sejarah Komputer

- 15. LA W 8 Akumulator CLK 8 A 8 CLR 8 Su Penjumlahan 8 Dan Pengurangan Eu 8 LB Register 8 B CLK Gambar 5.22 Aliran Data dari Memori ke Register B Data 8 bit dari register B dan akumulator dioperasikan (ADD/SUB) dan hasilnya disimpan kembali ke akumulator lewat W bus. Siklus Instruksi ADD/SUB Keseluruhan Berikut ini adalah gambar komponen-komponen yang aktif (warna abu-abu) pada tahap T4 dan T5 instruksi ADD/SUB : Cp LA Cp LA W 8 W 8 CLK Pencacah Program CLK CLK Pencacah Program CLK 8 Akumulator 8 Akumulator 44 44 CLR Program Counter A CLR Program Counter A Ep 8 Ep 8 CLR CLR 8 8 Su Su LM Masukan LM Masukan dan 4 Penjumlahan dan 4 Penjumlahan MAR 8 Dan MAR 8 Dan CLK CLK Pengurangan Pengurangan Eu Eu 8 8 4 4 4 4 Memori LB Memori LB Register Register RAM 16 x 8 84 8 RAM 16 x 8 84 8 B B CLK CLK CE CE Li Li 8 Lo 8 Lo CLK Register CLK Register Register Intruksi 8 Keluaran Register Intruksi 8 Keluaran CLR CLK CLR CLK 4 4 Ei Ei 4 8 4 8 CLK CLK Pengendali CLK Peraga Pengendali CLK Peraga Pengurut CLR Biner Pengurut CLR Biner CLR CLR 4 12 4 12 Cp Ep L CE Li E i L A EA S u Eu L B L0 M Cp Ep L CE Li E i L A EA S u Eu L B L0 M (a) Tahap T5 (b) Tahap T6 Gambar 5.21 Tahap T5 dan T6 Pada Instruksi ADD/SUB Organisasi dan Arsitektur Komputer - Sejarah Komputer

- 16. Instruksi OUT Instruksi OUT memerlukan satu tahap T4 yaitu memindahkan data dari akumulator ke dalam register keluaran. Pengendali/Pengurut akan mengirim nilai kendali CON : CON = Cp Ep LM CE Li Ei LA EA Su Eu LB L0 CON = 0 0 1 1 1 1 1 1 0 0 1 1 Jalur yang aktif EA = 1 aktif high dan LB = 0, Keduanya aktif low LA W 8 Akumulator CLK 8 A CLR Lo Register 8 Keluaran CLK 8 Gambar 5.22 Aliran Data dari Akumulator A ke Register Keluaran Siklus Instruksi ADD/SUB Keseluruhan Cp LA W 8 CLK Pencacah Program CLK 8 Akumulator 4 CLR (Program Counter) A Ep 8 CLR 8 Su LM Masukan & Penjumlahan 4 MAR 8 Dan CLK Pengurangan Eu 8 4 4 Memori LB 8 Register RAM 16 x 8 8 B CLK CE Li 8 Lo CLK Register Register Intruksi 8 CLR Keluaran CLK 4 Ei 4 8 CLK Pengendali CLK Peraga Pengurut CLR Biner CLR 12 CON = Cp Ep LM CE Li Ei LA EA Su Eu LB L0 Gambar 5.23 Tahap T4 Siklus Instruksi Out Organisasi dan Arsitektur Komputer - Sejarah Komputer

- 17. 5.4 Pengendali/Pengurut (Controller/Sequence) SAP-1 Bagian terpenting dalam SAP-1 adalah Register Pengendali/Pengurut. Pada computer modern bagian ini adalah unit kendali (control unit) yang berfungsi mengatur seluruh jalannya komponen. Pada setiap tahap atau siklus tidak semua komponen aktif. Semuanya ditentukan oleh keluaran dari bagian Pengendali/Pengurut ini. Keluran kendali lebarnya 12 bit, yang masing-masing bit-nya mengengedalikan seluruh register dalam SAP-1. Setiap tahap dari T1 sampai T6, pengendali mengeluarkan sinyal kendali sebanyak 6 buah. Sinyal kendali yang keluar dari Pengendali/Pengurut dinamakan mikro instruksi. Li 8 CLK Register Intruksi CLR 4 Ei 4 CLK Pengendali CLK Pengurut CLR CLR 4 12 Cp Ep L CE Li E i L A EA S u Eu L B L0 M Gambar 5.24 Tahap T4 Siklus Instruksi Out Di antara ke 12 jalur kendali terdapat jalur yang aktif high dan ada juga yang aktif low. Jalur yang aktif low ditandai dengan gari di atas nama jalurnya, jalur tersebut akan aktif jika nilainya = 0. Sementara jalur yang aktif high akan aktif jika nilainya = 1. Keluaran register Pengendali/Pengurut tergantung 4 bit kode operasi (opcode) dari register instruksi. Setiap instruksi memiliki kode operasi yang berbeda-beda, seperti yang telah dijelaskan sebelumnya. Lebih jauh lagi bagaimanakah kode operasi diproses oleh Pengendali/Pengurut sehingga menghasilkan 12 bit mikro instruksi. Kita bisa bisa perhatikan lebih detail lagi Register Intruksi ROM Alamat 16 x 4 T3 Pencacah CLK Presettable T3 || CLR ROM Kendali 16 x 12 Cp Ep L CE Li E i L A EA S u Eu L B M Gambar 5.25 Komponen dalam Pengendali/Pengurut Organisasi dan Arsitektur Komputer - Sejarah Komputer

- 18. Komponen yang terdapat dalam Pengendali/Pengurut adalah : ROM Alamat 16 x 4 Tabel 5.3 Isi ROM Alamat ALAMAT DATA INSTRUKSI 0000 0011 LDA 0001 0110 ADD 0010 1001 SUB 0011 XXXX NONE 0100 XXXX NONE 0101 XXXX NONE 0110 XXXX NONE 0111 XXXX NONE 1000 XXXX NONE 1001 XXXX NONE 1010 XXXX NONE 1011 XXXX NONE 1100 XXXX NONE 1101 XXXX NONE 1110 XXXX OUT 1111 1100 NONE Pencacah Presettable Pencacah Presettable akan mencacah dari 0000 sampai dengan 0011. Selanjutnya tergantung dari kode operasi yang masuk dari ROM Alamat. Jika instruksinya LDA maka nilai pencacah berikutnya adalah 0011, jika instruksinya OUT maka nilai pencacahnya berikutnya 1100. ROM Kendali 16 x 12 Tabel 5.4 Isi ROM Kendali Organisasi dan Arsitektur Komputer - Sejarah Komputer

- 19. Mikro Instruksi adalah isi ROM kendali 16 12 yang lebarnya 12 bit. Makro Instruksi adalah instruksi dalam bahasa assembl seperti LDA, ADD, SUB, dab OUT sering juga disebut Mnemonik, Secara singkat insruksi SAP-1 : Tabel 5.5 Mnemonik SAP-1 MNEMONIK OPERASI LDA Memasukan data RAM ke Akumulator ADD Menambahkan data RAM ke Akumulator SUB Mengurangkan data RAM ke Akumulator OUT Memasukan data Akumulator ke register Keluaran HLT Menghentikan program Mikroprgram adalah program yang disimpan dalam ROM kendali. Isi (CON) merupakan mikroprogram yang secara permanen disimpan dalam ROM kendali. Organisasi dan Arsitektur Komputer - Sejarah Komputer