Contenido electiva 1 dsp

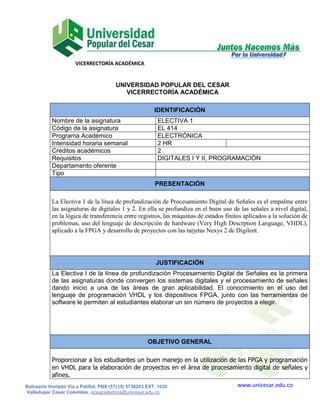

- 1. VICERRECTORÍA ACADÉMICA UNIVERSIDAD POPULAR DEL CESAR VICERRECTORÍA ACADÉMICA IDENTIFICACIÓN Nombre de la asignatura ELECTIVA 1 Código de la asignatura EL 414 Programa Académico ELECTRÓNICA Intensidad horaria semanal 2 HR Créditos académicos 2 Requisitos DIGITALES I Y II, PROGRAMACIÓN Departamento oferente Tipo PRESENTACIÓN La Electiva 1 de la línea de profundización de Procesamiento Digital de Señales es el empalme entre las asignaturas de digitales 1 y 2. En ella se profundiza en el buen uso de las señales a nivel digital, en la lógica de transferencia entre registros, las máquinas de estados finitos aplicados a la solución de problemas, uso del lenguaje de descripción de hardware (Very High Descrption Language, VHDL), aplicado a la FPGA y desarrollo de proyectos con las tarjetas Nexys 2 de Digilent. JUSTIFICACIÓN La Electiva I de la línea de profundización Procesamiento Digital de Señales es la primera de las asignaturas donde convergen los sistemas digitales y el procesamiento de señales dando inicio a una de las áreas de gran aplicabilidad. El conocimiento en el uso del lenguaje de programación VHDL y los dispositivos FPGA, junto con las herramientas de software le permiten al estudiantes elaborar un sin número de proyectos a elegir. OBJETIVO GENERAL Proporcionar a los estudiantes un buen manejo en la utilización de las FPGA y programación en VHDL para la elaboración de proyectos en el área de procesamiento digital de señales y afines. Balneario Hurtado Vía a Patillal. PBX (57) (5) 5736203 EXT. 1020 www.unicesar.edu.co Valledupar Cesar Colombia. viceacademica@unicesar.edu.co

- 2. VICERRECTORÍA ACADÉMICA OBJETIVOS ESPECÍFICOS Programar técnicamente en VHDL Utilizar adecuadamente la tarjeta Nexys 2 de Digilent Diseñar y presentar un proyecto final con la FPGA COMPETENCIAS GENERALES El estudiante al finalizar el curso, analiza situaciones reales y diseña una solución utilizando la FGPA. Programa en VHDL y muestra y expone su trabajo ESTRATEGIAS METODOLÓGICAS Se emplean dos estrategias metodológicas, la primera parte son Clase tipo exposición con participación de los estudiantes y la segunda es el aprendizaje basado en proyecto principalmente CONTENIDO 1. Introducción al las Electivas de Procesamiento Digital de Señales 1.1. Objetivos 1.2. Alcance, logros 1.3. Metodología 1.4. Bibliografía 2. Lógica secuencial síncrona 2.1. Circuitos secuenciales 2.2. Latches, flip-flops 2.3. Análisis de de circuitos secuenciales temporizados 2.4. Diagrama de estado 2.5. Tablas de estado 2.6. Asignación y reducción de estados 3. Registros y contadores 3.1. Registros de desplazamiento 3.2. Registro de desplazamiento universal 3.3. Contadores 4. Memorias 4.1. Tipos de memoria Balneario Hurtado Vía a Patillal. PBX (57) (5) 5736203 EXT. 1020 www.unicesar.edu.co Valledupar Cesar Colombia. viceacademica@unicesar.edu.co

- 3. VICERRECTORÍA ACADÉMICA 4.2. Constitución de una memoria de acceso aleatorio 4.3. Arreglos de memorias, extensión de la capacidad, y de la palabra. 5. Diseño a nivel de transferencia de registros 5.1. Notación RTL 5.2. Máquinas de estado algorítmico (ASM) 5.3. Multiplicador binario secuencial 5.4. Lógica de control 5.5. Diseño con multiplexores 5.6. Diseño libre de carreras 5.7. Diseño libre de latches 6. Máquinas de estado finito 6.1. Máquina de Mealy 6.2. Máquina de Moore 6.3. Ejemplo de diseño 7. Metodología de diseño 7.1. Conceptos de herramientas CAD-EDA 7.2. Diseño Bottom-Up 7.3. Diseño Top-Down 7.4. Ventajas del diseño Top-Down 7.5. Ingeniería concurrente 8. Introducción al lenguaje VHDL 8.1. El lenguaje VHDL 8.2. VHDL describe estructura y comportamiento 8.3. Ejemplo básico de descripción VHDL 8.4. Presentación del proyecto final 9. Elementos sintácticos del VHDL 9.1. Operadores y expresiones 9.2. Tipos de datos 9.3. Tipos escalares 9.4. Tipos compuestos 9.5. Subtipos de datos 9.6. Atributos 9.7. Declaración de constantes, variables y señales 9.8. Declaración de entidad y arquitectura 9.9. Desarrollo de ejercicios en programación VHDL 10. Ejecución concurrente 10.1. Ejecución concurrente y ejecución serie 10.2. Descripción comportamental RTL 10.3. Estructuras de la ejecución concurrente RTL 11. Descripción serie comportamental abstracta 11.1. Diferencias entre variable y señal 11.2. Estructuras de la ejecución serie Balneario Hurtado Vía a Patillal. PBX (57) (5) 5736203 EXT. 1020 www.unicesar.edu.co Valledupar Cesar Colombia. viceacademica@unicesar.edu.co

- 4. VICERRECTORÍA ACADÉMICA 11.3. Desarrollo de ejercicios en programación VHDL 12. Subprogramas, paquetes y bibliotecas 12.1. Subprogramas 12.2. Declaración de procedimientos y funciones 12.3. Llamadas a subprogramas 12.4. Sobrecarga de operadores 12.5. Bibliotecas, paquetes y unidades 12.6. Paquetes: PACKAGE y PACKAGE BODY 12.7. Configuración: CONFIGURATION 12.8. Desarrollo de ejercicios en programación VHDL 13. VHDL para simulación 13.1. Los retrasos y la simulación 13.2. Retrasos inerciales y transportados 13.3. Descripción de un banco de pruebas 13.4. Notificación de sucesos 13.5. Procesos pasivos 13.6. Desarrollo de ejercicios en programación VHDL 14. VHDL para síntesis 14.1. Restricciones en la descripción 14.2. Construcciones básicas 14.3. Descripción de lógica combinacional 14.4. Descripción de lógica secuencial 14.5. Desarrollo de ejercicios en programación VHDL 15. Conceptos avanzados en VHDL 15.1. Buses y resolución de señales [1] 15.2. Descripción de maquinas de estados [1] 15.3. Desarrollo de ejercicios en programación VHDL EVALUACIÓN PRIMER CORTE (30%) SEGUNDO CORTE (30%) TERCER CORTE (40%) Parcial 1 12% Diapositivas 7% Talleres ó Exposición Presentación Feria de la 18% Electrónica 8% Entrega de programas Entrega de proyecto (Hardware elaborados en VHDL + Software) 25% REFERENCIAS BIBLIOGRÁFICAS - Lecturas Obligatorias. [1] M. Morris Mano y M. D. Ciletti, Digital Design, Fourth ed., Pearson, Prentice Hall. Balneario Hurtado Vía a Patillal. PBX (57) (5) 5736203 EXT. 1020 www.unicesar.edu.co Valledupar Cesar Colombia. viceacademica@unicesar.edu.co

- 5. VICERRECTORÍA ACADÉMICA [6] R. J. Tocci y N. S. Widmer, Sistemas Digitales Principios y aplicaciones, Sexta ed., Pearson Educacioón, 1996. [7] F. Pardo Carpio, «VHDL Lenguaje para descripción y modelado de circuitos,» Universidad de Valencia, 1997. - Lecturas Complementarias. [2] P. P. Chu, FPGA Prototyping by examples. Xilinx spartan-3 version, Hoboken, New Jersey: Wiley-Interscience, 2008. [4] D. L. Perry, Vhd: programming by example, Fourth ed., McGraw-Hill, 2002. - Lecturas Sugeridas. [3] P. J. Ashenden y J. Lewis, The designer's guide to vhdl, Third ed., Morgan Kaufmann Publisher, 2008. [5] S. Hauck y A. DeHon, Reconfigurable Computing. The theory and practice of FPGA-based computation, Elsevier, 2008. La Universidad cuenta con las siguientes bases de datos: PROQUEST, EBRARY, E-LIBRO, SAFARI, JURIVERSIA, LEGIS, AMBIENTALEX.INFO Balneario Hurtado Vía a Patillal. PBX (57) (5) 5736203 EXT. 1020 www.unicesar.edu.co Valledupar Cesar Colombia. viceacademica@unicesar.edu.co