Lab-Tools FPGA Modules for Digital NMR Instrumentation

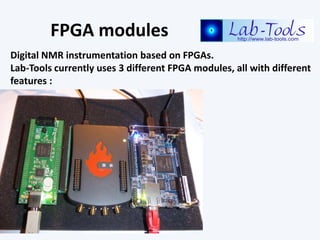

- 1. FPGA modules Digital NMR instrumentation based on FPGAs. Lab-Tools currently uses 3 different FPGA modules, all with different features :

- 2. FPGA modules Digital NMR instrumentation based on FPGAs. Lab-Tools currently uses 3 different FPGA modules : 1) FTDI Morphic II module with an Altera Cyclone II FPGA : USB2 bus interfaced to array processing language AplX , which is used for the configuration, control, data processing and GUI front-panel.

- 3. FPGA modules Digital NMR instrumentation based on FPGAs. Lab-Tools currently uses 3 different FPGA modules : 1) FTDI Morphic II module with an Altera Cyclone II FPGA : USB2 interfaced to array processing language AplX , used for the configuration, control, data processing and GUI front-panel. Mate with Lab-Tools Cardstac headers for adding a variety of instruments.

- 4. FPGA modules Digital NMR instrumentation based on FPGAs. Lab-Tools currently uses 3 different FPGA modules : 1) FTDI Morphic II module with an Altera Cyclone II FPGA : USB2 interfaced to array processing language AplX , used for the configuration, control, data processing and GUI front-panel. Here it is mated with a Lab-Tools Cardstac header for adding a variety of instruments.

- 5. FPGA modules Digital NMR instrumentation based on FPGAs. Lab-Tools currently uses 3 different FPGA modules : 2) Red Pitaya module with Xilinx FPGA with Linux ARM CPU : Has on board dual RF 14 bit 125MHz ADCs & DACs. Ethernet interface plus array processing language AplX server in the Linux CPU, talking to desktop for the configuration, control, data processing and GUI front-panel.

- 6. FPGA modules Digital NMR instrumentation based on FPGAs. Lab-Tools currently uses 3 different FPGA modules : 3) Terasic DE0-Nano-SoC module with Cyclone V FPGA with Linux ARM CPU : Ethernet interface plus array processing language AplX server in the Linux CPU, talking to desktop for the configuration, control, data processing and GUI front-panel. Mates with Lab-Tools Cardstac headers; Accepts same firmware as Morphic II.

- 7. Modular Firmware Skeleton For Multiple Instruments Inside a Single FPGA. AplX array-processing software from MicroApl creates and manages the on-screen GUI front-panel to control ; also controls the firmware instruments in the FPGAs over the USB2 bus. AplX then analyses the returned data. USB2 interfaced Morphic II Module with Cyclone II FPGA

- 8. Modular Firmware Skeleton For Multiple Instruments Inside a Single FPGA. An AplX server in the ARM processor controls and monitors the instruments in the FPGA via C programs and Xilinx firmware. An AplX client on the desktop then creates and manages the on-screen GUI and stores analysed data. Ethernet interfaced Red Pitaya module with Xilinx FPGA

- 9. Modular Firmware Skeleton For Multiple Instruments Inside a Single FPGA. An AplX server in the ARM processor controls and monitors the instruments in the FPGA via user programmable interfaces. An AplX client on the desktop then creates and manages the on-screen GUI and stores analysed data. Ethernet interfaced DE0-Nano-SoC module with CycloneV FPGA