Unidad 1 arquitectura

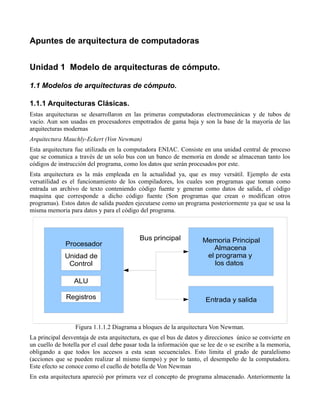

- 1. Apuntes de arquitectura de computadoras Unidad 1 Modelo de arquitecturas de cómputo. 1.1 Modelos de arquitecturas de cómputo. 1.1.1 Arquitecturas Clásicas. Estas arquitecturas se desarrollaron en las primeras computadoras electromecánicas y de tubos de vacío. Aun son usadas en procesadores empotrados de gama baja y son la base de la mayoría de las arquitecturas modernas Arquitectura Mauchly-Eckert (Von Newman) Esta arquitectura fue utilizada en la computadora ENIAC. Consiste en una unidad central de proceso que se comunica a través de un solo bus con un banco de memoria en donde se almacenan tanto los códigos de instrucción del programa, como los datos que serán procesados por este. Esta arquitectura es la más empleada en la actualidad ya, que es muy versátil. Ejemplo de esta versatilidad es el funcionamiento de los compiladores, los cuales son programas que toman como entrada un archivo de texto conteniendo código fuente y generan como datos de salida, el código maquina que corresponde a dicho código fuente (Son programas que crean o modifican otros programas). Estos datos de salida pueden ejecutarse como un programa posteriormente ya que se usa la misma memoria para datos y para el código del programa. Bus principal Memoria Principal Procesador Almacena Unidad de el programa y Control los datos ALU Registros Entrada y salida Figura 1.1.1.2 Diagrama a bloques de la arquitectura Von Newman. La principal desventaja de esta arquitectura, es que el bus de datos y direcciones único se convierte en un cuello de botella por el cual debe pasar toda la información que se lee de o se escribe a la memoria, obligando a que todos los accesos a esta sean secuenciales. Esto limita el grado de paralelismo (acciones que se pueden realizar al mismo tiempo) y por lo tanto, el desempeño de la computadora. Este efecto se conoce como el cuello de botella de Von Newman En esta arquitectura apareció por primera vez el concepto de programa almacenado. Anteriormente la

- 2. secuencia de las operaciones era dictada por el alambrado de la unidad de control, e cambiarla implicaba un proceso de recableado laborioso, lento(hasta tres semanas) y propenso a errores. En esta arquitectura se asigna un código numérico a cada instrucción. Dichos códigos se almacenan en la misma unidad de memoria que los datos que van a procesarse, para ser ejecutados en el orden en que se encuentran almacenados en memoria. Esto permite cambiar rápidamente la aplicación de la computadora y dio origen a las computadoras de propósito general Mas a detalle, el procesador se subdivide en una unidad de control (C.U.), una unidad lógica aritmética (A.L.U.) y una serie de registros. Los registros sirven para almacenar internamente datos y estado del procesador. La unidad aritmética lógica proporciona la capacidad de realizar operaciones aritméticas y lógicas. La unidad de control genera las señales de control para leer el código de las instrucciones, decodificarlas y hacer que la ALU las ejecute. Arquitectura Harvard Esta arquitectura surgió en la universidad del mismo nombre, poco después de que la arquitectura Von Newman apareciera en la universidad de Princeton. Al igual que en la arquitectura Von Newman, el programa se almacena como un código numérico en la memoria, pero no en el mismo espacio de memoria ni en el mismo formato que los datos. Por ejemplo, se pueden almacenar las instrucciones en doce bits en la memoria de programa, mientras los datos de almacenan en 8 bits en una memoria aparte. Bus de Bus de programa Procesador datos Memoria de datos Unidad de Memoria de Control programa ALU Registros Entrada y salida Figura 1.1.1.2 Diagrama a bloques de la arquitectura Harvard El hecho de tener un bus separado para el programa y otro para los datos permite que se lea el código de operación de una instrucción, al mismo tiempo se lee de la memoria de datos los operados de la instrucción previa. Así se evita el problema del cuello de botella de Von Newman y se obtiene un mejor desempeño. En la actualidad la mayoría de los procesadores modernos se conectan al exterior de manera similar a a la arquitectura Von Newman, con un banco de memoria masivo único, pero internamente incluyen varios niveles de memoria cache con bancos separados en cache de programa y cache de datos, buscando un mejor desempeño sin perder la versatilidad. 1.1.2 Arquitecturas Segmentadas. Las arquitecturas segmentadas o con segmentación del cauce buscan mejorar el desempeño realizando paralelamente varias etapas del ciclo de instrucción al mismo tiempo. El procesador se divide en varias

- 3. unidades funcionales independientes y se dividen entre ellas el procesamiento de las instrucciones. Para comprender mejor esto, supongamos que un procesador simple tiene un ciclo de instrucción sencillo consistente solamente en una etapa de búsqueda del código de instrucción y en otra etapa de ejecución de la instrucción. En un procesador sin segmentación del cauce, las dos etapas se realizarían de manera secuencial para cada una de la instrucciones, como lo muestra la siguiente figura. B1 E1 B2 E2 B3 E3 Figura 1.1.2.1 Búsqueda y ejecución en secuencia de tres instrucciones en un procesador sin segmentación del cause En un procesador con segmentación del cause, cada una de estas etapas se asigna a una unidad funcional diferente, la búsqueda a la unidad de búsqueda y la ejecución a la unidad de ejecución. Estas unidades pueden trabajar en forma paralela en instrucciones diferentes. Estas unidades se comunican por medio de una cola de instrucciones en la que la unidad de búsqueda coloca los códigos de instrucción que leyó para que la unidad de ejecución los tome de la cola y los ejecute. Esta cola se parece a un tubo donde las instrucciones entran por un extremo y salen por el otro. De esta analogía proviene el nombre en ingles: Pipelining o entubamiento. En general se divide al procesador segmentado en una unidad independiente por cada etapa del ciclo de instrucción. Unidad de Unidad de Cola de Instrucciones Búsqueda ejecución Figura 1.1.2.3 Comunicación entre las unidades en un procesador con segmentación de cauce. Completando el ejemplo anterior, en un procesador con segmentación, la unidad de búsqueda comenzaría buscando el código de la primera instrucción en el primer ciclo de reloj. Durante el segundo ciclo de reloj, la unidad de búsqueda obtendría el código de la instrucción 2, mientras que la unidad de ejecución ejecuta la instrucción 1 y así sucesivamente. La siguiente figura muestra este proceso. B1 B2 B3 B3 Unidad de búsqueda E1 E2 E3 Unidad de ejecución Figura 1.1.2.3 Búsqueda y ejecución en secuencia de tres instrucciones en un

- 4. procesador con segmentación del cause En este esquema sigue tomando el mismo numero de ciclos de reloj (el mismo tiempo), pero como se trabaja en varias instrucciones al mismo tiempo, el número promedio de instrucciones por segundo se multiplica. En teoría, el rendimiento de un procesador segmentado mejora con respecto a uno no segmentado en un factor igual al numero de etapas independientes. Sin embargo, la mejora en el rendimiento no es proporcional al numero de segmentos en el cauce debido a que cada etapa no toma el mismo tiempo en realizarse, además de que se puede presentar competencia por el uso de algunos recursos como la memoria principal. Otra razón por la que las ventajas de este esquema se pierden es cuando se encuentra un salto en el programa y todas las instrucciones que ya se buscaron y se encuentran en la cola, deben descartarse y comenzar a buscar las instrucciones desde cero a partir de la dirección a la que se salto. Esto reduce el desempeño del procesador y aún se investigan maneras de predecir los saltos para evitar este problema. Espera Espera Búsqueda Ejecución Figura 1.1.2.4 Consecuencias de la competencia por un recurso 1.1.3 Arquitecturas de multiprocesamiento. Cuando se desea incrementar el desempeño más aya de lo que permite la técnica de segmentación del cauce (limite teórico de una instrucción por ciclo de reloj), se requiere utilizar más de un procesador para la ejecución del programa de aplicación. Las CPU de multiprocesamiento se clasifican de la siguiente manera: ● SISO – (Single Instruction, Single Operand ) computadoras independientes ● SIMO – (Single Instruction, Multiple Operand ) procesadores vectoriales ● MISO – (Multiple Instruction, Single Operand ) No implementado ● MIMO – (Multiple Instruction, Multiple Operand ) sistemas SMP, Clusters Procesadores vectoriales – Son computadoras pensadas para aplicar un mismo algoritmo numérico a una serie de datos matriciales, en especial en la simulación de sistemas físicos complejos, tales como simuladores para predecir el clima, explosiones atómicas, reacciones químicas complejas, etc., donde los datos son representados como grandes números de datos en forma matricial sobr los que se deben se aplicar el mismo algoritmo numérico. En los sistemas SMP (Simetric Multiprocesesors), varios procesadores comparten la misma memoria principal y periféricos de I/O, Normalmente conectados por un bus común. Se conocen como simétricos, ya que ningún procesador toma el papel de maestro y los demás de esclavos, sino que todos tienen derechos similares en cuanto al acceso a la memoria y periféricos y ambos son administrados por el sistema operativo.

- 5. Los Clusters son conjuntos de computadoras independientes conectadas en una red de área local o por un bis de interconexión y que trabajan cooperativamente para resolver un problema. Es clave en su funcionamiento contar con un sistema operativo y programas de aplicación capaces de distribuir el trabajo entre las computadoras de la red. 1.2 Análisis de los componentes. 1.2.1 CPU. 1.2.1.1 Arquitecturas. Ademas de las arquitecturas clásicas mencionadas anteriormente, en la actualidad han aparecido arquitecturas híbridas entre la Von Newman y la Harvard, buscando conservar la flexibilidad, pero mejorando el rendimiento. El cambio más importante de los últimos años en diseño de las computadoras de los últimos años se dio durante los años 1980, con la aparición de la corriente de diseño conocida como computadoras de conjunto reducido de instrucciones (RISC, por sus siglas en ingles). Esta escuela pretende aplicar un enfoque totalmente distinto al tradicional hasta entonces, que paso a conocerse como computadoras de conjunto complejo de instrucciones (CISC) para diferenciarla de la nueva tendencia. La tendencia tradional, representada por las arquitecturas CISC (Complex Instruction Set Computers) se caracterizan por tener un número amplio de instrucciones y modos de direccionamiento. Se implementan instrucciones especiales que realizan funciones complejas, de manera que un programador puede encontrar con seguridad, una instrucción especial que realiza en hardware la función que el necesita. El número de registros del CPU es limitado, ya que las compuertas lógicas del circuito integrado se emplean para implementar las secuencias de control de estas instrucciones especiales. Al investigar las tendencias en la escritura de software científico y comercial al inicio de los 80, ya se pudo observar que en general ya no se programaba mucho en ensamblador, sino en lenguajes de alto nivel, tales como C. Los compiladores de lenguajes de alto nivel no hacían uso de las instrucciones especiales implementadas en los procesadores CISC, por lo que resultaba un desperdicio de recursos emplear las compuertas del circuito de esta forma. Por lo anterior, se decidió que era mejor emplear estos recursos en hacer que las pocas instrucciones que realmente empleaban los compiladores se ejecutaran lo más rápidamente posible. Así surgió la escuela de diseño RISC (Reduced Instruction Set Computers) donde solo se cuenta con unas pocas instrucciones y modos de direccionamiento, pero se busca implementarlos de forma muy eficiente y que todas las instrucciones trabajen con todos los modos de direccionamiento. Ademas, se observo que una de las tareas que tomaban más tiempo en ejecutarse en lenguajes de alto nivel, era el pasar los parámetros a las subrutinas a través de la pila. Como la forma más rápida de hacer este paso es por medio de registros del CPU, se busco dotarlo con un amplio número de registros, a través de los cuales se pueden pasar dichos parámetros. 1.2.1.2 Tipos. Los CPUs modernos pueden clasificarse de acuerdo a varias características, tales como: el tamaño del ALU o del Bus de conexión al exterior (8, 16, 32, 64 bits),si tienen cauce segmentado o no segmentado, si con tipo CISC o RISC, Von Newan o Harvard y si solo tienen instrucciones enteras o implementan también instrucciones de punto flotante

- 6. 1.2.1.3 Características. Las características más importantes a considerar al escoger un CPU para usarlo en una aplicación, son: •Modelo del programador (Conjunto de registros que el programador puede utilizar), forman el modelo mental del CPU que el programador utiliza al programar en ensamblador. •Conjunto de instrucciones que puede ejecutar el CPU •Modos de direccionamiento que pueden usarse para obtener los operandos de las instrucciones. •Ciclo de instrucción (el conjunto de pasos que realiza el CPU para procesar cada instrucción) •Buses de interconexión, usados para que el CPU lea y escriba a la memoria y a los dispositivos de entrada y salida. 1.2.1.4 Funcionamiento. Debido a la gran variedad de CPU disponibles comercialmente, se explicara el funcionamiento de un unidad central de proceso imaginaria muy simple, pero que resume el funcionamiento básico de la mayoría de los CPUs. Este CPU es similar a las primeras computadoras existentes en los años 1950s. Esta computadora contara con una memoria de 4096 palabras de 16 bits cada una. Esto corresponde a un bus de direcciones de 12 bits y un bus de datos de 16 bits). En cada localidad de memoria se podrá almacenar un entero de 16 bits o el código de una instrucción, también de 16 bits. Todos los CPU tienen como función principal la ejecución de un programa acorde a la aplicación del mismo. Un programa es un conjunto de instrucciones almacenadas de acuerdo al orden en que deben ejecutarse. Por lo tanto, toda computadora debe ser capaz de procesar las instrucciones de su programa en un ciclo de instrucción, consistente en un número de etapas que varia con cada CPU, pero que tradicionalmente han sido tres: 1-Búsqueda del código de Instrucción. Esta consiste en leer de la memoria cual será la siguiente instrucción a ejecutar, la cual esta almacenada en forma de un código numérico que indica cual de todas las operaciones que puede realizar el CPU sera la siguiente y con que operandos se ejecutara. 2- Decodificación. Consiste en tomar el código numérico e identificar a cual de las operaciones que puede realizar el CPU corresponde dicho código. El proceso contrario, la codificación, consiste en conociendo la instrucción, determinar el número que la va a representar. Esta etapa usualmente se realiza con un decodificador binario. 3- Ejecución. En esta etapa se lleva a cabo la operación sobre los datos que se vallan a procesar. En general, la unidad de control (CU) genera las señales de control necesarias para llevar los datos a las entradas de la Unidad Aritmética Lógica, la cual efectuará las operaciones aritméticas y lógicas. Posteriormente, la unidad de control generara las señales de control necesarias para transferir la salida de la Unidad Aritmética Lógica al registro donde serán almacenados los resultados para su uso posterior.

- 7. Búsqueda de la Instrucción Decodificación de la Instrucción Ejecución de la Instrucción Figura 1.2.1.4.1 Ciclo de instrucción Es importante recordar que cada instrucción del programa se almacena en memoria como un número binario. Este número se conoce como código de instrucción, y usualmente se divide en al menos dos campos: un código de operación (Opcode) y un número que representa al operando u operandos de la instrucción. En el caso de la computadora imaginaria que estamos estudiando, se almacena cada instrucción en una de las 4096 palabras de memoria de 16 bits cada una. Se utiliza un formato de un solo operando, con un segundo operando en el acumulador cuando es necesario. Los cuatro bits más significativos de los dieciséis bits de la palabra se dedican a almacenar el código de operación. Los doce bits menos significativos se dedican a almacenar la dirección del operando. Código de Instrucción Operación Operando 1 Operando 2 Operando único Codigo de Operación Figura 1.2.1.4.2 Codificación de las instrucciones La siguiente tabla resume los códigos de operación de la computadora de ejemplo. Código de Operación Instrucción Operación 0h LOAD (Carga) ACC<-[M] 1h STORE (Almacena) [M]<-ACC 2h ADD (Suma) ACC<-ACC+[M] 3h ADC (Suma con Acarreo) ACC<-ACC+[M]+C 4h SUB (Resta) ACC<-ACC+-M]

- 8. 5h OR (Or Bit a Bit) ACC<-ACC or [M] 6h AND (And bit a Bit) ACC<-ACC and [M] 7h XOR (Xor Bit a Bit) ACC<-ACC xor [M] 8h SHL (Corrimiento a la Izquierda) ACC<-ACC << 1 9h SHR (Corrimiento a la derecha) ACC<-ACC >> 1 Ah BRA Bifurcación o salto PC<-M Bh BRZ (Bifurca si es Cero) Si Z==1 => PC<-M Ch BRC (Bifurca si hay Acarreo) Si Z==1 => PC<-M Dh BRO (Bifurca si hay Sobreflujo) Si Z==1 => PC<-M Eh LDI (Carga Constante Inmediata) ACC <-[PC]; PC<-PC+1 Fh STOP Detener la ejecución Tabla 1.2.1.4.1 Códigos de operación para la computadora de ejemplo Las partes del CPU de la computadora imaginaria son: ACC – Acumulador, se usará para almacenar uno de los operandos y el resultado de varias de las instrucciones MAR – (Memory Address Register) Registro de dirección de memoria, selecciona a que localidad de memoria se va a leer o a escribir. MBR – (Memory Bus Register) Registro de bus de memoria. A través de él se lee y se escriben los datos. PC – (Program Counter) El contador de programa almacena la dirección de la siguiente instrucción a buscar. Por esta razón también es conocido como apuntador de instrucciones. IR - Registro de instrucción, guarda el código de la instrucción que se esta ejecutando. Flags – Registro de Banderas, agrupa a todas las banderas de la ALU en un registro, en el caso de nuestra computadora imaginaria, las banderas disponibles serán: Z – Bandera de Cero, se pone en uno cuando todos los bits del resultado son cero; O – Sobreflujo, se pone en uno cuando el resultado de la ultima operación se sale de el rango de los números de 16 bits con signo; C – Acarreo, se enciende cuando el resultado de la ultima operación se sale del rengo de los números de 16 bits sin signo.

- 9. Contenido Dir. XXXXh 000h Banderas XXXXh 001h MAR 2023h 002h Acumulador 4024h 003h BUS ... PC XXXXh 022h MBR 1234h 023h IR 4567h 024h ... XXXXh FFFh CPU Memoria Figura 1.2.1.4.2 Diagrama a bloques del CPU a estudiar Como se explico anteriormente, el funcionamiento del CPU se basa en los pasos del ciclo de instrucción, consistentes en búsqueda, decodificación y ejecución de la instrucción. Comenzaremos revisando los pasos correspondientes a la búsqueda de la instrucción. El registro PC contiene la dirección de la localidad de memoria que contiene el código de instrucción de la siguiente instrucción a ejecutar. Como la etapa de búsqueda consistirá básicamente en leer este código y almacenarlo en el registro IR para su posterior uso en las etapas de decodificación y ejecución, el contenido de PC se copia al MAR para poder leer esa localidad de memoria. Se lee la memoria y el resultado de dicha lectura se copia del MBR al IR. Finalmente, se incrementa el PC para que en el siguiente ciclo de instrucción se lea la instrucción de la localidad de memoria consecutiva. Resumiendo estas operaciones en lenguaje de transferencia de registros: MAR<-PC IR<-[MAR] PC<-PC+1 En la etapa de decodificación simplemente se separan los códigos de operación de los operandos. Por ejemplo, la instrucción LOAD 023h se codificaría como 0023h, siendo 0h el código de operación y 023h el operando. Además, la unidad de control deberá identificar que al opcode 0 corresponde a la instrucción LOAD para que en la siguiente etapa se realicen las operaciones correspondientes a esta instrucción. En cuanto a la etapa de ejecución, los pasos realizados en esta etapa varían dependiendo del código de operación leído en la etapa de búsqueda. Por ejemplo, si el código leído es un 0, que corresponde con una instrucción LOAD, la etapa de ejecución consistirá en copiar la parte de la dirección del operando en el registro MAR para poder leer la localidad en donde se encuentra el operando. Se lee el operando de memoria y el dato leído se copia del MBR al acumulador. Resumiendo dichas operaciones en lenguaje de transferencia de registros se tiene: MAR<-IR(M) //IR(M) representa los bits del registro IR que almacenan la dirección del operando ACC<-MBR

- 10. Para el código de operación 2, correspondiente a la instrucción ADD, también se transfiere la dirección del operando al MAR y se lee el contenido de la memoria, pero en vez de enviarse directamente del MBR al acumulador, se envía al ALU para que se sume con el contenido del acumulador y posteriormente se almacene el resultado de la suma en el acumulador. Resumiendo en lenguaje de transferencia de registros: MAR<-IR(M) //IR(M) representa los bits del registro IR que almacenan la dirección del operando ACC<-ACC+MBR La columna operación de la Tabla 1.2.1.4.1 proporciona un resumen el lenguaje de transferencia de registros de las operaciones correspondientes a cada código de operación. 1.2.2 Memoria. Una memoria es un dispositivo que puede mantenerse en por lo menos dos estados estables por un cierto periodo de tiempo. Cada uno de estos estados estables puede utilizarse para representar un bit. A un dispositivo con la capacidad de almacenar por lo menos un bit se le conoce como celda básica de memoria. Un dispositivo de memoria completo se forma con varias celdas básicas y los circuitos asociados para poder leer y escribir dichas celdas básicas, agrupadas como localidades de memoria que permitan almacenar un grupo de N bits. El número de bits que puede almacenar cada localidad de memoria es conocido como el ancho de palabra de la memoria. Coincide con el ancho del bus de datos. Uno de los circuitos auxiliares que integran la memoria es el decodificador de direcciones. Su función es la de activar a las celdas básicas que van a ser leídas o escritas a partir de la dirección presente en el bus de direcciones. Tiene como entradas las n lineas del bus de direcciones y 2N lineas de habilitación de localidad, cada una correspondiente a una combinación binaria distinta de los bits de direcciones. Por lo tanto, el número de localidades de memoria disponibles en un dispositivo (T) se relaciona con el número de lineas de dirección N por T= 2N . 1.2.2.1 Arquitecturas. Desde hace unas decenas de años, los procesadores han estado aumentando su velocidad de operación a un paso mucho más rápido que las memorias, lo que ha llevado a la situación en que los procesadores actuales operan mucho más rápidamente que la memoria principal de las computadoras. Esto hace que el procesador tenga que quedarse detenido por varios ciclos de reloj (estados de espera) cada vez que tiene que leer o escribir a la memoria principal. Para aliviar un poco esta situación conservando el precio de la computadora razonablemente bajo, se ha organizado a la memoria como una jerarquía de diversos niveles con distintos tamaños y velocidades. Hay que recordar que la memoria más rápida es mucho más cara que la más lenta y que por lo tanto, es menor la cantidad de memoria de este tipo que se puede usar. Esta estructura jerárquica se ilustra en la figura 1.2.2.1. De esta manera, la mayor parte de la capacidad de almacenamiento de la maquina se encuentra en el disco duro, que tiene un costo por Gbyte muy bajo, pero que también es muy lento debido a que hay que mover piezas mecánicas para leer o escribir en él. En seguida se encuentra la memoria principal, que normalmente es del tipo RAM dinámica. Es en esta memoria donde se almacenan los programas para que los pueda ejecutar el procesador, así como los datos con que trabajan dichos programas. Con el objetivo de mejorar la velocidad del procesador al ejecutar ciclos y al leer repetidamente datos de uso común, se coloca una pequeña cantidad de memoria RAM estática entre el procesador y la memoria principal. Esta memoria es conocida como memoria cache y guarda una copia de una pequeña región de la memoria principal, para que si se requiere volver a leer los datos almacenados en esta región de memoria, no se tenga que esperar a que se lea la memoria principal, que

- 11. es mucho más lenta que la cache y que el procesador. Finalmente, en la cima de la jerarquía, se encuentran los registros del procesador que aunque son muy pocos, son los que se pueden leer y escribir más rápidamente. Menor tamaño, Mayor Velocidad Registros del procesador Memoria Cache Memoria principal Disco Duro Menor velocidad, mayor tamaño Figura 1.2.2.1 Jerarquía de memoria en un procesador Moderno 1.2.2.2 Tipos. Los diversos tipos de memorias se clasifican como memorias volátiles y memorias no volátiles. Las memorias volátiles pierden la información que almacenan al momento en que se les desconecta la energía, mientras que las no volátiles conservan su contenido aunque no estén alimentadas. Las memorias volátiles son conocidas desde las primeras computadoras como memorias de acceso aleatorio (RAM), ya que en esa época las memorias volátiles eran de acceso secuencial. Dentro de las memorias volátiles se encuentran las subclases RAM Dinámica y RAM Estática. Las memorias no volátiles conservan sus datos a pesar de que en este conectadas el voltaje del alimentación. De hecho pueden conservar sus datos por un periodo de tiempo relativamente largo, usualmente entre cien y 200 años. Conforme evolucionado la tecnología, se han desarrollado diversas familias de rumores no volátiles, entre las cuales se encuentran: la memoria de solo lectura (ROM - Read only Memory), la memoria de solo lectura programable (PROM -Programable Read only Memory), la memoria de solo lectura programable y borrable (EPROM - Erasable Read only Memory), la memoria de solo lectura programable y borrable eléctricamente (EEPROM Electricaly Erasable Read

- 12. only Memory) y la memoria flash. 1.2.2.3 Características. En cuanto a las memorias volátiles, la memoria RAM dinámica es muy rápida pero muy cara. En contraste, la memoria RAM estática es muy barata pero muy lenta. En general, las memorias no volátiles son baratas y su precio depende sobre todo de su capacidad de almacenamiento. Algunas de estas tecnologías son consideradas obsoletas y por lo tanto casi no son utilizadas en actualidad. 1.2.2.4 Funcionamiento. El tipo más común de memorias volátiles es la RAM dinámica, que utiliza la capacitancia parásita de los transistores MOSFET con los que esta construida para almacenar un bit. Como solo se requiere de un transistor por celda de memoria, esta memoria es muy económica, pero debido al tiempo que toma cargar la gran capacitancia de los transistores con los que esta construida, es muy lenta. S e le c c ió n d e r e n g lo n C a p a c ita n c ia I/O d e p a r á s ita C o lu m n a Figura 1.2.2.4.1 - Estructura de una celda de RAM Dinámica mostrando la capacitancia parásita en donde se almacenan el dato. El otro tipo de memoria RAM utilizado en la actualidad, es la RAM estática. Esta memoria se construye con el mismo tipo de transistores con los que se construyen los procesadores, por lo que pueden operar a una velocidad similar a la del procesador. Sin embargo, como se requieren alrededor de 8 transistores por bit, el costo de esta memoria es mucho más alto que el de la RAM dinámica.

- 13. I/O de columna Selección de renglon Figura 1.2.2.4.2 Estructura de una celda de RAM Estática a nivel de transistores. En cuanto a las memorias no volátiles, En cuanto a las memorias no volátiles, históricamente han existido varios tipos. Los primeros sólo podían ser leídos, por lo que fueron conocidos como memorias de solo lectura (ROM - Read Only Memory). A pesar de que los tipos más modernos permiten que su contenido se ha modificado por el usuario, aún son conocidos como memorias de solo lectura. En las memorias de solo lectura originales (ROM), el almacenar en uno o un cero, depende de si el fabricante colocó o no un diodo físicamente en el circuito de la memoria. De esta manera, el contenido de la memoria queda establecido por el fabricante desde el momento de su construcción y no es posible que el usuario no modifique. Sin embargo, este tipo de memoria es aún muy usada debido a que es muy económica y por lo tanto, ideal para la producción en masa de muchos artefactos de consumo masivo. CE A2 A1 A0 Salida 1 0 0 0 0 1 0 0 1 1 1 0 1 0 0 1 0 1 1 1 1 1 0 0 1 1 1 0 1 0 1 1 1 0 1 1 1 1 1 0 0 X X X HZ Figura 1.2.2.4.3 – Estructura de una memoria ROM de 8x1 bits y la tabla con el contenido de cada celda. Solo hay ceros en las columnas con un diodo conectado. Con el objetivo de hacer a la memoria de solo lectura un dispositivo más versátil, algunos fabricantes de memorias sustituyeron a los diodos por fusibles semiconductores que el usuario podía quemar usando un programador especial. Esto permitió a los usuarios tener dispositivos de memoria de solo lectura cuyo contenido ellos mismos podían programar, por lo que estos dispositivos fueron conocidos

- 14. como memorias de solo lectura programables (PROM - Programable Read Only Memory). El único inconveniente que presentaban estas memorias era que si se necesitaba hacer un pequeño cambio, debía descartarse a la memoria ya programada y utilizar un dispositivo nuevo en blanco. Este problema pudo eliminarse al sustituir los fusibles semiconductores por transistores con una compuerta flotante que les permitía almacenar una carga eléctrica por un tiempo muy grande. Esta compuerta flotante permite almacenar una carga eléctrica que reduce el voltaje que debe ser aplicado a la compuerta principal para hacer que el rector conduzca. De esta manera, aplicando un voltaje de prueba a la compuerta principal y observando si el transistor conduce, se puede saber si un transistor no tiene carga en su compuerta flotante (está borrado o almacena un uno) o sí (estaba programado o almacena un cero). La primera generación de dispositivos que utilizó esta tecnología, conocidos como memorias de solo lectura programables y borrables (EPROM), podían grabarse eléctricamente aplicando un voltaje más alto de lo normal a la compuerta principal. Sin embargo, para eliminar la carga tendría que aplicarse una luz ultravioleta intensa al dispositivo, lo cual eliminaba la carga almacenada en la compuerta flotante. Para realizar este proceso de borrado era necesario retirar al dispositivo del circuito de aplicación y colocarlo en el borrador de luz ultravioleta por aproximadamente media hora . En la segunda generación de dispositivos de memoria que utilizaban transistores con compuertas flotante se logró eliminar la carga eléctricamente, con lo que dichos dispositivos se volvieron más versátiles. Los dispositivos de esta generación se conocieron como memorias de solo lectura programables y borrables eléctricamente (EEPROM). Como cada byte de la memoria podía ser borrado de forma independiente, requerían de muchos circuitos auxiliares para permitir este tipo de borrado, lo que aumentaba su costo. Para la tercera generación, se buscó reducir el costo de los dispositivos reduciendo la cantidades circuitos auxiliares necesarios para el borrado. Esto se logró permitiendo únicamente el borrado de bloques de memoria de tamaño relativamente grande. También se buscó almacenar más de un bit por celda de memoria controlando la cantidad de carga almacenada en cada celda, de manera que con ocho voltajes discretos se pueden representar las ocho combinaciones correspondientes a tres bits. Los dispositivos de esta generación son conocidos como memorias FLASH. 1.2.3 Dispositivos de I/O. 1.2.3.1 Arquitecturas. 1.2.3.2 Tipos. 1.2.3.3 Características. 1.2.3.4 Funcionamiento.