Recommended

Program control, instruction executionLec19 Intro to Computer Engineering by Hsien-Hsin Sean Lee Georgia Tech -- Pr...

Lec19 Intro to Computer Engineering by Hsien-Hsin Sean Lee Georgia Tech -- Pr...Hsien-Hsin Sean Lee, Ph.D.

Dynamic Instruction scheduling algorithms in microprocessorsLec8 Computer Architecture by Hsien-Hsin Sean Lee Georgia Tech -- Dynamic Sch...

Lec8 Computer Architecture by Hsien-Hsin Sean Lee Georgia Tech -- Dynamic Sch...Hsien-Hsin Sean Lee, Ph.D.

More Related Content

What's hot

Program control, instruction executionLec19 Intro to Computer Engineering by Hsien-Hsin Sean Lee Georgia Tech -- Pr...

Lec19 Intro to Computer Engineering by Hsien-Hsin Sean Lee Georgia Tech -- Pr...Hsien-Hsin Sean Lee, Ph.D.

Dynamic Instruction scheduling algorithms in microprocessorsLec8 Computer Architecture by Hsien-Hsin Sean Lee Georgia Tech -- Dynamic Sch...

Lec8 Computer Architecture by Hsien-Hsin Sean Lee Georgia Tech -- Dynamic Sch...Hsien-Hsin Sean Lee, Ph.D.

What's hot (20)

Programming ATmega microcontroller using Embedded C

Programming ATmega microcontroller using Embedded C

Lec19 Intro to Computer Engineering by Hsien-Hsin Sean Lee Georgia Tech -- Pr...

Lec19 Intro to Computer Engineering by Hsien-Hsin Sean Lee Georgia Tech -- Pr...

BKK16-503 Undefined Behavior and Compiler Optimizations – Why Your Program St...

BKK16-503 Undefined Behavior and Compiler Optimizations – Why Your Program St...

Pragmatic Optimization in Modern Programming - Demystifying the Compiler

Pragmatic Optimization in Modern Programming - Demystifying the Compiler

Lec8 Computer Architecture by Hsien-Hsin Sean Lee Georgia Tech -- Dynamic Sch...

Lec8 Computer Architecture by Hsien-Hsin Sean Lee Georgia Tech -- Dynamic Sch...

Similar to Hd10

Similar to Hd10 (20)

Realization of an 8 bit pipelined microprocessor in verilog hdl

Realization of an 8 bit pipelined microprocessor in verilog hdl

Designing of fifo and serial peripheral interface protocol using Verilog HDL

Designing of fifo and serial peripheral interface protocol using Verilog HDL

Connectivity for Local Sensors and Actuators Using nRF24L01+

Connectivity for Local Sensors and Actuators Using nRF24L01+

8051 TIMER COUNTER SERIAL COMM. INTERUPT PROGRAMMING.pdf

8051 TIMER COUNTER SERIAL COMM. INTERUPT PROGRAMMING.pdf

Pragmatic Optimization in Modern Programming - Mastering Compiler Optimizations

Pragmatic Optimization in Modern Programming - Mastering Compiler Optimizations

More from Prakash Rao

More from Prakash Rao (20)

Electromagnetic Theory and Transmission Lines by Dr. R. Prakash Rao

Electromagnetic Theory and Transmission Lines by Dr. R. Prakash Rao

Recently uploaded

Call Girl Aurangabad Indira Call Now: 8617697112 Aurangabad Escorts Booking Contact Details WhatsApp Chat: +91-8617697112 Aurangabad Escort Service includes providing maximum physical satisfaction to their clients as well as engaging conversation that keeps your time enjoyable and entertaining. Plus they look fabulously elegant; making an impressionable. Independent Escorts Aurangabad understands the value of confidentiality and discretion - they will go the extra mile to meet your needs. Simply contact them via text messaging or through their online profiles; they'd be more than delighted to accommodate any request or arrange a romantic date or fun-filled night together. We provide –(INDIRA) Call Girl Aurangabad Call Now 8617697112 Aurangabad Escorts 24x7

(INDIRA) Call Girl Aurangabad Call Now 8617697112 Aurangabad Escorts 24x7Call Girls in Nagpur High Profile Call Girls

Process of Integration the Laser Scan Data into FEA Model and Level 3 Fitness-for-Service Assessment of Critical Assets in Refinery & Process IndustriesFEA Based Level 3 Assessment of Deformed Tanks with Fluid Induced Loads

FEA Based Level 3 Assessment of Deformed Tanks with Fluid Induced LoadsArindam Chakraborty, Ph.D., P.E. (CA, TX)

Welcome to the April edition of WIPAC Monthly, the magazine brought to you by Water Industry Process Automation & Control.

In this month's edition, along with the latest news from the industry we have articles on:

The use of artificial intelligence and self-service platforms to improve water sustainability

A feature article on measuring wastewater spills

An article on the National Underground Asset Register

Have a good month,

OliverWater Industry Process Automation & Control Monthly - April 2024

Water Industry Process Automation & Control Monthly - April 2024Water Industry Process Automation & Control

Call Girl Meerut Indira Call Now: 8617697112 Meerut Escorts Booking Contact Details WhatsApp Chat: +91-8617697112 Meerut Escort Service includes providing maximum physical satisfaction to their clients as well as engaging conversation that keeps your time enjoyable and entertaining. Plus they look fabulously elegant; making an impressionable. Independent Escorts Meerut understands the value of confidentiality and discretion - they will go the extra mile to meet your needs. Simply contact them via text messaging or through their online profiles; they'd be more than delighted to accommodate any request or arrange a romantic date or fun-filled night together. We provide –(INDIRA) Call Girl Meerut Call Now 8617697112 Meerut Escorts 24x7

(INDIRA) Call Girl Meerut Call Now 8617697112 Meerut Escorts 24x7Call Girls in Nagpur High Profile Call Girls

Top Rated Pune Call Girls Budhwar Peth ⟟ 6297143586 ⟟ Call Me For Genuine Sex Service At Affordable Rate

Booking Contact Details

WhatsApp Chat: +91-6297143586

pune Escort Service includes providing maximum physical satisfaction to their clients as well as engaging conversation that keeps your time enjoyable and entertaining. Plus they look fabulously elegant; making an impressionable.

Independent Escorts pune understands the value of confidentiality and discretion - they will go the extra mile to meet your needs. Simply contact them via text messaging or through their online profiles; they'd be more than delighted to accommodate any request or arrange a romantic date or fun-filled night together.

We provide -

01-may-2024(v.n)

Top Rated Pune Call Girls Budhwar Peth ⟟ 6297143586 ⟟ Call Me For Genuine Se...

Top Rated Pune Call Girls Budhwar Peth ⟟ 6297143586 ⟟ Call Me For Genuine Se...Call Girls in Nagpur High Profile

Model Call Girl Services in Delhi reach out to us at 🔝 9953056974 🔝✔️✔️

Our agency presents a selection of young, charming call girls available for bookings at Oyo Hotels. Experience high-class escort services at pocket-friendly rates, with our female escorts exuding both beauty and a delightful personality, ready to meet your desires. Whether it's Housewives, College girls, Russian girls, Muslim girls, or any other preference, we offer a diverse range of options to cater to your tastes.

We provide both in-call and out-call services for your convenience. Our in-call location in Delhi ensures cleanliness, hygiene, and 100% safety, while our out-call services offer doorstep delivery for added ease.

We value your time and money, hence we kindly request pic collectors, time-passers, and bargain hunters to refrain from contacting us.

Our services feature various packages at competitive rates:

One shot: ₹2000/in-call, ₹5000/out-call

Two shots with one girl: ₹3500/in-call, ₹6000/out-call

Body to body massage with sex: ₹3000/in-call

Full night for one person: ₹7000/in-call, ₹10000/out-call

Full night for more than 1 person: Contact us at 🔝 9953056974 🔝. for details

Operating 24/7, we serve various locations in Delhi, including Green Park, Lajpat Nagar, Saket, and Hauz Khas near metro stations.

For premium call girl services in Delhi 🔝 9953056974 🔝. Thank you for considering us!Call Now ≽ 9953056974 ≼🔝 Call Girls In New Ashok Nagar ≼🔝 Delhi door step de...

Call Now ≽ 9953056974 ≼🔝 Call Girls In New Ashok Nagar ≼🔝 Delhi door step de...9953056974 Low Rate Call Girls In Saket, Delhi NCR

Booking open Available Pune Call Girls Koregaon Park 6297143586 Call Hot Indian Girls Waiting For You To Fuck

Booking Contact Details

WhatsApp Chat: +91-6297143586

pune Escort Service includes providing maximum physical satisfaction to their clients as well as engaging conversation that keeps your time enjoyable and entertaining. Plus they look fabulously elegant; making an impressionable.

Independent Escorts pune understands the value of confidentiality and discretion - they will go the extra mile to meet your needs. Simply contact them via text messaging or through their online profiles; they'd be more than delighted to accommodate any request or arrange a romantic date or fun-filled night together.

We provide -

01-may-2024(v.n)

Booking open Available Pune Call Girls Koregaon Park 6297143586 Call Hot Ind...

Booking open Available Pune Call Girls Koregaon Park 6297143586 Call Hot Ind...Call Girls in Nagpur High Profile

Call Girl Bhosari Indira Call Now: 8617697112 Bhosari Escorts Booking Contact Details WhatsApp Chat: +91-8617697112 Bhosari Escort Service includes providing maximum physical satisfaction to their clients as well as engaging conversation that keeps your time enjoyable and entertaining. Plus they look fabulously elegant; making an impressionable. Independent Escorts Bhosari understands the value of confidentiality and discretion - they will go the extra mile to meet your needs. Simply contact them via text messaging or through their online profiles; they'd be more than delighted to accommodate any request or arrange a romantic date or fun-filled night together. We provide –(INDIRA) Call Girl Bhosari Call Now 8617697112 Bhosari Escorts 24x7

(INDIRA) Call Girl Bhosari Call Now 8617697112 Bhosari Escorts 24x7Call Girls in Nagpur High Profile Call Girls

Recently uploaded (20)

(INDIRA) Call Girl Aurangabad Call Now 8617697112 Aurangabad Escorts 24x7

(INDIRA) Call Girl Aurangabad Call Now 8617697112 Aurangabad Escorts 24x7

FEA Based Level 3 Assessment of Deformed Tanks with Fluid Induced Loads

FEA Based Level 3 Assessment of Deformed Tanks with Fluid Induced Loads

Call Girls Wakad Call Me 7737669865 Budget Friendly No Advance Booking

Call Girls Wakad Call Me 7737669865 Budget Friendly No Advance Booking

VIP Model Call Girls Kothrud ( Pune ) Call ON 8005736733 Starting From 5K to ...

VIP Model Call Girls Kothrud ( Pune ) Call ON 8005736733 Starting From 5K to ...

Water Industry Process Automation & Control Monthly - April 2024

Water Industry Process Automation & Control Monthly - April 2024

(INDIRA) Call Girl Meerut Call Now 8617697112 Meerut Escorts 24x7

(INDIRA) Call Girl Meerut Call Now 8617697112 Meerut Escorts 24x7

Top Rated Pune Call Girls Budhwar Peth ⟟ 6297143586 ⟟ Call Me For Genuine Se...

Top Rated Pune Call Girls Budhwar Peth ⟟ 6297143586 ⟟ Call Me For Genuine Se...

Cara Menggugurkan Sperma Yang Masuk Rahim Biyar Tidak Hamil

Cara Menggugurkan Sperma Yang Masuk Rahim Biyar Tidak Hamil

FULL ENJOY Call Girls In Mahipalpur Delhi Contact Us 8377877756

FULL ENJOY Call Girls In Mahipalpur Delhi Contact Us 8377877756

Call Now ≽ 9953056974 ≼🔝 Call Girls In New Ashok Nagar ≼🔝 Delhi door step de...

Call Now ≽ 9953056974 ≼🔝 Call Girls In New Ashok Nagar ≼🔝 Delhi door step de...

XXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXX

XXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXX

Booking open Available Pune Call Girls Koregaon Park 6297143586 Call Hot Ind...

Booking open Available Pune Call Girls Koregaon Park 6297143586 Call Hot Ind...

(INDIRA) Call Girl Bhosari Call Now 8617697112 Bhosari Escorts 24x7

(INDIRA) Call Girl Bhosari Call Now 8617697112 Bhosari Escorts 24x7

Hd10

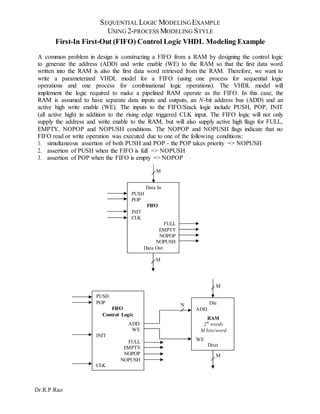

- 1. SEQUENTIAL LOGIC MODELING EXAMPLE USING 2-PROCESS MODELING STYLE Dr.R.P.Rao Din ADD RAM 2N words M bits/word WE Dout PUSH POP FIFO Control Logic ADD WE INIT FULL EMPTY NOPOP NOPUSH CLK First-In First-Out (FIFO) Control Logic VHDL Modeling Example A common problem in design is constructing a FIFO from a RAM by designing the control logic to generate the address (ADD) and write enable (WE) to the RAM so that the first data word written into the RAM is also the first data word retrieved from the RAM. Therefore, we want to write a parameterized VHDL model for a FIFO (using one process for sequential logic operations and one process for combinational logic operations). The VHDL model will implement the logic required to make a pipelined RAM operate as the FIFO. In this case, the RAM is assumed to have separate data inputs and outputs, an N-bit address bus (ADD) and an active high write enable (WE). The inputs to the FIFO/Stack logic include PUSH, POP, INIT (all active high) in addition to the rising edge triggered CLK input. The FIFO logic will not only supply the address and write enable to the RAM, but will also supply active high flags for FULL, EMPTY, NOPOP and NOPUSH conditions. The NOPOP and NOPUSH flags indicate that no FIFO read or write operation was executed due to one of the following conditions: 1. simultaneous assertion of both PUSH and POP - the POP takes priority => NOPUSH 2. assertion of PUSH when the FIFO is full => NOPUSH 3. assertion of POP when the FIFO is empty => NOPOP M M M N M Data In PUSH POP FIFO INIT CLK FULL EMPTY NOPOP NOPUSH Data Out

- 2. SEQUENTIAL LOGIC MODELING EXAMPLE USING 2-PROCESS MODELING STYLE Dr.R.P.Rao library IEEE; use IEEE.std_logic_1164.all; use IEEE.std_logic_unsigned.all; entity FIFO_LOGIC is generic (N: integer := 3); port (CLK, PUSH, POP, INIT: in std_logic; ADD: out std_logic_vector(N-1 downto 0); FULL, EMPTY, WE, NOPUSH, NOPOP: buffer std_logic); end entity FIFO_LOGIC; architecture RTL of FIFO_LOGIC is signal WPTR, RPTR: std_logic_vector(N-1 downto 0); signal LASTOP: std_logic; begin SYNC: process (CLK) begin if (CLK'event and CLK = '1') then if (INIT = '1') then -- initialization -- WPTR <= (others => '0'); RPTR <= (others => '0'); LASTOP <= '0'; elsif (POP = '1' and EMPTY = '0') then -- pop -- RPTR <= RPTR + 1; LASTOP <= '0'; elsif (PUSH = '1' and FULL = '0') then -- push -- WPTR <= WPTR + 1; LASTOP <= '1'; end if; -- otherwise all Fs hold their value -- end if; end process SYNC; COMB: process (PUSH, POP, WPTR, RPTR, LASTOP, FULL, EMPTY) begin -- full and empty flags -- if (RPTR = WPTR) then if (LASTOP = '1') then FULL <= '1'; EMPTY <= '0'; else else end if; FULL <= '0'; EMPTY <= '1'; end if; FULL <= '0'; EMPTY <= '0';

- 3. SEQUENTIAL LOGIC MODELING EXAMPLE USING 2-PROCESS MODELING STYLE Dr.R.P.Rao -- address, write enable and nopush/nopop logic -- if (POP = '0' and PUSH = '0') then -- no operation-- ADD <= RPTR; WE <= '0'; NOPUSH <= '0'; NOPOP <= '0'; elsif (POP = '0' and PUSH = '1') then -- push only -- ADD <= WPTR; NOPOP <= '0'; if (FULL = '0') then -- valid write condition -- WE <= '1'; NOPUSH <= '0'; else -- no write condition -- WE <= '0'; NOPUSH <= '1'; end if; elsif (POP = '1' and PUSH = '0') then -- pop only -- ADD <= RPTR; NOPUSH <= '0'; WE <= '0'; if (EMPTY = '0') then -- valid read condition -- NOPOP <= '0'; else end if; NOPOP <= '1'; -- no red condition -- else -- push and pop at same time – if (EMPTY = ‘0’) then -- valid pop -- ADD <= RPTR; WE <= '0'; NOPUSH <= '1'; NOPOP <= '0'; end if; else end if; ADD <= wptr; WE <= ‘1’; NOPUSH <= ‘0’; NOPOP <= ‘1’; end process COMB; end architecture RTL;

- 4. SEQUENTIAL LOGIC MODELING EXAMPLE USING 2-PROCESS MODELING STYLE Dr.R.P.Rao With a VHDL model for the RAM and FIFO controllogic complete, we can generate a top-level hierarchical model of the complete FIFO: library IEEE; use IEEE.std_logic_1164.all; use IEEE.std_logic_unsigned.all; entity FIFO is generic (N: integer := 3; -- number of address bits for 2**N address locations M: integer := 5); -- number of data bits to/from FIFO port (CLK, PUSH, POP, INIT: in std_logic; DIN: in std_logic_vector(N-1 downto 0); DOUT: out std_logic_vector(N-1 downto 0); FULL, EMPTY, NOPUSH, NOPOP: out std_logic); end entity FIFO; architecture TOP_HIER of FIFO is signal WE: std_logic; signal A: std_logic_vector(N-1 downto 0); component FIFO_LOGIC is generic (N: integer); -- number of address bits port (CLK, PUSH, POP, INIT: in std_logic; ADD: out std_logic_vector(N-1 downto 0); FULL, EMPTY, WE, NOPUSH, NOPOP: buffer std_logic); end component FIFO_LOGIC; component RAM is generic (K, W: integer) -- number of address and data bits port (WR: in std_logic; -- active high write enable ADDR: in std _ logic _vector (W-1 downto 0); -- RAM address DIN: in std _ logic _ vector (K-1 downto 0); -- write data DOUT: out std _ logic _ vector (K-1 downto 0)); -- read data end component RAM; begin -- example of component instantiation using positional notation FL: FIFO_LOGIC generic map (N) port map (CLK, PUSH, POP, INIT, A, FULL, EMPTY, WE, NOPUSH, NOPOP); -- example of component instantiation using keyword notation R: RAM generic map (W => N, K => M) port map (DIN => DIN, ADDR => A, WR => WE, DOUT => DOUT); end architecture TOP_HIER;