Mealy state machine

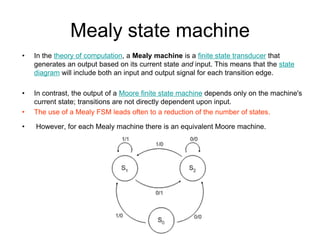

- 1. Mealy state machine • In the theory of computation, a Mealy machine is a finite state transducer that generates an output based on its current state and input. This means that the state diagram will include both an input and output signal for each transition edge. • In contrast, the output of a Moore finite state machine depends only on the machine's current state; transitions are not directly dependent upon input. • The use of a Mealy FSM leads often to a reduction of the number of states. • However, for each Mealy machine there is an equivalent Moore machine.

- 3. Moore state machine • In the theory of computation, a Moore machine is a finite state transducer where the outputs are determined by the current state alone (and do not depend directly on the input). The state diagram for a Moore machine will include an output signal for each state. Compare with a Mealy machine, which maps transitions in the machine to outputs. • The advantage of the Moore model is a simplification of the behavior.

- 5. Example • Q3.Derive a minimal state table for a single-input and single-output Moore-type FSM that produces an output of 1 if in the input sequence it detects either 110 or 101 patterns. Overlapping sequences should be detected. (Show the detailed steps of your solution.)

- 7. State Diagram Reset w=0 w=0 w=1 w=0 w=1 A/z=0 B/z=0 E/z=0 F/z=1 w=1 w=1 w=1 w=0 C/z=0 w=1 w=0 State Diagram D/z=1

- 8. Sate Table (Moore FSM) Present Next State Output state Z w=0 w=1 A A B 0 B E C 0 C D C 0 D A F 1 E A F 0 F E C 1 6 states need 3 flip-flops

- 9. State Assignment (Mealy FSM): state A: Got no 1 state B: Got”1” state C: Got”11” state D: Got”10” Reset 1/0 1/0 1/0 0/0 A B C 1/1 0/0 0/0 0/1 D State Diagram

- 10. Sate Table (Mealy FSM) Present Next State Output Z state w=0 w=1 w=0 w=1 A A B 0 0 B D C 0 0 C D C 1 0 D A B 0 1 4 states need 2 flip-flops