Digital Converters Family for Software Radio

•

1 like•283 views

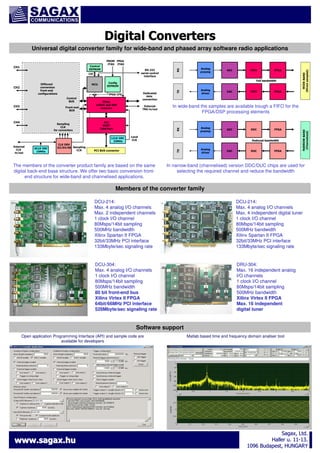

This document summarizes a universal digital converter family for software radio applications. It offers two front-end configurations: wide-band direct sampling and narrow-band channelized. In wide-band mode, samples are available through a FIFO for FPGA/DSP processing. In narrow-band mode, DDC/DUC chips are used to select channels and reduce bandwidth. The family includes products with up to 4 or 16 channels that sample at 80Msps with 14-bit resolution and 500MHz bandwidth, and interface with FPGAs and PCI buses. Open APIs and sample code are provided for developers.

Report

Share

Report

Share

Download to read offline

More Related Content

What's hot (20)

Basic Study on the WT12 Family of Bluetooth Devices

Basic Study on the WT12 Family of Bluetooth Devices

Similar to Digital Converters Family for Software Radio

High Performance DSP with Xilinx All Programmable Devices (Design Conference ...

High Performance DSP with Xilinx All Programmable Devices (Design Conference ...Analog Devices, Inc.

Spectra IP Core ORB - high-performance, low-latency solution for FPGA-GPP com...

Spectra IP Core ORB - high-performance, low-latency solution for FPGA-GPP com...ADLINK Technology IoT

Similar to Digital Converters Family for Software Radio (20)

The FlexTiles Development Platform offers Dual FPGA for 3D SoC Prototyping

The FlexTiles Development Platform offers Dual FPGA for 3D SoC Prototyping

High Performance DSP with Xilinx All Programmable Devices (Design Conference ...

High Performance DSP with Xilinx All Programmable Devices (Design Conference ...

Spectra IP Core ORB - high-performance, low-latency solution for FPGA-GPP com...

Spectra IP Core ORB - high-performance, low-latency solution for FPGA-GPP com...

Introducing OMAP-L138/AM1808 Processor Architecture and Hawkboard Peripherals

Introducing OMAP-L138/AM1808 Processor Architecture and Hawkboard Peripherals

DESIGN CHOICES FOR EMBEDDED REAL-TIME CONTROL SYSTEMS @ 4th FPGA Camp

DESIGN CHOICES FOR EMBEDDED REAL-TIME CONTROL SYSTEMS @ 4th FPGA Camp

[HES2014] HackRF A Low Cost Software Defined Radio Platform by Benjamin Vernoux![[HES2014] HackRF A Low Cost Software Defined Radio Platform by Benjamin Vernoux](data:image/gif;base64,R0lGODlhAQABAIAAAAAAAP///yH5BAEAAAAALAAAAAABAAEAAAIBRAA7)

![[HES2014] HackRF A Low Cost Software Defined Radio Platform by Benjamin Vernoux](data:image/gif;base64,R0lGODlhAQABAIAAAAAAAP///yH5BAEAAAAALAAAAAABAAEAAAIBRAA7)

[HES2014] HackRF A Low Cost Software Defined Radio Platform by Benjamin Vernoux

More from Bertalan EGED

More from Bertalan EGED (20)

Recently uploaded

Recently uploaded (20)

TeamStation AI System Report LATAM IT Salaries 2024

TeamStation AI System Report LATAM IT Salaries 2024

Use of FIDO in the Payments and Identity Landscape: FIDO Paris Seminar.pptx

Use of FIDO in the Payments and Identity Landscape: FIDO Paris Seminar.pptx

Streamlining Python Development: A Guide to a Modern Project Setup

Streamlining Python Development: A Guide to a Modern Project Setup

The Role of FIDO in a Cyber Secure Netherlands: FIDO Paris Seminar.pptx

The Role of FIDO in a Cyber Secure Netherlands: FIDO Paris Seminar.pptx

"Debugging python applications inside k8s environment", Andrii Soldatenko

"Debugging python applications inside k8s environment", Andrii Soldatenko

DSPy a system for AI to Write Prompts and Do Fine Tuning

DSPy a system for AI to Write Prompts and Do Fine Tuning

Passkey Providers and Enabling Portability: FIDO Paris Seminar.pptx

Passkey Providers and Enabling Portability: FIDO Paris Seminar.pptx

Transcript: New from BookNet Canada for 2024: BNC CataList - Tech Forum 2024

Transcript: New from BookNet Canada for 2024: BNC CataList - Tech Forum 2024

How AI, OpenAI, and ChatGPT impact business and software.

How AI, OpenAI, and ChatGPT impact business and software.

Ensuring Technical Readiness For Copilot in Microsoft 365

Ensuring Technical Readiness For Copilot in Microsoft 365

DevoxxFR 2024 Reproducible Builds with Apache Maven

DevoxxFR 2024 Reproducible Builds with Apache Maven

DevEX - reference for building teams, processes, and platforms

DevEX - reference for building teams, processes, and platforms

Digital Converters Family for Software Radio

- 1. Digital Converters Universal digital converter family for wide-band and phased array software radio applications Front-end BUS CH4 Sampling CLK for converters FPGA LOGIC and DSP resource SCLK OSC 10MHz CLK DRV X2/X4/X8 Sampling CLK External TRG in/out PCI HOST Interface LCLK OSC 33MHz External CLK in/out Dedicated data connection FPGA Analog driver DAC Analog preamp ADC Local CLK PCI BUS connector The members of the converter product family are based on the same digital back-end base structure. We offer two basic conversion frontend structure for wide-band and channelised applications. FIFO FPGA In wide-band the samples are available trough a FIFO for the FPGA/DSP processing elements RX CH3 FIFO Full bandwidth FPGA CFG Control BUS ADC Config EEPROM DDC FPGA Reduced bandwidth TX CH2 MCU TX Different conversion front-end configurations Analog preamp Analog driver DAC DUC FPGA NARROW-BAND (Channelized) RS-232 serial control interface I2C WIDE-BAND (Direct sampled) PROM FPGA JTAG JTAG RX Control EEPROM CH1 In narrow-band (channelised) version DDC/DUC chips are used for selecting the required channel and reduce the bandwidth Members of the converter family DCU-214: DCUMax. 4 analog I/O channels Max. 2 independent channels 1 clock I/O channel 80Msps/14bit sampling 500MHz bandwidth Xilinx Spartan II FPGA 32bit/33MHz PCI interface 133Mbyte/sec signaling rate DCU-214: DCUMax. 4 analog I/O channels Max. 4 independent digital tuner 1 clock I/O channel 80Msps/14bit sampling 500MHz bandwidth Xilinx Spartan II FPGA 32bit/33MHz PCI interface 133Mbyte/sec signaling rate DCU-304: DCUMax. 4 analog I/O channels 1 clock I/O channel 80Msps/14bit sampling 500MHz bandwidth 80 bit front-end bus frontXilinx Virtex II FPGA 64bit/66MHz PCI interface 528Mbyte/sec signaling rate DRU-304: DRUMax. 16 independent analog I/O channels 1 clock I/O channel 80Msps/14bit sampling 500MHz bandwidth Xilinx Virtex II FPGA Max. 16 independent digital tuner Software support Open application Programming Interface (API) and sample code are available for developers www.sagax.hu Matlab based time and frequency domain analiser tool Sagax, Ltd. Ltd. Haller u. 11-13. 111096 Budapest, HUNGARY