Transferencia de datos entre registros

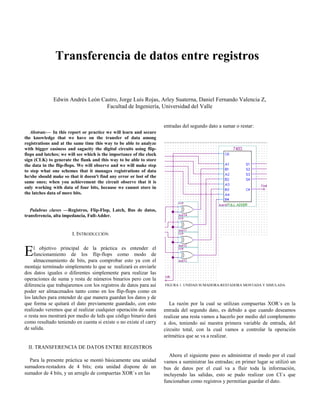

- 1. Transferencia de datos entre registros Edwin Andrés León Castro, Jorge Luís Rojas, Arley Suaterna, Daniel Fernando Valencia Z, Facultad de Ingeniería, Universidad del Valle entradas del segundo dato a sumar o restar: Abstratc— In this report or practice we will learn and secure the knowledge that we have on the transfer of data among registrations and at the same time this way to be able to analyze with bigger easiness and sagacity the digital circuits using flip- flops and latches; we will see which is the importance of the clock sign (CLK) to generate the flank and this way to be able to store the data in the flip-flops. We will observe and we will make step to step what one schemes that it manages registrations of data he/she should make so that it doesn't find any error or lost of the same ones; when you achievement the circuit observe that it is only working with data of four bits, because we cannot store in the latches data of more bits. Palabras claves —Registros, Flip-Flop, Latch, Bus de datos, transferencia, alta impedancia, Full-Adder. I. INTRODUCCIÓN E l objetivo principal de la práctica es entender el funcionamiento de los flip-flops como modo de almacenamiento de bits, para comprobar esto ya con el montaje terminado simplemente lo que se realizará es enviarle dos datos iguales o diferentes simplemente para realizar las operaciones de suma y resta de números binarios pero con la diferencia que trabajaremos con los registros de datos para así FIGURA 1. UNIDAD SUMADORA-RESTADORA MONTADA Y SIMULADA. poder ser almacenados tanto como en los flip-flops como en los latches para entender de que manera guardan los datos y de que forma se quitará el dato previamente guardado, con esto La razón por la cual se utilizan compuertas XOR´s en la realizado veremos que al realizar cualquier operación de suma entrada del segundo dato, es debido a que cuando deseamos o resta nos mostrará por medio de leds que código binario dará realizar una resta vamos a hacerlo por medio del complemento como resultado teniendo en cuenta si existe o no existe el carry a dos, teniendo así nuestra primera variable de entrada, del de salida. circuito total, con la cual vamos a controlar la operación aritmética que se va a realizar. II. TRANSFERENCIA DE DATOS ENTRE REGISTROS Ahora el siguiente paso es administrar el modo por el cual Para la presente práctica se montó básicamente una unidad vamos a suministrar las entradas; en primer lugar se utilizó un sumadora-restadora de 4 bits; esta unidad dispone de un bus de datos por el cual va a fluir toda la información, sumador de 4 bits, y un arreglo de compuertas XOR`s en las incluyendo las salidas, esto se pudo realizar con CI´s que funcionaban como registros y permitían guardar el dato.

- 2. Los primeros registros que encontramos son dos CI´s, 74374, los cuales eran dos Flip-Flops, que estaban conectados cada uno a las entradas (Las entradas corresponden a dos números binarios de 4 bits). Este par de registros permitían controlar cual dato pasa al bus, ya que sus salidas estaban directamente conectadas a él. Esta acción podía realizarse gracias a unas entradas de control (OE Output Enable), con estas entradas podíamos poner las salidas en alta impedancia, de esta manera no alimentaban al bus de datos. FIGURA 3. IMPLEMENTACIÓN DE LOS LATCHES. Estos registros guardan el dato justo antes de realizarse la suma, así los dos datos que estén guardados en cada uno de los registros van a ser sumado o restado, para guardar el dato contamos con un Enable en cada registro, así para leer un dato ubicamos el enable en “1”, en este momento el dato que está a la entrada es reflejado en la salida, y posteriormente para guardarlo ubicamos el enable en “0”; cuando el enable está en “0” no va importar el dato que tengamos en el bus en ese momento, en la salida vamos a tener el dato que leímos cuando el enable se encontró en “1” por último vez. Teniendo dos entradas de control adicional EN3 y EN4. Por último, las salidas del full-adder son llevadas a un quinto registro (74373) el cual tiene sus salidas conectadas al bus de datos, teniendo de esta manera 2 entradas de control más, un Enable (EN5) y un OE (OE5) en el registro que esta conectado a las salidas del Full-Adder. Un último registro es conectado en el bus de datos y su función básica es leer el dato FIGURA 2. IMPLEMENTACIÓN DE LOS FLIP_FLOPS. que está presente en él y en su salida visualizarlo. El circuito descrito anteriormente fue montado y simulado, En este paso tenemos ya tres entradas más de control, OC1 en total disponemos de 10 señales de control, dos datos de y OC2 con las cuales permitimos el paso de cada entrada y una entrada, dos salidas (una de ellas de 4 bits), 6 registros señal de reloj CLK. Ahora tenemos la opción de introducir un conectados al bus (3 suministrando datos y 3 leyendo), 1 full- dato o no en el bus, el siguiente paso es poder guardarlo, para adder y un CI 74ls86 (4 compuertas XOR). ello disponemos de CI´s 74373, los cuales son registros que funcionan por medio de Latches, Utilizamos dos registros para El circuito presenta una salida que corresponde al carry de ello, ubicando las salidas a cada una de las entradas de la salida del full_adder, este bit indica que la suma que se este unidad sumadora-restadora: realizando presenta un desborde, pero hay que tener en cuenta la operación que estemos realizando, puesto que al realizar restas el carry de salida puede encenderse e indicar que hay desborde en la salida, hecho que es incompatible con la operación que realizamos, debido a que el carry de salida de

- 3. un full-adder de 4 bits indica que este bit hace parte del 2A, para ello inicialmente ubicamos los EN3, EN4 y EN5 en resultado y presenta un peso de 2 4 , este problema se presenta “0” para que ningún registro este leyendo un dato, y los OC1, debido a que en realidad la operación que efectuamos al restar OC2, OC5 en “1” para que no suministremos ningún dato al es una suma, con la particularidad de que el segundo dato lo bus, seguidamente observamos que el OC6 se ubica en “0” y el hemos pasado a complemento a dos por medio del control SR, EN6 en “1” para observar el dato que esté presente en el bus. en “ 1”, a travez de todas las compuertas XOR y el carry de Para realizar la operación 2A pasamos el dato A al bus entrada. Por lo tanto este carry de salida puede ser ignorado ubicando OC1 “0”, para que el Registro 1 suministre el dato cuando realicemos restas y debe ser tenido en cuenta cuando presente en su salida; si observamos en el diagrama al realizamos una suma. momento de de habilitar este registro el dato en la salida es “0” y no A (“5”), para lograr que el registro suministre A El circuito anterior responde al siguiente circuito de flujo: debemos mover la entrada de control CLK, de tal manera que tengamos un flanco de subida: FIGURA 4.DIAGRAMA DE BLOQUES. Muestre por medio de un diagrama de tiempo el flujo de las señales de control para realizar la operación 2A±B. FIGURA 6. SEÑAL CLK. El diagrama de flujo lo podemos se obtuvo a partir de la siguiente simulación: En este momento tenemos presente A en el bus de datos. Para obtener 2A, necesitamos que los registros 3 y 4, lean el dato en el bus y lo guarden, debido a ello observamos que los EN3 y EN4 son ubicados en “1” en una fracción de tiempo. En las salidas del sumador tenemos tener 2A (revisando previamente que la entrada S/R esté en “0”) y lo debemos guardar para posteriormente sumar B. Para ello ubicamos OC1 en “1” para que el bus quede libre y ubicamos OC5 en “0” para habilitar el Registro 5, para este lapso de tiempo el valor observado en la salida puede variar de forma extraña debido a que el EN5 aún no ha sido habilitado para que suministre el dato al bus. El EN5 es ubicado en “1” temporalmente para que pase el dato al bus y quede guardado en la salida de este registro. Observamos que en la salida tenemos presente 2A (“10”) y que el EN3 es ubicado en “1” para leer y guardar el dato en el registro 3, el OC5 se ubica en “0” para tener el bus libre nuevamente. La siguiente fracción del diagrama de flujo muestra la secuencia presente para que al dato guardado se le sume o reste B: FIGURA 5. FRACCIÓN DEL DIAGRAMA DE FLUJO. En el anterior diagrama tenemos como valores de entrada A=5 y B=13, para realizar en esta primera parte la operación

- 4. complemento a dos y para conocer su magnitud debemos pasarlo a complemento a dos, por lo tanto: 1310 11012 11012C 00112 00112 310 Por último cabe anotar que el Cout tuvo valores indeterminados durante el tiempo en que los dos registros antes del sumador no habían suministrado un dato exacto, debido a que se debe tener con certeza que valores hay presentes en las entradas del sumador para realizar la operación. Indique el error que se presenta en el siguiente circuito de flujo de datos y la forma de corregirlo FIGURA 7. SEGUNDA FRACCIÓN DEL DIAGRAMA DE FLUJO. para que se puedan desarrollar las operaciones de la práctica: De la figura 7 observamos que el primer paso es ubicar el OC2 en “0” para el dato B este presente en el bus, observamos que este dato había sido guardado en el registro cuando suministramos el dato A al bus, seguidamente leemos y guardamos el dato B en el registro 4, ubicando temporalmente el EN4 en “1” temporalmente y observamos un cambio en la salida Cout indicando que la suma ha producido un desborde, en este momento podemos decidir si queremos sumar o restar. Para observar finalmente el resultado ubicamos el OC5 en “0” y el EN5 en “1”, en la salida observamos como resultado un “7” y debido a que el Cout está en “1” debemos sumar 16, lo que nos da como resultado “23”, que es lo que se esperaba. Aprovechando que tenemos 2A y B guardados en las entradas del sumador nos aseguramos de tener el EN5 en “1” y modificar el S/R para observar la resta: FIGURA 9. CIRCUITO DE FLUJO INCORRECTO. El error se produce en la realimentación que se presenta en el sumador hacia el REG 3, porque para que halla un flujo de datos tienen que pasar obligatoriamente por el REG 4, y este hecho no asegura que resultado se tome del sumador, para luego ser guardado en el REG 3, por lo tanto no es posible guardar con plena seguridad un dato en el REG 3, para corregir dicho error lo ideal es conectar el REG 3 al bus de datos, pero caeríamos en el circuito propuesto para la práctica. Una alternativa presente es tomar la salida del REG 4 hacia el FIGURA 8. SUMA – RESTA DE 2A Y B. REG 3, considerando como problema el hecho de que hay que ser cauteloso en la secuencia en que vamos a ingresar un dato, así de esta manera el primer dato que se desee guardar debe Se observa que al momento de ubicar S/R en “1” el hacerse al REG 3 pasando previamente por el REG 4. resultado cambia a “13”, hay que tener en cuenta que el presente resultado ha sido suministrado en complemento a dos debido a la lógica con la cual se ha realizado la resta. Por lo tanto este resultado corresponde a un número negativo en

- 5. 9º Quitar dato B del bus. 10º Leer y ubicar el resultado 7+12 en el bus. 11º Restar 12 a 7. III. INVESTIGACIÓN Describa el funcionamiento de los FLIP-FLOPS. Que tipos de F.F existen, cuales son sus principales características, comercialmente como se conocen (referencias para comprarlos de acuerdo al tipo de F.F). 1. FLIP-FLOP. FIGURA 10. CIRCUITO CORREGIDO. Un biestable, también llamado flip-flop , es un multivibrador capaz de permanecer en un estado Indicar cada uno de los pasos (cambio en posiciones determinado o por el contrario durante un tiempo de los switch) necesarios para realizar la suma 7+12 y indefinido, es decir, que permanece indefinidamente en la resta 7-12. uno de sus dos estados posibles aunque haya desaparecido la señal de excitación que provoco su Para los pasos de la operación vamos a dejar las señales transición al estado actual; debido a su amplia OC6 en “0” y EN6 en “1”. Este hecho solamente indica que utilización, los F.F se han convertido en un elemento vamos a observar el dato que está presente en el bus de datos en todo momento: fundamental dentro de los circuitos secuenciales. Esta característica es ampliamente utilizada en A= 0111, B=1100 electrónica digital para memorizar información. El paso de un estado a otro se realiza variando sus entradas, PASO POSICIÓN Todos los circuitos digitales utilizan datos binarios para CLK EN3 EN4 EN5 OC1 OC2 OC5 S/R funcionar correctamente, los circuitos están diseñados 1º 0 0 0 0 0 1 1 0 para contar, sumar, separar, etc. los datos según nuestras 2º 1 0 0 0 0 1 1 0 necesidades, pero por el tipo de funcionamiento de las 3º 1 1 0 0 0 1 1 0 compuertas digitales, los datos presentes en las salidas de 4º 1 0 0 0 0 1 1 0 las mismas, cambian de acuerdo con sus entradas, y no 5º 1 0 0 0 1 1 1 0 hay manera de evitarlo, si las entradas cambian, las 6º 1 0 0 0 1 0 1 0 salidas lo harán también; Dependiendo del tipo de dichas 7º 1 0 1 0 1 0 1 0 entradas los biestables se dividen en: 8º 1 0 0 0 1 0 1 0 1 0 0 0 1 1 1 0 Asíncronos: Sólo tienen entradas de control. El 9º 10º 1 0 0 1 1 1 0 0 más empleado es el biestable RS. RESULTADO 7+12 Síncronos: Además de las entradas de control 11º 1 0 0 1 1 1 0 1 posee una entrada de sincronismo o de reloj. Si RESULTADO 7-12 las entradas de control dependen de la de TABLA 1. POSICIONES EN LOS SWITCH. sincronismo se denominan síncronas y en caso contrario asíncronas. Por lo general, las entradas Donde cada paso corresponde a las siguientes acciones: de control asíncronas prevalecen sobre las 1º Ubicar dato A en el bus. síncronas. 2º Guardar datos A y B en los registros 1 y 2 La entrada de sincronismo puede ser activada por nivel respectivamente. (alto o bajo) o por flanco (de subida o de bajada). Dentro 3º Leer dato A en el REG 3. de los biestables síncronos activados por nivel están los 4º Guardar dato A en el REG 3. tipos RS y D, y dentro de los activos por flancos los tipos 5º Quitar dato A del bus. JK, T y D. 6º Ubicar dato B en el bus. 1.2 TIPOS DE FLIP-FLOPS: 7º Leer dato B en el REG 4 1.2.1 FLIP-FLOP S-R 8º Guardar dato B en el REG 4.

- 6. Dispositivo de almacenamiento temporal de dos estados ejemplo de un biestable síncrono a partir de una asíncrona, (alto y bajo), cuyas entradas principales, R y S, a las que junto con su esquema normalizado: debe el nombre, permiten al ser activadas: Su tabla de verdad es la siguiente: R: El borrado (reset en inglés), puesta a 0 ó nivel bajo de la salida. C R S Q Q S: El grabado (set en inglés), puesta a 1 ó nivel alto de la salida. 0 X X Q0 Q0 Si no se activa ninguna de las entradas, el biestable permanece en el estado que poseía tras la última 1 0 0 Q0 Q0 operación de borrado o grabado. En ningún caso deberían activarse ambas entradas a la vez, ya que esto provoca que 1 0 1 1 0 las salidas directa (Q) y negada (Q') queden con el mismo valor: a bajo, si la báscula está construida con puertas 1 1 0 0 1 NO-O (NOR), o a alto, si con puertas NO-Y (NAND). El problema de que ambas salidas queden al mismo estado 1 1 1 INDEFINIDO está en que al desactivar ambas entradas no se podrá TABLA 2. TABLA DE VERDAD S-R SINCRONO determinar el estado en el que quedaría la salida. Por eso, 1.2.2 FLIP-FLOP D. en las tablas de verdad, la activación de ambas entradas se Dispositivo de almacenamiento temporal de dos estados contempla como caso no deseado (INDETERMINADO). (alto y bajo), cuya salida adquiere el valor de la entrada D cuando se activa la entrada de sincronismo, C. En función del modo de activación de dicha entrada de sincronismo, existen dos tipos de biestables D: Activo por nivel (alto o bajo), también denominado registro o cerrojo (latch en inglés). Activo por flanco (de subida o de bajada). FIGURA 11. SÍMBOLO DEL FLIP-FLOP S-R 1.2.1.1 FLIP-FLOP S-R ASINCRONO Sólo posee las entradas R y S. Se compone internamente de dos puertas lógicas NO-Y o NO-O, Su tabla de verdad es la siguiente (Q representa el estado actual de la salida y q el estado anterior a la última activación): R S Q FIGURA 12. SÍMBOLO DEL FLIP-FLOP D Q A diferencia de los FF tipo J-K, el FF tipo "D" (Datos, 0 0 Q0 Q0 Data) sólo cuneta con una entrada para hacer el cambio de las salidas. A cada pulso del reloj; El circuito opera de la siguiente 0 1 1 0 forma: cuando hay un flanco de subida en el puerto de entrada clk, y la entrada d vale '1', entonces la salida q pasa a tomar el 1 0 0 1 valor de d. Cuando clk está a nivel bajo, la entrada d se 1 1 INDEFINI encuentra deshabilitada, manteniendo q el valor anterior. Esta DO es la base de su operatividad como memoria TABLA 2. TABLA DE VERDAD S-R ASINCRONO La ecuación característica del biestable D que describe su comportamiento es: 1.2.1.2 FLIP-FLOP S-R SÍNCRONO. Además de las entradas R y S, posee una entrada C de D CLK Q Q ´ sincronismo cuya misión es la de permitir o no el cambio de estado del biestable. En la siguiente figura se muestra un

- 7. 0 ↑ 0 1 1 ↑ 1 0 X 0 Q0 Q0 X 1 Q0 Q0 TABLA 2. TABLA DE VERDAD FLIP-FLOP D FIGURA 12. SÍMBOLO DEL FLIP-FLOP J-K 1.2.3 FLIP-FLOP J-K. 1.3 TRANSFERENCIA DE DATOS ENTRE FLIP-FLOPS El flip-flop JK se emplea para eliminar la incertidumbre cuando las señales de entrada J=K=1, en el caso del flip- El uso mas común que se le dan a los flip-flops es el flop RS, esta asignación de los valores de las entradas de almacenamiento de datos o información. Estos datos estaban prohibidas en el caso del RS, sin embargo aquí en generalmente se almacenan en grupos de flip-flops que el JK, se dará la función basculamiento. El flip-flop JK es son llamados registros. La operación de más frecuencia el más completo de, los flip-flop que se emplean. Tiene dos en los datos almacenados en los flip-flops o registros es entradas J y K, similares a las entradas S y R de un flip- la transferencia. Como por ejemplo la transferencia de datos entre los flip-flops S-C, J-K y D es la siguiente: flop RS. La estrada J realiza la función set y la entrada K la función reset. La principal diferencia entre ambos es que J y K pueden valer uno simultáneamente, a diferencia del flip-flop RS, en este caso la salida cambia de estado, pasando a valer lo contrario de lo que valía antes. CLK J K Q Q´ 0 X X Q0 Q0 1 X X Q0 Q0 FIGURA 13 FLIP-FLOP S-C ↑ 0 0 Q0 Q0 ↑ 0 1 0 1 ↑ 1 0 1 0 ↑ 1 1 Q0 Q0 TABLA 2. TABLA DE VERDAD FLIP-FLOP J-K FIGURA 14 FLIP-FLOP J-K 1.3 FLIP-FLOPS COMERCIALES 74LS73: Dual JK con disparo de flanco negativo. 74LS74: Dual JK con disparo de flanco positivo 74LS173: 4 registros tipo D con salida tipo 3-estados 74LS174: 6 flip-flops tipo D (Fairchild). 74LS273: 8 registros tipo D con borrado 74LS373: 8 registros D tipo Latch, con salidas de 3 estados 74LS374: 8 registros D tipo Latch, con salidas de 3 estados FIGURA 15 FLIP-FLOP D

- 8. Estas transferencias que se dan a través del Bus de Datos 2. LATCH. son gobernadas por varios dispositivos y métodos, de los cuales el Controlador PCI, "Peripheral Component Interconnect", Interconexión de componentes Periféricos, es uno de los principales. Su trabajo equivale, Un latch es un dispositivo asíncrono que permite simplificando mucho el asunto, a una central de semáforos almacenar un bit. De acuerdo a l estado de las entradas, él para el tráfico en las calles de una ciudad. puede ejecutar varias acciones, cargar un bit, almacenarlo o simplemente borrarlo. De esta manera tenemos una 3.1.2 BUS DE DIRECCIONES especie de memoria RAM. El término asíncrono indica que no es necesario que el latch este sincronizado con una El bus de dirección (o direcciones) es un bus del señal de reloj externa, este funciona cada vez que cambia microprocesador totalmente independiente al bus de datos la entrada. Existen varios tipos de latch, entre los más donde se establece la dirección de memoria del dato en conocidos están el SR y el D. tránsito. 3. BUS DE DATOS. El bus de dirección consiste en el conjunto de líneas eléctricas necesarias para establecer una dirección. Esto En la arquitectura de computadores, un bus puede depende de la cantidad de memoria direccionable. Por conectar lógicamente varios periféricos (o computadores) ejemplo, para direccionar una memoria de 256 palabras, sobre el mismo conjunto de cables. Bus es una palabra son necesarias al menos 8 líneas. Adicionalmente pueden inglesa que significa "transporte". Aplicada a la ser necesarias líneas de control para señalar cuando la informática, se relaciona con la idea de las transferencias dirección está disponible en el bus. Esto depende del internas de datos que se dan en un sistema computacional diseño del propio bus. en funcionamiento. En el bus todos los nodos reciben los datos aunque no se dirijan a todos éstos, los nodos a los Algunos diseños utilizan líneas eléctricas multiplexadas que no van dirigidos los datos simplemente los ignoran. para el bus de dirección y el bus de datos. Esto significa Los primeros buses de computadoras eran literalmente que un mismo conjunto de líneas eléctricas se comportan buses eléctricos paralelos con múltiples conexiones. Hoy unas veces como bus de dirección y otras veces como bus en día el término es usado para cualquier arreglo físico de datos, pero nunca al mismo tiempo. Una línea de control que provea la misma funcionalidad lógica que un bus permite discernir cual de las dos funciones está activa. eléctrico paralelo. Los buses modernos pueden usar tanto conexiones paralelas como en serie, y pueden ser 3.1.3 BUS DE CONTROL cableados en topología multidrop o en daisy chain, o conectados por hubs switcheados, como el caso del USB. Gobierna el uso y acceso a las líneas de datos y de direcciones. Como estas líneas están compartidas por todos los componentes tiene que proveerse de determinados 3.1 CLASES DE BUSES. mecanismos que controlen su utilización. Las señales de Hay tres clases de buses: bus de datos, bus de control transmiten tanto ordenes como información de direcciones y bus de control. temporización entre los módulos del sistema. 3.1.1 BUS DE DATOS IV. CONCLUSIONES Ppermite significar la idea de las transferencias internas de datos que se dan en un sistema computacional Dentro de la presente práctica cabe anotar que se logró en funcionamiento. En el bus todos los nodos reciben los comprender y afianzar aún más conceptos correspondientes a datos aunque no se dirijan a todos los nodos, los nodos a la lógica combinatoria, como es el caso de una unidad los que no van dirigidos simplemente lo ignoran. sumadora-restadora, de donde se pudo comprender y verificar el modo y funcionamiento de esta. De la cual podemos afirmar El primero mueve los datos entre los dispositivos del que: hardware: de Entrada como el teclado, el escáner, el Mouse, etc.; de salida como la Impresora, el Monitor o la - El carry de salida tiene un peso de 2 n para un tarjeta de Sonido; y de Almacenamiento como el Disco sumador de n bits Duro, el Diskette o la Memoria-Flash.

- 9. - Al usar la unidad para restas podemos encontrar que - Cuando trabajamos en modo nivel tenemos la opción de en una resta simple se puede presentar un desborde leer el dato mientras mantenemos el nivel y guardarlo debido a que usamos complemento a dos. cuando se cambie. - Cuando realizamos restas de tal manera que el resultado es negativo, vamos encontrar este en El uso de compuertas triestados, FF D, modo nivel y modo complemento a dos y para conocer su magnitud flanco, permitió el uso de mandos o señales de control que debemos complementarlo a dos. podían ser manipuladas para hacer uso del circuito y permitir - El hecho de que el carry de salida se encienda cuando realizar las operaciones por medio de registros (utilizando los realizamos algunas restas y que dichas restas se enable o señales de reloj) para guardar memoria, realizar la presenten en complemento a dos siendo el resultado operación requerida (S/R de la unidad), manejar el paso de negativo, hace necesario que cuando al operar la datos (utilizando las compuertas triestados a travez de los unidad, tener presente estas consideraciones para “Output Control”) y evitar perdida de información en un bus interpretar el resultado, hecho por el cual puede no de datos. ser viable. Por último, al tener todo en conjunto permitió ver y Por otro lado encontramos que se pudo establecer un flujo de establecer las diferencias y funciones de los elementos ya datos a través de un bus por medio de registros, para ello se mencionados para manipular y transferir datos y todo esto tuvieron en cuenta FLIP-FLOPS D (modo flanco y modo gracias a un bus de datos del cual también se pudo comprender nivel). Del FLIP-FLOP D podemos afirmamos lo siguiente: y establecer utilidades para el flujo de información. - Cuando se habla de modo nivel quiere decir que la salida del FF D es totalmente transparente al dato V. OBSERVACIONES Y COMENTARIOS cuando la señal de reloj, o enable para este caso, se encuentra sobre un nivel lógico (“1”), Observaciones : El laboratorio en el momento de su - Cuando se habla de modo flanco encontramos que el desarrollo resultó ser muy practico ya que se debía de realizar FF D solo lee el dato de entrada y lo ubica en la una acción cualquiera (Operación del circuito) el cual salida solo cuando se presenta un flanco de subida o demostraba la preparación y el entendimiento del solo flanco de bajada. comportamiento del circuito que se montó previamente. - Un flaco de subida en una señal se presenta cuando la señal pasa del nivel bajo al alto. El flanco de Comentarios : De pronto, por el peso académico que bajada corresponde al caso inverso. representa el sexto semestre, el tiempo que se necesita disponer para los montajes es bastante y por ende complica la Para la correcta utilización del bus se hizo necesario utilizar elaboración de los circuitos. las compuertas triestados debido a que este tipo de compuertas permite controlar el paso de un dato a travez de ella. Estas IV. BIBLIOGRAFÍA compuertas estan ubicadas dentro de los CI´s utilizados y controlaban el paso de cada dato al bus. Por ello podemos ver la utilidad de las mencionadas compuertas en la transferencia [1] John P. Hayes. "Introducción al Diseño Lógico Digital". de datos ya que permite utilizar una vía directa para que dos o Addison-Wesley Iberoamericana; más integrados puedan enviar información a travez de ella, [2] www.datasheetcatalog.com uno a la vez, sin la necesidad de implementar vías [3] Jhon Wakerly. “Diseño Digital, Principios y practicas”. independientes. Prentice – Hall 3ra Edición. [4] http://proton.ucting.udg.mx/~zoad/programas/electfile El hecho de que los FF funcionen con una señal de reloj [5] http://oswagar.galeon.com/enlaces1111733.html (modo nivel o flanco), permitió aprovechar este hecho para usarlos como elementos para guardar memoria y ser usados como registros, de lo anterior podemos diferenciar que: - Cuando trabajamos en modo flanco tomamos el dato que está a la entrada una vez se ha dado la orden (puede ser mediante un pulso, o un cambio en la posición de un dip- switch) y el dato queda guardado instantáneamente