input output Organization

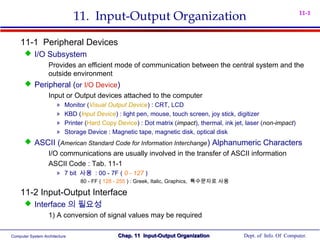

- 1. Computer System Architecture Dept. of Info. Of Computer.Chap. 11 Input-Output OrganizationChap. 11 Input-Output Organization 11-1 11. Input-Output Organization 11-1 Peripheral Devices I/O Subsystem Provides an efficient mode of communication between the central system and the outside environment Peripheral (or I/O Device) Input or Output devices attached to the computer » Monitor (Visual Output Device) : CRT, LCD » KBD (Input Device) : light pen, mouse, touch screen, joy stick, digitizer » Printer (Hard Copy Device) : Dot matrix (impact), thermal, ink jet, laser (non-impact) » Storage Device : Magnetic tape, magnetic disk, optical disk ASCII (American Standard Code for Information Interchange) Alphanumeric Characters I/O communications are usually involved in the transfer of ASCII information ASCII Code : Tab. 11-1 » 7 bit 사용 : 00 - 7F ( 0 - 127 ) 80 - FF ( 128 - 255 ) : Greek, Italic, Graphics, 특수문자로 사용 11-2 Input-Output Interface Interface 의 필요성 1) A conversion of signal values may be required

- 2. Computer System Architecture Dept. of Info. Of Computer.Chap. 11 Input-Output OrganizationChap. 11 Input-Output Organization 11-2 2) A synchronization mechanism may be needed » The data transfer rate of peripherals is usually slower than the transfer rate of the CPU 3) Data codes and formats in peripherals differ from the word format in the CPU and Memory 4) The operating modes of peripherals are different from each other » Each peripherals must be controlled so as not to disturb the operation of other peripherals connected to the CPU Interface Special hardware components between the CPU and peripherals Supervise and Synchronize all input and output transfers I/O Bus and Interface Modules : Fig. 11-1 I/O Bus » Data lines » Address lines » Control lines Interface Modules : 주로 VLSI Chip 사용 » SCSI (Small Computer System Interface) » IDE (Integrated Device Electronics) » Centronics » RS-232 » IEEE-488 (GPIB) In t e r f a c e K e y b o a r d a n d d is p la y t e r m i n a l In t e r f a c e M a g n e t ic t a p e I n t e r f a c e M a g n e t i c d i s k I n t e r f a c e P r in t e r P r o c e s s o r D a t a C o n t r o l A d d r e s s I/ O b u s

- 3. Computer System Architecture Dept. of Info. Of Computer.Chap. 11 Input-Output OrganizationChap. 11 Input-Output Organization 11-3 I/O command : 8251 SIO 예제 » Control Command » Status Command » Input Command » Output Command I/O Bus versus Memory Bus Computer buses can be used to communicate with memory and I/O » 1) Use two separate buses, one for memory and the other for I/O : Fig. 11-19, p. 421 I/O Processor » 2) Use one common bus for both memory and I/O but have separate control lines for each : Isolated I/O or I/O Mapped I/O IN, OUT : I/O Instruction MOV or LD : Memory read/write Instruction » 3) Use one common bus for memory and I/O with common control lines : Memory Mapped I/O MOV or LD : I/O and Memory read/write Instruction Intel, Zilog Motorola * Control Lines I/O Request, Mem Request, Read/Write * Control Lines Read/Write

- 4. Computer System Architecture Dept. of Info. Of Computer.Chap. 11 Input-Output OrganizationChap. 11 Input-Output Organization 11-4 Example of I/O Interface : Fig. 11-2 4 I/O port : Data port A, Data port B, Control, Status » 비교 : 8255 PIO ( port A, B, C, Control/Status ) Address Decode : CS, RS1, RS0 11-3 Asynchronous Data Transfer Synchronous Data Transfer All data transfers occur simultaneously during the occurrence of a clock pulse Registers in the interface share a common clock with CPU registers Asynchronous Data Transfer Internal timing in each unit (CPU and Interface) is independent Each unit uses its own private clock for internal registers 따라서 Asynchronous 에서는 언제 data transfer 가 발생하는지 알리는 신호가 필요하며 Strobe 와 Handshake 방식을 사용함 T im in g a n d C o n t ro l C S W R R D R S 0 R S 1 B u s b u f f e r s S t a t u s r e g is t e r C o n t ro l r e g is t e r P o r t B r e g is t e r P o rt A r e g is t e rB id ir e c t io n a l d a t a b u s S t a t u s T o C P U I/ O r e a d R e g is t e r s e le c t C h ip s e le c t I/ O w r it e I/ O d a t a I/ O d a t a C o n t r o l T o I/ O d e v ic e Internalbus C S R S 0 R S 1 R e g is t e r s e le c t e d N o n e : d a t a b u s in h ig h - im p e d a n c e P o r t A r e g is t e r P o r t B r e g is t e r C o n t r o l re g is t e r S t a t u s r e g is t e r 0 1 1 1 1 1 0 0 1 1 0 1 0 × ×

- 5. Computer System Architecture Dept. of Info. Of Computer.Chap. 11 Input-Output OrganizationChap. 11 Input-Output Organization 11-5 Strobe : Control signal to indicate the time at which data is being transmitted 1) Source-initiated strobe : Fig. 11-3 2) Destination-initiated strobe : Fig. 11-4 Disadvantage of strobe method » Destination 이 Data 를 아무 이상 없이 잘 가져 갔는지 알 수가 없다 . » 따라서 Handshake method 를 사용하여 Data 전송을 확인함 S o u r c e u n it D e s t in a t io n u n it ( a ) B lo c k d ia g r a m V a lid d a t a D a t a S t r o b e ( b ) T im in g d ia g r a m D a t a b u s S t r o b e S o u r c e u n it D e s t in a t io n u n it ( a ) B lo c k d ia g r a m V a lid d a t a D a t a S t r o b e ( b ) T im in g d ia g r a m D a t a b u s S t r o b e Fig. 11-3 Source-initiated strobe Fig. 11-4 Destination-initiated strobe

- 6. Computer System Architecture Dept. of Info. Of Computer.Chap. 11 Input-Output OrganizationChap. 11 Input-Output Organization 11-6 Handshake : Agreement between two independent units 1) Source-initiated handshake : Fig. 11-5 2) Destination-initiated handshake : Fig. 11-6 Timeout : If the return handshake signal does not respond within a given time period, the unit assumes that an error has occurred. S o u r c e u n i t D e s t i n a t i o n u n i t ( a ) B l o c k d i a g r a m V a l i d d a t a D a t a ( b ) T i m i n g d i a g r a m D a t a b u s D a t a v a l i d D a t a a c c e p t e d D a t a v a l i d D a t a a c c e p t e d P l a c e d a t a o n b u s E n a b le d a t a v a l i d . D is a b l e d a t a v a l i d I n v a l i d a t e d a t a o n b u s A c c e p t d a t a f r o m b u s E n a b l e d a t a a c c e p t e d D i s a b l e d a t a a c c e p t e d R e a d y t o a c c e p t d a t a ( i n i t i a l s t a t e ) ( c ) S e q u e n c e o f e v e n t s S o u r c e u n i t D e s t i n a t i o n u n i t Fig. 11-5 Source-initiated handshake S o u r c e u n i t D e s t i n a t i o n u n i t ( a ) B l o c k d i a g r a m V a l i d d a t a ( b ) T i m i n g d i a g r a m D a t a b u s D a t a v a l id R e a d y f o r d a t a D a t a v a l i d D a t a b u s P l a c e d a t a o n b u s E n a b l e d a t a v a l i d . D i s a b l e d a t a v a l i d I n v a li d a t e d a t a o n b u s ( i n i t i a l s t a t e ) A c c e p t d a t a f r o m b u s D i s a b le r e d a y f o r d a t a R e a d y t o a c c e p t d a t a . E n a b l e r e a d y f o r d a t a ( c ) S e q u e n c e o f e v e n t s R e a d y f o r d a t a S o u r c e u n it D e s t in a t i o n u n i t Fig. 11-6 Destination-initiated handshake

- 7. Computer System Architecture Dept. of Info. Of Computer.Chap. 11 Input-Output OrganizationChap. 11 Input-Output Organization 11-7 Asynchronous Serial Transfer Synchronous transmission : Sec. 11-8 » The two unit share a common clock frequency » Bits are transmitted continuously at the rate dictated by the clock pulses Asynchronous transmission : Fig. 11-7 » Special bits are inserted at both ends of the character code » Each character consists of three parts : 1) start bit : always “0”, indicate the beginning of a character 2) character bits : data 3) stop bit : always “1” Asynchronous transmission rules : When a character is not being sent, the line is kept in the 1-state The initiation of a character transmission is detected from the start bit, which is always “0” The character bits always follow the start bit After the last bit of the character is transmitted, a stop bit is detected when the line returns to the 1-state for at least one bit time 1 1 11 0000 S t a r t b i t C h a r a c t e r b i t s S t o p b i t

- 8. Computer System Architecture Dept. of Info. Of Computer.Chap. 11 Input-Output OrganizationChap. 11 Input-Output Organization 11-8 Baud Rate : Data transfer rate in bits per second » 10 character per second with 11 bit format = 110 bit per second UART (Universal Asynchronous Receiver Transmitter) : 8250 UART (Universal Synchronous/Asynchronous Receiver Transmitter) : 8251 Asynchronous Communication Interface : Fig. 11-8 예제 ) 8250 SIO » 80 : Data Write/Read (Transmit/Receive) » 81 : Control Write/ Status Read A0 = RS (register select) Double Buffered (in transmit register) » New character can be loaded as soon as the previous one starts transmission 3 possible errors (in status register) » 1) parity error Even or Odd parity error » 2) framing error right number of stop bits is not detected at the end of the received character » 3) overrun error CPU does not read the character from the receiver register before the next one is available T im in g a n d C o n t r o l C S W R R D R S B u s b u f f e r s S t a t u s r e g i s t e r C o n t r o l r e g i s t e r R e c e iv e r r e g i s t e r T r a n s m it t e r r e g i s t e rB i d ir e c t i o n a l d a t a b u s I / O r e a d R e g is t e r s e le c t C h i p s e l e c t I / O w r it e Internalbus C S R S R e g i s t e r s e le c t e d N o n e : d a t a b u s in h ig h - im p e d a n c e T r a n s m it t e r r e g is t e r 0 1 1 1 1 1 0 1 0 × S h if t r e g is t e r S h if t r e g is t e r T r a n s m i t t e r c o n t r o l a n d c l o c k R e c e i v e r c o n t r o l a n d c l o c k T r a n s m it d a t a T r a n s m it t e r c lo c k R e c e iv e r d a t a R e c e iv e r c lo c k R D W R R D W R O p e r a t io n × C o n t r o l r e g is t e r R e c e iv e r r e g is t e r S t a t u s r e g is t e r

- 9. Computer System Architecture Dept. of Info. Of Computer.Chap. 11 Input-Output OrganizationChap. 11 Input-Output Organization 11-9 First-In, First-Out (FIFO) Buffer : Fig. 11-9 Fi : F4 = 1 = Output ready » 1 = valid data in Ri » 0 = no valid data in Ri Fi’ : F1’ = 1 = Input ready » 1 = empty in Ri » 0 = full in Ri Data Input » 1) Input ready = 1 (F1’ = 1) 일 때 Insert = 1 로 하여 데이터 입력 » 2) AND gate 의 출력이 1 이 되면서 입력 데이터가 R1 으로 전송된다 . » 3) S = 1 이 되면 F/F 이 set 되어 F1 = 1 이 된다 . » 4) R2 가 비어 있으면 F2’ = 1 이고 F1 = 1 과 AND gate 를 통과하면 R1 의 내용이 R2 로 전송된다 . Data Output » 1) Output ready = 1 (F4 = 1) 일 때 Delete = 1 로 하여 데이터 출력 » 2) Delete = 1 이면 R = 1 (S = 0) 이 되어 Output ready = 0 (F4 = 0) 으로 된다 . » 3) Delete 가 1 에서 0 이 되면 3 input AND gate 의 출력이 1 이 되면서 R3 가 R4 로 전송되면서 S = 1 이 되어 다시 Output ready = 1 로 된다 . 4 - b it r e g is t e r S R F 1 F '1 4 - b it r e g is t e r S R F 4 F '4 4 - b it r e g is t e r S R F 2 F '2 4 - b it r e g is t e r S R F 3 F '3 D a t a in p u t D a t a o u t p u t C lo c k C lo c k C lo c k C lo c k In s e r t M a s t e r c le a r In p u t r e a d y D e le t e O u t p u t r e a d y R 1 R 4R 3R 2 초기 상태 F1 = 0 F1’ = 1 S = 0

- 10. Computer System Architecture Dept. of Info. Of Computer.Chap. 11 Input-Output OrganizationChap. 11 Input-Output Organization 11-10 11-4 Modes of Transfer Data transfer to and from peripherals 1) Programmed I/O : in this section 2) Interrupt-initiated I/O : in this section and sec. 11-5 3) Direct Memory Access (DMA) : sec. 11-6 4) I/O Processor (IOP) : sec. 11-7 Example of Programmed I/O : Fig. 11-10, 11-11 Interrupt-initiated I/O 1) Non-vectored : fixed branch address 2) Vectored : interrupt source supplies the branch address (interrupt vector) In t e r f a c e C P U I/ O d e v ic e D a t a r e g is t e r S t a t u s r e g is t e r F D a t a b u s I/ O w r it e I/ O r e a d A d d r e s s b u s D a t a a c c e p t e d D a t a v a lid I/ O b u s F = F la g b it R e a d s t a t u s r e g is t e r C h e c k f la g b it R e a d d a t a r e g is t e r T r a n s f e r d a t a t o m e m o r y C o n t in u e w it h p r o g r a m F la g O p e r a tio n c o m p le te ? = 0 = 1 y e s n o

- 11. Computer System Architecture Dept. of Info. Of Computer.Chap. 11 Input-Output OrganizationChap. 11 Input-Output Organization 11-11 Software Considerations I/O routines » software routines for controlling peripherals and for transfer of data between the processor and peripherals I/O routines for standard peripherals are provided by the manufacturer (Device driver, OS or BIOS) I/O routines are usually included within the operating system I/O routines are usually available as operating system procedures ( OS or BIOS function call) 11-5 Priority Interrupt Priority Interrupt Identify the source of the interrupt when several sources will request service simultaneously Determine which condition is to be serviced first when two or more requests arrive simultaneously 처리 방법 : » 1) Software : Polling » 2) Hardware : Daisy chain, Parallel priority

- 12. Computer System Architecture Dept. of Info. Of Computer.Chap. 11 Input-Output OrganizationChap. 11 Input-Output Organization 11-12 Polling Identify the highest-priority source by software means » One common branch address is used for all interrupts » Program polls the interrupt sources in sequence » The highest-priority source is tested first Polling priority interrupt 의 단점 » If there are many interrupt sources, the time required to poll them can exceed the time available to service the I/O device » 따라서 Hardware priority interrupt 를 사용 Daisy-Chaining : Fig. 11-12 D e v i c e 1 P I P O D e v i c e 3 P I P O D e v i c e 2 P I P O T o n e x t D e v i c e C P U I N T I N T A C K I n t e r r u p t r e q u e s t I n t e r r u p t a c k n o w l e d g e P r o c e s s o r d a t a b u s V A D 1 V A D 3V A D 2 “1” “1” “0”Device 2 Interrupt Request

- 13. Computer System Architecture Dept. of Info. Of Computer.Chap. 11 Input-Output OrganizationChap. 11 Input-Output Organization 11-13 One stage of the daisy-chain priority arrangement : Fig. 11-13 No interrupt request Invalid : interrupt request, but no acknowledge No interrupt request : Pass to other device (other device requested interrupt ) Interrupt request S Q R V e c t o r a d d r e s s D e la y E n a b le R F P I P r io r it y in I n t e r r u p t r e q u e s t f r o m d e v ic e O p e n - c o lle c t o r in v e r t e r In t e r r u p t r e q u e s t t o C P U P r io r it y o u t P O V A D R FP I P O E n a b le 0 0 1 1 0 0 1 1 0 0 1 1 0 0 0 1 INTACK INT

- 14. Computer System Architecture Dept. of Info. Of Computer.Chap. 11 Input-Output OrganizationChap. 11 Input-Output Organization 11-14 Parallel Priority Priority Encoder 를 이용한 Parallel Priority : Fig. 11-14 » Interrupt Enable F/F (IEN) : set or cleared by the program » Interrupt Status F/F (IST) : set or cleared by the encoder output Priority Encoder Truth Table : Tab. 11-2 » I0 가 제일 높은 우선 순위 Interrupt Cycle At the end of each instruction cycle, CPU checks IEN and IST if both IEN and IST equal to “1” CPU goes to an Instruction Cycle » Sequence of microoperation during Instruction Cycle 0 3 2 1 0 3 2 1 P rio rit y e n c o d e r I0 I2 I3 I1 d is k K e y b o a rd R e a d e r P rin t e r In t e r ru p t re g is t e r y 0 0 0 0 0 0 x IS TIE N V A D t o C P U E n a b le In t e rru p t t o C P U IN T A C K f ro m C P U M a s k re g is t e r ninstructionextFetchto 0 1 ][ 1 Go IEN VADPC INTACK PCSPM SPSP ← ← ← ← −← : Decrement stack point : Push PC into stack : Enable INTACK : Transfer VAD to PC : Disable further interrupts Branch to ISR

- 15. Computer System Architecture Dept. of Info. Of Computer.Chap. 11 Input-Output OrganizationChap. 11 Input-Output Organization 11-15 Software Routines CPU 가 현재 main program 의 749 번지를 실행 도중에 KBD interrupt 발생 KBD service program 의 255 번지를 실행 도중에 DISK interrupt 발생 J M P D I S K M a in p r o g r a m J M P K B D J M P R D R J M P P D R S t a c k 7 5 0 2 5 6 M e m o r y 0 3 2 1 A d d r e s s 7 5 0 P r o g r a m t o s e r v i c e m a g n e t ic d i s k P r o g r a m t o s e r v i c e K e y b o a r d P r o g r a m t o s e r v i c e c h a r a c t e r r e a d e r P r o g r a m t o s e r v i c e li n e p r in t e r D I S K 2 5 6 K B D R D R P T R I/ O s e r v ic e p r o g r a m s KBD Int. Here 749 DISK Int. Here 255

- 16. Computer System Architecture Dept. of Info. Of Computer.Chap. 11 Input-Output OrganizationChap. 11 Input-Output Organization 11-16 Initial Operation of ISR » 1) Clear lower-level mask register bit ( 낮은 순위 Int. 발생 방지 ) » 2) Clear interrupt status bit IST » 3) Save contents of processor registers » 4) Set interrupt enable bit IEN ( 높은 순위 Int. 발생을 원할 때만 ) » 5) Proceed with service routine Final Operation of ISR » 1) Clear interrupt enable bit IEN ( 아래 2, 3, 4, 5 실행 중 Int. 발생 방지 ) » 2) Restore contents of processor registers » 3) Clear the bit in the interrupt register belonging to the source that has been serviced » 4) Set lower-level priority bits in the mask register ( 낮은 순위 Int. 발생 허용 ) » 5) Restore return address into PC and set IEN 11-6 Direct Memory Access (DMA) DMA DMA controller takes over the buses to manage the transfer directly between the I/O device and memory (Bus Request/Grant 신호 이용 ) Fig. 11-14 C P U B R B G D B U S W R A B U S R D B u s r e q u e s t B u s g r a n t A d d r e s s b u s W r i t e R e a d D a t a b u s H i g h - i m p e d a n c e ( d i s a b le ) w h e n B G i s e n a b l e d D M A C o n t r o l l e r B R B G

- 17. Computer System Architecture Dept. of Info. Of Computer.Chap. 11 Input-Output OrganizationChap. 11 Input-Output Organization 11-17 Transfer Modes 1) Burst transfer : Block 단위 전송 2) Cycle stealing transfer : Byte 단위 전송 DMA Controller ( Intel 8237 DMAC ) : Fig. 11-17 DMA Initialization Process » 1) Set Address register : memory address for read/write » 2) Set Word count register : the number of words to transfer » 3) Set transfer mode : read/write, burst/cycle stealing, I/O to I/O, I/O to Memory, Memory to Memory Memory search I/O search » 4) DMA transfer start : next section » 5) EOT (End of Transfer) : Interrupt 발생 C o n t r o l lo g ic C S D a t a b u s b u f f e r s C o n t r o l r e g is t e r D a t a b u s D M A s e le c t Internalbus R S In t e r r u p t B G B R R D W R R e g is t e r s e le c t R e a d W r it e B u s r e q u e s t B u s g r a n t In t e r r u p t A d d r e s s r e g is t e r W o r d c o u n t r e g is t e r A d d r e s s b u s b u f f e r s A d d r e s s b u s D M A r e q u e s t D M A A c k n o w le d g e t o I/ O d e v ic e

- 18. Computer System Architecture Dept. of Info. Of Computer.Chap. 11 Input-Output OrganizationChap. 11 Input-Output Organization 11-18 DMA Transfer (I/O to Memory) 1) I/O Device sends a DMA request 2) DMAC activates the BR line 3) CPU responds with BG line 4) DMAC sends a DMA acknowledge to the I/O device 5) I/O device puts a word in the data bus (for memory write) 6) DMAC write a data to the address specified by Address register 7) Decrement Word count register 8) Word count register = 0 이면 EOT interrupt 발생하여 CPU 에 알림 9) Word count register ≠ 0 이면 DMAC checks the DMA request from I/O device I/ O P e r ip h e r a l d e v ic e D M A a c k n o w le d g e A d d re s s s e le c t C P U In t e r r u p t A d d r e s s D a t a B G B R R D W R R a n d o m a c c e s s m e m o r y ( R A M ) A d d re s s D a t aR D W R D ir e c t m e m o r y a c c e s s ( D A M ) c o n t r o lle r In t e r r u p t A d d r e s s D a t aR D W R B G R S D S B R D M A r e q u e s t R e a d c o n t r o l W r it e c o n t r o l A d d r e s s b u s D a t a b u s

- 19. Computer System Architecture Dept. of Info. Of Computer.Chap. 11 Input-Output OrganizationChap. 11 Input-Output Organization 11-19 11-7 Input-Output Processor (IOP) IOP : Fig. 11-19 Communicate directly with all I/O devices Fetch and execute its own instruction » IOP instructions are specifically designed to facilitate I/O transfer » DMAC must be set up entirely by the CPU Designed to handle the details of I/O processing Command Instruction that are read form memory by an IOP » Distinguish from instructions that are read by the CPU » Commands are prepared by experienced programmers and are stored in memory » Command word = IOP program M e m o r y u n it C e n t r a l P r o c e s s in g u n it ( C P U ) In p u t - o u t p u t p r o c e s s o r ( IO P ) Memorybus P D P DP DP D P e r ip h e r a l d e v ic e s I/ O b u s

- 20. Computer System Architecture Dept. of Info. Of Computer.Chap. 11 Input-Output OrganizationChap. 11 Input-Output Organization 11-20 CPU - IOP Communication : Fig. 11-20 Memory units acts as a message center : Information 전달 영역 » each processor leaves information for the other C P U o p e r a t io n s I O P o p e r a t io n s S e n d in s t r u c t io n t o t e s t IO P p a t h T r a n s f e r s t a t u s w o r d t o m e m o r y lo c a t io n If s t a t u s O K . , s e n d s t a r t I/ O in s t r u c t io n t o I O P A c c e s s m e m o r y f o r I O P p r o g r a m C P U c o n t in u e s w it h a n o t h e r p r o g r a m C o n d u c t I/ O t r a n s f e r u s in g D M A ; p r e p a r e s t a t u s r e p o r t I/ O t r a n s f e r c o m p le t e d in t e r r u p t C P U R e q u e s t I O P s t a t u s T r a n s f e r s t a t u s w o r d t o m e m o r y lo c a t io n C h e c k s t a t u s w o r d f o r c o r r e c t t r a n s f e r C o n t in u e Message Center IOP Program CPU Program

- 21. Computer System Architecture Dept. of Info. Of Computer.Chap. 11 Input-Output OrganizationChap. 11 Input-Output Organization 11-21 IBM 370 I/O Channel Channel = I/O Processor in IBM 370 computer Three types of channel » 1) Multiplexer channel : slow-medium speed device, operating with a number of I/O devices simultaneously » 2) Selector channel : high-speed device, one I/O operation at a time » 3) Block-Multiplexer channel : 1) + 2) I/O instruction format : Fig. 11-21(a) » Operation code : 8 개 Start I/O, Start I/O fast release (less CPU time), Test I/O, Clear I/O, Halt I/O, Halt device, Test channel, Store channel ID Channel Status Word : Fig. 11-21(b) » Always stored in Address 64 in memory » Key : Protection used to prevent unauthorized access » Address : Last channel command word address used by channel » Count : 0 (if successful transfer) O p e r a t io n c o d e D e v ic e a d d r e s s C h a n n e l a d d r e s s ( a ) I / O in s t r u c t io n f o r m a t K e y A d d r e s s C o u n tS t a t u s ( b ) C h a n n e l s t a t u s w o r d f o r m a t C o m m a n d c o d e D a t a a d d r e s s C o u n tF la g s ( c ) C h a n n e l c o m m a n d w o r d f o r m a t

- 22. Computer System Architecture Dept. of Info. Of Computer.Chap. 11 Input-Output OrganizationChap. 11 Input-Output Organization 11-22 Channel Status Word : Fig. 11-21(c) » Always stored in Address 72 in memory » Command Code Write : transfer data from memory to I/O device Read : transfer data I/O device to memory Read backwards : read magnetic tape with tape moving backward Control : rewinding of tape, positioning a disk-access mechanism (HDD head control) Sense : inform the channel status word to the address 64 (Status Read) Transfer in channel : channel jump command (Channel change) » Flags 100000 : data chaining (same record) 010000 : command chaining (same device) 000000 : separate record,and End of I/O operation Example of a channel program : Tab. 11-3 Command Address Flags Count Write tape 4000 100000 60 Write tape 6000 010000 20 Write tape 3000 000000 40 3000 4000 6000 40 60 20 40 80 + TapeMemory Same record same device Separate record same device

- 23. Computer System Architecture Dept. of Info. Of Computer.Chap. 11 Input-Output OrganizationChap. 11 Input-Output Organization 11-23 Location of information in the IBM 370 : Fig. 11-22 Address 72 에 I/O channel program 의 시작 Address (xxxx) 를 미리 설정 CPU 에 의해 Start I/O 명령 실행 I/O channel program 이 실행 실행 결과를 Address 64 에 저장 C h a n n e l s t a t u s w o r d C h a n n e l a d d r e s s w o r d C h a n n e l c o m m a n d w o r d 1 C h a n n e l c o m m a n d w o r d 3 C h a n n e l c o m m a n d w o r d 2 S t a r t I/ O i n s t r u c t i o n 6 4 7 2 M e m o r y u n it I/ O c h a n n e l p r o g r a m C P U p r o g r a m xxxx xxxx Fig. 11-21(b) Fig. 11-21(a) Fig. 11-21(c)

- 24. Computer System Architecture Dept. of Info. Of Computer.Chap. 11 Input-Output OrganizationChap. 11 Input-Output Organization 11-24 Intel 8089 IOP : Fig. 11-23 CPU enables channel attention Select one of two channels of 8089 8089 gets attention of the CPU by sending an interrupt request 8 0 8 6 C P U 8 0 8 9 I O P B u s C o n t r o lle r M e m o r y u n it In t e r f a c e In t e r f a c e I n p u t d e v ic e O u t p u t d e v ic e L o c a l b u s attention Channel Interrupt Select b u s S y s t e m Location of Information : Fig. 11-24 Channel Command Word (CCW) : message center » Start command » Suspend command » Resume command » Halt command C o n tro l b lo c k P a ra m e te r b lo c k T a s k b lo c k B u s y C C W P B a d d re s s T B a d d re s s S ta tu s T ra c k a n d s e c to r D e v ic e a d d re s s B y te c o u n t M e m o ry a d d re s s 8 0 8 9 IO P p ro g ra m

- 25. Computer System Architecture Dept. of Info. Of Computer.Chap. 11 Input-Output OrganizationChap. 11 Input-Output Organization 11-25 11-8 Serial Communication Difference between I/O Processor and Data Communication Processor I/O Processor » communicate with peripherals through a common I/O bus (data, address, control bus) Data Communication Processor » communicate with each terminal through a single pair of wires Modem ( = Data Sets, Acoustic Couplers ) Convert digital signals into audio tones to be transmitted over telephone lines Various modulation schemes are used (FM, AM, PCM) Block transfer An entire block of characters is transmitted in synchronous transmission Transmitter sends one more character (error check) after the entire block is sent Error Check LRC (Longitudinal Redundancy Check) : XOR CRC (Cyclic Redundancy Check) : Polynomial 3 Transmission System Simplex : one direction only Half-duplex : both directions but only one direction at a time Full-duplex : both directions simultaneously “Data Communication” 교과 참고

- 26. Computer System Architecture Dept. of Info. Of Computer.Chap. 11 Input-Output OrganizationChap. 11 Input-Output Organization 11-26 Data Link The communication lines, modems, and other equipment used in the transmission of information between two or more stations Data Link Protocol 1) Character-Oriented Protocol 2) Bit-Oriented Protocol Character-Oriented Protocol Message format for Character-Oriented Protocol : Fig. 11-25 » TEXT : 전송할 내용 » BCC : Block Check Character (LRC or CRC) ASCII Communication Control Character : Tab. 11-4 » SYN (0010110) : Establishes synchronism » SOH (0000001) : Start of Header (address or control information) » STX (0000010) : Start of Text » ETX (0000011) : End of Text Transmission Example : Tab. 11-5, 11-6 S Y N S O HS Y N H e a d e r S T X T e x t B C CE T X

- 27. Computer System Architecture Dept. of Info. Of Computer.Chap. 11 Input-Output OrganizationChap. 11 Input-Output Organization 11-27 Data Transparency Character-Oriented Protocol 에서 Binary Information 을 전송하면 , 이를 Control Character 로 오인하여 문제가 발생 따라서 Character-Oriented Protocol 에서 Data Transparency 를 해결하기 위해서 DLE (Data Link Escape) Character 를 사용 DLE Inserting a DLE character (bit pattern = 00010000) before each control character » Exam) DLE ETX DLE SYN 그러나 DLE character is inefficient and somewhat complicated to implement 따라서 Bit-Oriented Protocol 을 사용 Bit-Oriented Protocol Transmit a serial bit stream (Frame) of any length without character boundaries Examples of bit-oriented protocol » 1) SDLC (Synchronous Data Link Control) : IBM » 2) HDLC (High-level Data Link Control) : ISO » 3) ADCCP (Advanced Data Communication Control Procedure) : ANSI Frame format for bit-oriented protocol : Fig. 11-26 » Flag : A frame starts and ends with 8-bit flag (01111110) F la g 0 1 1 1 1 1 1 0 C o n t r o l 8 b it s A d d r e s s 8 b it s In f o r m a t io n a n y n u m b e r o f b it s F r a m e c h e c k 1 6 b it s F la g 0 1 1 1 1 1 1 0

- 28. Computer System Architecture Dept. of Info. Of Computer.Chap. 11 Input-Output OrganizationChap. 11 Input-Output Organization 11-28 Zero Insertion » Prevent a flag from occurring in the middle of a data frame » Zero (0) is inserted by transmitting station after any succession of five continuous 1’s Example of zero insertion : 01111110 (data) 011111010 » Receiver always removes a 0 that follows a succession of five 1’s Control field format : Fig. 11-27 » 1) Information Transfer : for ordinary data transmission » 2) Supervisory : for ready, busy condition check, ... » 3) Unnumbered : for initialization of link functions, reporting errors, ... N S N rP / F0 54321 876 I n f o r m a t i o n t r a n s f e r : N rP / F1S u p e r v i s o r y : P / FU n u m b e r e d : C o d e0 C o d eC o d e11 N S N r P / F C o d e P o l l / f i n a l R e c e i v e c o u n t B i n a r y c o d e S e n d c o u n t Security 를 위하여 임의로 정의하여 사용함

- 29. Computer System Architecture Dept. of Info. Of Computer.Chap. 11 Input-Output OrganizationChap. 11 Input-Output Organization 11-29 Control Fields » Ns : send frame count » Nr : error free 한 receive frame count » P/F : P = 1 : primary station is finished and ready for the secondary station to respond P = 0 : each frame sent to the secondary station from the primary station F = 1 : secondary station sends the last frame F = 0 : secondary station responds with a number of frame (when primary station is finished) » Code : type of command/response