Tarea 2 mapa mental int,mod dir,mem and reg

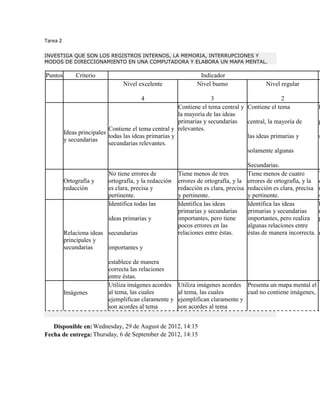

- 1. Tarea 2 INVESTIGA QUE SON LOS REGISTROS INTERNOS, LA MEMORIA, INTERRUPCIONES Y MODOS DE DIRECCIONAMIENTO EN UNA COMPUTADORA Y ELABORA UN MAPA MENTAL. Puntos Criterio Indicador Nivel excelente Nivel bueno Nivel regular 4 3 2 Contiene el tema central y Contiene el tema F la mayoría de las ideas primarias y secundarias central, la mayoría de p Contiene el tema central y relevantes. Ideas principales todas las ideas primarias y las ideas primarias y s y secundarias secundarias relevantes. solamente algunas Secundarias. No tiene errores de Tiene menos de tres Tiene menos de cuatro T Ortografía y ortografía, y la redacción errores de ortografía, y la errores de ortografía, y la e redacción es clara, precisa y redacción es clara, precisa redacción es clara, precisa r pertinente. y pertinente. y pertinente. s Identifica todas las Identifica las ideas Identifica las ideas E primarias y secundarias primarias y secundarias r ideas primarias y importantes, pero tiene importantes, pero realiza p pocos errores en las algunas relaciones entre Relaciona ideas secundarias relaciones entre éstas. éstas de manera incorrecta. m principales y secundarias importantes y establece de manera correcta las relaciones entre éstas. Utiliza imágenes acordes Utiliza imágenes acordes Presenta un mapa mental el Imágenes al tema, las cuales al tema, las cuales cual no contiene imágenes, ejemplifican claramente y ejemplifican claramente y son acordes al tema son acordes al tema Disponible en: Wednesday, 29 de August de 2012, 14:15 Fecha de entrega: Thursday, 6 de September de 2012, 14:15

- 2. Fundamentos de Lógica Digital LUNES, 19 DE NOVIEMBRE DE 2007 Suplemento # 4a: Las instrucciones del µP 8086 Todo microprocesador, desde el primero que hizo su aparición hasta los más complejos en la actualidad, desde el momento en que es puesto a la venta es entregado con un conjunto de instrucciones en lenguaje de máquina en las cuales se detallan las operaciones que el microprocesador es capaz de hacer. En cada versión nueva de microprocesador la primera prioridad es aumentar el número de instrucciones disponibles para ofrecer más opciones de programación al programador. Aunque pudiera parecerle a muchos un ejercicio inútil la familiarización con el conjunto de instrucciones de las operaciones que puede llevar a cabo cualquier microprocesador, es de enorme interés el estar familiarizados con el conjunto "primitivo" de las instrucciones de los primeros microprocesadores que aparecieron en el mercado por una razón muy sencilla:todas las instrucciones de cada microprocesador se han ido incorporando dentro del conjunto de instrucciones del nuevo modelo que lo reemplaza. Esto se debe a una característica impuesta por los consumidores: la demanda de algo conocido como upwardcompatibility. Esencialmente, esto consiste en el hecho de que una de las grandes inversiones en cualquier computadora personal de escritorio son los programas que se van a ejecutar en ella. A nadie le gusta invertir mucho dinero en la adquisición de programas para utilizar procesadores de palabras como Microsoft Word o hacer diseños gráficos como AutoCAD si dichos programas no se podrán correr en las nuevas computadoras que vayan saliendo al mercado. Esto prácticamente exige a los fabricantes de los microprocesadores continuar incorporando dentro de sus nuevos modelos la capacidad para poder

- 3. "entender" las instrucciones que podían ser "entendidas" por los modelos previos, ya que de no ser así basta una sola instrucción ausente para poder inutilizar potencialmente una inversión de cientos o quizá miles de dólares en "software". Es por esto que es de enorme interés el lograr una familiarización con los conjuntos de instrucciones de los microprocesadores más sencillos, puesto quien no logra tal cosa menos podrá comprender los nuevos conjuntos de instrucciones mucho más amplios y mucho más complejos de los microprocesadores de la actualidad. Para poder entender el significado del conjunto de instrucciones del microprocesador 8086 es necesario tomar conocimiento de algunos detalles internos a la arquitectura de este microprocesador. Lo más importante es que el 8086 posee varios registros de almacenamiento, construídos cada uno de ellos con 16 flip-flops: Estos registros pueden ser clasificados en cuatro categorías: el registro de las banderas(flags), los ocho registros de propósito general (AX, BX, CX, DX, SI, DI, BP y SP, cada uno de 16 bits), el puntero de instrucciones IP, y los registros de segmentos (CS,DS, ES y SS). El problema principal en utilizar únicamente 16 bits para "domiciliar" cada dato contenido en una

- 4. memoria RAM es que con 16 bits solo se pueden especificar 65,536 ( = 2n = 216 ) localidades diferentes de memoria RAM con todas las combinaciones posibles de "unos" y "ceros" que permite una palabra de 16 bits. Los registros de segmentos son utilizados para un ingenioso esquema de adición de "segmentos" de bits al domicilio básico de 16 bits mediante estos registros especiales, esquema manejado por el microprocesador 8086 con el propósito de poder "domiciliar" más de 65,536 bytes cuando se cuenta únicamente con registros de 16 bits para ello, esto es, cuando se requiere "domiciliar" para la ejecución de cualquier programa decente una cantidad de memoria RAM mucho mayor que la que normalmente podría "domiciliar" un microprocesador limitado al uso de palabras binarias con una extensión de 16 bits. El proceso de ampliación del espacio de memoria "domiciliable" se puede bosquejar en su esencia más sencilla de la siguiente manera: Es así como en las primeras computadoras personales de escritorio no hubo ninguna dificultad para que el microprocesador 8086 pudiese manejar memorias RAM con una capacidad de un millón de localidades diferentes (1 millón 48 mil 576 para ser exactos) ó 1 Megabytes, con cada localidad almacenando un byte (8 bits) de información:

- 5. Generalmente hablando, el registro de las banderas no tiene como objetivo el ser accesado directamente por el programador del microprocesador; estas "banderas" son "izadas" (puestas en "1") cuando ocurre alguna condición especial, por ejemplo cuando el resultado de alguna operación aritmética es cero, lo cual iza la "bandera de cero" o zeroflagponiéndo dicho registro en el estado "1". La posición relativa de cada una de las "banderas" en este registro es la siguiente: Las "banderas" guardadas por el registro son las siguientes: O = Overflowflag (bandera de sobreflujo) D = Directionflag (bandera de dirección) T = Trapflag (bandera de trampa) S = Signflag (bandera de signo aritmético) Z = Zero flag (bandera de cero) A = AuxiliaryCarryflag (bandera de "llevar" auxiliar)

- 6. C = Carryflag (bandera de "llevar") El registro AX en el microprocesador es el registro mejor conocido en las computadoras convencionales como el acumulador. Siempre está involucrado cuando se llevan a cabo las operaciones de multiplicación y división, y también es el registro más eficiente de utilizar cuando se llevan a cabo ciertas operaciones aritméticas, lógicas, y de movimiento de datos. El registro BX puede ser utilizado como puntero hacia localidades de la memoria RAM. La especialidad del registro CX es contar. El registro DX es el único registro en el microprocesador 8086 que puede ser utilizado como un puntero hacia domicilios relacionados con las unidades de Entrada/Salida(Input/Output) con las instrucciones IN y OUT. El registro SP es el conocido como el puntero hacia la pila (stack pointer). A continuación se presenta el conjunto de instrucciones disponibles dentro de dos de los primeros grandes microprocesadores "abuelos", el microprocesador 8086 y el microprocesador 8088, junto con las descripciones que les fueron dadas originalmente. Es importante señalar que este conjunto de instrucciones está dado en las mnemónicas(abreviaturas de fácil memorización) que fueron dadas por los fabricantes, porque a fin de cuentas todas estas instrucciones en realidad son instrucciones en lenguaje de "unos" y "ceros", y para poder convertir un programa escrito con estas mnemónicas a un programabinario que la máquina pueda correr directamente es necesario utilizar la ayuda de un lenguaje ensamblador (assembler): aaa ASCCI adjust after addition aad ASCII adjust before division aam ASCII adjust after multiplication aas

- 7. ASCII adjust after subtraction adc add with carry add add without carry and logical AND call target call procedure cbw convert byte to word clc clear carry flag cld clear direction flag cli clear interrupt flag cmc complement carry flag cmp destination, source compare cmps source, destination compare strings cmpsb compare string bytes cmpsw compare string words

- 8. cwd convert word to doubleword daa decimal adjust after addition das decimal adjust after subtraction dec destination decrement div source unsigned divide esc immediate, source escape hit halt idiv source signed integer divide imul source signed integer multiply in accumulator, port input from port inc destination increment ins destination, port input from port to string insb input from port to string byte insw input from port to string word

- 9. int immediate call interrupt service routine into interrupt on overflow iret interrupt return ja jump if above; (carry flag = 0) and (zero flag = 0) jae jump if above or equal; (carry flag = 0) jb jump if below (carry flag = 1) jbe jump if below or equal; (carry flag = 1) or (zero flag = 1) jc jump if carry; (carry flag = 1) jcxz jump if register cx equals 0 je jump if equal; (zero flag = 1) jg jump if greater; (sign flag = overflow flag) and (zero flag = 0) jge jump if greater or equal; (sign flag = overflow flag) jl jump if less; (sign flag less than or greater than overflow flag) jle

- 10. jump if less or equal; (sign flag less than or greater than overflow flag) or (zero flag = 1) jna jump if not above (carry flag = 1) or (zero flag = 1) jnae jump if not above or equal (carry flag = 1) jnb jump if not below; (carry flag = 0) jnbe jump if not below or equal; (carry flag = 0) and (zero flag = 0) jnc jump if not carry; (carry flag = 0) jne jump if not equal; (zero flag = 0) jng jump if not greater; (sign flag less than or greater than overflow flag) or (zero flag = 1) jnge jump if not greater or equal; (sign flag less than or greater than overflow flag) jnl jump if not less; (sign flag = overflow flag) jnle jump if not less or equal; (sign flag = overflow flag) and (zero flag = 0) jno jump if not overflow; (overflow flag = 0) jnp jump if not parity; (parity flag = 0) jns jump if not sign; (sign flag = 0)

- 11. jnz jump if not zero; (zero flag = 0) jo jump if overflow; (oveflow flag = 1) jp jump if parity; (parity flag =1) jpe jump if parity even; (parity flag = 1) jpo jump if parity odd; (parity flag = 0) js jump if sign; (sign flag = 1) jz jump if zero; (zero flag = 1) jump target jump unconditionally lahf load (some) flags into register ah lds register, source load pointer and register ds lea register, source load effective address les register, source load pointer and register es lock lock the bus lod source load string

- 12. lodsb load string byte lodsw load string word loop target loop on register cx loope target loop on register cx while equal loopz target loop on register cx while zero flag = 1 loopne target loop on register cx while not equal loopnz target loop on register cx while zero flag = 0 mov destination, source move data mov destination, source move string movsb move string byte movsw move string word mul source unsigned multiplication neg destination two's complemente negation nop

- 13. no operation not destination one's complement negation or destination, source logical OR out port, accumulator output to port outs port, source output from string to port outsb output from string byte to port outsw ountput from string word to port pop destination pop from stack popf pop flags push source push onto stack pushf push flags rcl destination, count rotate through carry-left rcr destination, count rotate through carry-right rep string instruction repeat

- 14. repe string instruction repeat while equal repz string instruction repeat while zero flag = 1 repne string instruction repeat while not equal repnz string instruction repeat while zero flag = 0 ret immediate return retf immediate return far retn immediate return near rol destination, count rotate left ror destination, count rotate right sahf store ah register to flags register sal destination, count shift arithmetic left sar destination, count shift arithmetic right sbb destination, source subtract integers with borrow scasb destination scan string

- 15. scasw scan string word shl destination, count shift left shr destination, count shift right stc set carry flag std set direction flag sti set interrupt-enable flag stos destination store string stosb store string byte stosw store string word sub destination, source subtract test destination, source test bits wait wait until not busy xchg destination, source exchange xlat source

- 16. translate from table xlatb translate from table xor destination, source exclusive OR Varias de estasinstruccionesprácticamentedelatan la arquitecturadelmicroprocesador. Las instrucciones shl (shift left) y shr (shift right) delatan la presencia de unregistro de desplazamiento en ambasvías, quepuedesercapaz de irdesplazandounapalabrabinaria bit-por-bit ya sea hacia la izquierda o hacia la derecha. Porotrolado, lasinstrucciones popy push revelanque se puedeoperarunapila de datosdesdedelmicroprocesador. A manera de ejemplo de cómo se usanestasinstruccionesparairforjandounprogramaelaboradoparaestemicroprocesador 8086 de Intel, tenemos el siguientefragmentoescrito en algúnlenguajeensambladorcomo Turbo Assembler: ... mov ah,0 moval,ah inc al ... en donde la primerainstrucción mov "carga" el registro AH con el valor de 0 (o mejordicho, con el byte de cero, "00000000"), con la segundainstrucción mov se copia el valor almacenado en el registro AH al registro AL, y trasestoincrementa en unaunidad el contenido del registro AL con la instrucción inc.El resultado final nos deja ambos registrosAL y AH "cargados" con el valor 00000000, "limpiando" ambos registros a cero. (La instrucción mov en realidad debería haberse llamado copy, porque el contenido tomado del registro original no es removido de dicho registro.) Aquí tenemos otro ejemplo: ... mov ax,5 mov dx,9

- 17. add ax,dx ... Este pequeño fragmento "carga" el registro AX con el número 5 (o mejor dicho, con el número binario 00000101), tras lo cual "carga" el registro DX con el número 9 (o mejor dicho, con el número binario 00001001), y en la tercera instrucción suma los contenidos en ambos registros dejando el resultado en el registro AX. En castellano, esto ser resumiría como "poner al acumulador en el estado 5 (cargar sus flip-flops con el equivalente binario del número 5), "poner al registro dx en el estado 9", "y sumar el contenido del registro DX al contenido del acumulador dejando el resultado en el acumulador". REGISTROS DEL PROCESADOR Los registros del procesador se emplean para controlar instrucciones en ejecución, manejar direccionamiento de memoria y proporcionar capacidad aritmética. Los registros son direccionables por medio de un nombre. Los bits por convención, se numeran de derecha a izquierda, como en: ... 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 Los registros internos del procesador se puede clasificar en 6 tipos diferentes 1. Registros de segmento 2. Registros de propósito general 3. Registros de apuntadores 4. Registros de banderas 5. Registros de Puntero de instrucción 6. Registros de Pila

- 18. Registros de segmento Un registro de segmento tiene 16 bits de longitud y facilita un área de memoria para direccionamiento conocida como el segmento actual. Registro CS. El DOS almacena la dirección inicial del segmento de código de un programa en el registro CS. Esta dirección de segmento, mas un valor de desplazamiento en el registro apuntador de instrucción (IP), indica la dirección de una instrucción que es buscada para su ejecución. Registro DS. La dirección inicial de un segmento de datos de programa es almacenada en el registro DS. En términos sencillos, esta dirección, mas un valor de desplazamiento en una instrucción, genera una referencia a la localidad de un byte especifico en el segmento de datos. Registro SS. El registro SS permite la colocación en memoria de una pila, para almacenamiento temporal de direcciones y datos. El DOS almacena la dirección de inicio del segmento de pila de un programa en le registro SS. Esta dirección de segmento, mas un valor de desplazamiento en el registro del apuntador de pila (SP), indica la palabra actual en la pila que esta siendo direccionada. Registros ES. Alguna operaciones con cadenas de caracteres (datos de caracteres) utilizan el registro extra de segmento para manejar el direccionamiento de memoria. En este contexto, el registro ES esta asociado con el registro DI (índice). Un programa que requiere el uso del registro ES puede inicializarlo con una dirección de segmento apropiada. Registros FS y GS. Son registros extra de segmento en los procesadores 80386 y posteriores. Regresar Arriba

- 19. Registros de propósito general. Los registros de propósito general AX, BX, CX y DX son los caballos de batalla del sistema. Son únicos en el sentido de que se puede direccionarlos como una palabra o como una parte de un byte. El ultimo byte de la izquierda es la parte "alta", y el ultimo byte de la derecha es la parte "baja". Por ejemplo, el registro CX consta de una parte CH (alta) y una parte Cl (baja), y usted puede referirse a cualquier parte por su nombre. Registro AX. El registro AX, el acumulador principal, es utilizado para operaciones que implican entrada/salida y la mayor parte de la aritmética. Por ejemplo, las instrucciones para multiplicar , dividir y traducir suponen el uso del AX. También, algunas operaciones generan código mas eficiente si se refieren al AX en lugar de a los otros registros. Registro BX. El BX es conocido como el registro base ya que es el único registro de propósito general que puede ser índice para direccionamiento indexado. También es común emplear el BX para cálculos. Registro DX. El DX es conocido como l registro de datos. Alguna operaciones de entrada/salida requieren uso, y las operaciones de multiplicación y división con cifras grandes suponen al DX y al AX trabajando juntos. Regresar Arriba

- 20. Registro de Apuntador de Instrucciones. El registro apuntador de instrucciones (IP) de 16 bits contiene el desplazamiento de dirección de la siguiente instrucción que se ejecuta. El IP esta asociado con el registro CS en el sentido de que el IP indica la instrucción actual dentro del segmento de código que se esta ejecutando actualmente. Los procesadores 80386 y posteriores tienen un IP ampliado de 32 bits, llamado EIP. En el ejemplo siguiente, el registro CS contiene 25A4[0]H y el IP contiene 412H. Para encontrar la siguiente instrucción que será ejecutada, el procesador combina las direcciones en el CS y el IP: Segmento de dirección en el registro CS: 25A40H Desplazamiento de dirección en el registro IP: + 412H Dirección de la siguiente instrucción: 25E52H Regresar Arriba Registros Apuntadores. Los registros SP (apuntador de la pila) Y BP (apuntador de base) están asociados con el registro SS y permiten al sistema accesar datos en el segmento de la pila. Registro SP. El apuntador de la pila de 16 bits esta asociado con el registro SS y proporciona un valor de desplazamiento que se refiere a la palabra actual que esta siendo procesada en la pila. Los procesadores 80386 y posteriores tienen un apuntador de pila de 32 bits, el registro ESP. El sistema maneja de forma automática estos registros.

- 21. En el ejemplo siguiente, el registro SS contiene la dirección de segmento 27B3[0]H y el SP el desplazamiento 312H. Para encontrar la palabra actual que esta siendo procesada en la pila, la computadora combina las direcciones en el SS y el SP: Registro BP. El BP de 16 bits facilita la referencia de parámetros, los cuales son datos y direcciones transmitidos vía pila. Los procesadores 80386 y posteriores tienen un BP ampliado de 32 bits llamado el registro EBP. Regresar Arriba Registros Indice. Los registros SI y DI están disponibles para direccionamiento indexado y para sumas y restas. Registro SI. El registro índice fuente de 16 bits es requerido por algunas operaciones con cadenas (de caracteres). En este contexto, el SI esta asociado con el registro DS. Los procesadores 80386 y posteriores permiten el uso de un registro ampliado de 32 bits, el ESI. Registro DI. El registro índice destino también es requerido por algunas operaciones con cadenas de caracteres. En este contexto, el DI esta asociado con el registro ES. Los procesadores 80386 y posteriores permiten el uso de un registro ampliado de 32 bits, el EDI.

- 22. Regresar Arriba Registro de Banderas. De los 16 bits del registro de banderas, nueve son comunes a toda la familia de procesadores 8086, y sirven para indicar el estado actual de la maquina y el resultado del procesamiento. Muchas instrucciones que piden comparaciones y aritmética cambian el estado de las banderas, algunas cuyas instrucciones pueden realizar pruebas para determinar la acción subsecuente. En resumen, los bits de las banderas comunes son como sigue: OF (Overflow, desbordamiento). Indica desbordamiento de un bit de orden alto (mas a la izquierda) después de una operación aritmética. DF (dirección). Designa la dirección hacia la izquierda o hacia la derecha para mover o comparar cadenas de caracteres. IF (interrupción). Indica que una interrupción externa, como la entrada desde el teclado, sea procesada o ignorada. TF (trampa). Permite la operación del procesador en modo de un paso. Los programas depuradores, como el DEBUG, activan esta bandera de manera que usted pueda avanzar en la ejecución de una sola instrucción a un tiempo, para examinar el efecto de esa instrucción sobre los registros de memoria.

- 23. SF (signo). Contiene el signo resultante de una operación aritmética (0 = positivo y 1 = negativo). ZF (cero). Indica el resultado de una operación aritmética o de comparación (0 = resultado diferente de cero y 1 = resultado igual a cero). AF (acarreo auxiliar). Contiene un acarreo externo del bit 3 en un dato de 8 bits para aritmética especializada. PF (paridad). Indica paridad par o impar de una operación en datos de 8 bits de bajo orden (mas a la derecha). CF (acarreo). Contiene el acarreo de orden mas alto (mas a la izquierda) después de una operación aritmética; también lleva el contenido del ultimo bit en una operación de corrimiento o de rotación. Las banderas están en el registro de banderas en las siguientes posiciones: Las banderas mas importantes para la programación en ensamblador son O, S, Z y C, para operaciones de comparación y aritméticas, y D para operaciones de cadenas de caracteres. Los procesadores 80286 y posteriores tienen algunas banderas usadas para propósitos internos, en especial las que afectan al modo protegido. Los procesadores 80286 y posteriores tienen un registro extendido de banderas conocido como Eflags. Regresar Arriba

- 24. Registros de PILA La pila es un área de memoria importante y por ello tiene, en vez de uno, dos registros que se usan como desplazamiento (offset) para apuntar a su contenido. Se usan como complemento al registro y son: -SP- Stack Pointer: Se traduce como puntero de pila y es el que se reserva el procesador para uso propio en instrucciones de manipulado de pila. Por lo general , el programador no debe alterar su contenido. -BP- Base pointer: Se usa como registro auxiliar. El programador puede usarlo para su provecho. Claro que estos nombres y tipos de registros son estándar, ya que cada fabricante puede utilizar otros registro que reemplacen a estos o los auxilien, aun así, los fabricantes que usan otros registro tienen la misma función que los anteriormente mencionados Ejemplo Registros de uso general del 8086/8088: Tienen 16 bits cada uno y son ocho: 1. AX = Registro acumulador, dividido en AH y AL (8 bits cada uno). Usándolo se produce (en general) una instrucción que ocupa un byte menos que si se utilizaran otros registros de uso general. Su parte más baja, AL, también tiene esta propiedad. El último registro mencionado es el equivalente al acumulador de los procesadores anteriores (8080 y 8085). Además hay instrucciones como DAA; DAS; AAA; AAS; AAM; AAD; LAHF; SAHF; CBW; IN y OUT que trabajan con AX o con uno de sus dos

- 25. bytes (AH o AL). También se utiliza este registro (junto con DX a veces) en multiplicaciones y divisiones. 2. BX = Registro base, dividido en BH y BL. Es el registro base de propósito similar (se usa para direccionamiento indirecto) y es una versión más potente del par de registros HL de los procesadores anteriores. 3. CX = Registro contador, dividido en CH y CL. Se utiliza como contador en bucles (instrucción LOOP), en operaciones con cadenas (usando el prefijo REP) y en desplazamientos y rotaciones (usando el registro CL en los dos últimos casos). 4. DX = Registro de datos, dividido en DH y DL. Se utiliza junto con el registro AX en multiplicaciones y divisiones, en la instrucción CWD y en IN y OUT para direccionamiento indirecto de puertos (el registro DX indica el número de puerto de entrada/salida). 5. SP = Puntero de pila (no se puede subdividir). Aunque es un registro de uso general, debe utilizarse sólo como puntero de pila, la cual sirve para almacenar las direcciones de retorno de subrutinas y los datos temporarios (mediante las instrucciones PUSH y POP). Al introducir (push) un valor en la pila a este registro se le resta dos, mientras que al extraer (pop) un valor de la pila este a registro se le suma dos. 6. BP = Puntero base (no se puede subdividir). Generalmente se utiliza para realizar direccionamiento indirecto dentro de la pila.

- 26. 7. SI = Puntero índice (no se puede subdividir). Sirve como puntero fuente para las operaciones con cadenas. También sirve para realizar direccionamiento indirecto. 8. DI = Puntero destino (no se puede subdividir). Sirve como puntero destino para las operaciones con cadenas. También sirve para realizar direccionamiento indirecto. Cualquiera de estos registros puede utilizarse como fuente o destino en operaciones aritméticas y lógicas Regresar Arriba Indicadores (flags) Hay nueve indicadores de un bit en este registro de 16 bits. Los cuatro bits más significativos están indefinidos, mientras que hay tres bits con valores determinados: los bits 5 y 3 siempre valen cero y el bit 1 siempre vale uno (esto también ocurría en los procesadores anteriores). CF (CarryFlag, bit 0): Si vale 1, indica que hubo "arrastre" (en caso de suma) hacia, o "préstamo" (en caso de resta) desde el bit de orden más significativo del resultado. Este indicador es usado por instrucciones que suman o restan números que ocupan varios bytes. Las instrucciones de rotación pueden aislar un bit de la memoria o de un registro poniéndolo en el CF.

- 27. PF (ParityFlag, bit 2): Si vale uno, el resultado tiene paridad par, es decir, un número par de bits a 1. Este indicador se puede utilizar para detectar errores en transmisiones. AF (AuxiliarycarryFlag, bit 4): Si vale 1, indica que hubo "arrastre" o "préstamo" del nibble (cuatro bits) menos significativo al nibble más significativo. Este indicador se usa con las instrucciones de ajuste decimal. ZF (Zero Flag, bit 6): Si este indicador vale 1, el resultado de la operación es cero. SF (SignFlag, bit 7): Refleja el bit más significativo del resultado. Como los números negativos se representan en la notación de complemento a dos, este bit representa el signo: 0 si es positivo, 1 si es negativo. TF (TrapFlag, bit 8): Si vale 1, el procesador está en modo paso a paso. En este modo, la CPU automáticamente genera una interrupción interna después de cada instrucción, permitiendo inspeccionar los resultados del programa a medida que se ejecuta instrucción por instrucción. IF (InterruptFlag, bit 9): Si vale 1, la CPU reconoce pedidos de interrupción externas enmascarables (por el pin INTR). Si vale 0, no se reconocen tales interrupciones. Las interrupciones no enmascarables y las internas siempre se reconocen independientemente del valor de IF. DF (DirectionFlag, bit 10): Si vale 1, las instrucciones con cadenas sufrirán "auto-decremento", esto es, se procesarán las cadenas desde las direcciones más altas de memoria hacia las más bajas. Si vale 0, habrá "auto-incremento", lo que quiere decir que las cadenas se procesarán de "izquierda a derecha".

- 28. OF (Overflowflag, bit 11): Si vale 1, hubo un desborde en una operación aritmética con signo, esto es, un dígito significativo se perdió debido a que tamaño del resultado es mayor que el tamaño del destino. Regresar Arriba El procesador Z80 Registros de propósito general El Z80 posee 14 registros de propósito general de 8 bits denominados A, B, C, D, H, L y A', B', C', D', H' , L'. Solamente un set de siete registros y el correspondiente registro de Flags F pueden estar activos al mismo tiempo. Una instrucción especial selecciona A y F o A' y F' mientras que otra instrucción selecciona B, C, D, E, H, L o C', D', E' ,H' L'. El programador puede cambiar rápidamente de un conjunto de registros de propósito general a otro. Esto proporciona una mayor capacidad de almacenamiento en registros. El acceso a datos presentes en registros de la CPU es mucho más rápido que el acceso a datos en memoria. Los registros pueden agruparse de a pares formando registros de 16 bits. Estos son los pares BC, DE y HL (sus equivalentes primas también pueden agruparse). Flags Aunque los Flags existen físicamente dentro de la CPU están agrupados lógicamente formando un registro. Los Flags del Z80 son los siguientes:

- 29. Flag de Cero(Z): Toma el valor 1 si el resultado de una operación es cero. Es el bit seis. Flag de signo(S): Toma el valor 1 si el resultado de una operación es negativo. Es el bit siete. Flag de Carry(C): Este flag es afectado por las instrucciones de desplazamiento y es puesto en 1 ó 0 según el valor del bit desplazado. También es afectado por las operaciones aritméticas. Este flag es el bit cero. Flag de Paridad y overflow(P/V): En el caso de paridad, se pone en 1 si el resultado de una operación posee un número par de unos. Cuando el flag P/V se usa para representar overflow, el flag se pone en 1 si ocurre un overflow después de una operación aritmética. Este flag es el bit 2. Flag H y N: Son dos FlipFlop que no pueden ser examinados por las instrucciones de salto condicional. El Z80 los usa para las operaciones BCD. H representa el rebalse que genera considerando los cuatro bits menos significativos del resultado y N es el flag de resta, el cual se activa para indicar si la última instrucción ejecutada fue suma o resta. En el caso general, una instrucción de resta coloca en 1 el flag N y una instrucción de suma lo coloca en 0. Los Flags H y N son los bits 4 y 1 respectivamente. Registros de propósito especial ProgramCounter: Es un registro de 16 bits que indica la dirección de la próxima instrucción ejecutar. Las instrucciones del Z80 pueden contar de uno, dos, tres o cuatro bytes. Stack-Pointer:

- 30. Es un registro de 16 bits que indica la dirección de una memoria RAM externa denominada Stack. El objetivo de esta área de memoria es proporcionar un medio de almacenamiento temporal de los registros del usuario, registro de Flags y del programCounter. La provisión de Stack es fundamental para operaciones tales como los llamados a sub-rutinas e interrupciones. Registros índices IX e IY: Estos registros son de 16 bits, diseñados para permitir un direccionamiento indexado en los programas del Z80. Cuando se ejecuta una instrucción en un modo de direccionamiento indexado, se usa uno de los dos registros índices para calcular la dirección del operando. Registro de interrupciones I: Es un registro de 8 bits que puede ser cargado para especificar el byte más significativo de una dirección de memoria. El byte menos significativo es proporcionado por el dispositivo que solicita la interrupción. Registro de refresh de memoria R: Es un registro especial diseñado para proporcionar un refresh automático de las memorias RAM dinámicas. Registro de instrucciones: El registro de instrucciones tiene por misión almacenar el código de operación de la instrucción leída desde memoria. Este código es descodificado y con esta información se dirigen todos los micro-pasos. Memoria de acceso aleatorio Para otros usos de este término, véase RAM (desambiguación).

- 31. DIMM normal y corriente de memoria RAM tipo DDR3 de 240 contactos. La memoria de acceso aleatorio (en inglés: random-accessmemory),se utiliza como memoria de trabajo para el sistema operativo, los programas y la mayoría del software. Es allí donde se cargan todas las instrucciones que ejecutan el procesador y otras unidades de cómputo. Se denominan "de acceso aleatorio"porque se puede leer o escribir en una posición de memoria con un tiempo de espera igual para cualquier posición, no siendo necesario seguir un orden para acceder a la información de la manera más rápida posible. Durante el encendido del computador, la rutina POST verifica que los módulos de memoria RAM estén conectados de manera correcta. En el caso que no existan o no se detecten los módulos, la mayoría de tarjetas madres emiten una serie de pitidos que indican la ausencia de memoria principal. Terminado ese proceso, la memoria BIOS puede realizar un test básico sobre la memoria RAM indicando fallos mayores en la misma. Contenido [ocultar] 1 Nomenclatura 2 Historia 3 Tecnologías de memoria o 3.1 SDR SDRAM o 3.2 RIMM RDRAM o 3.3 DDR SDRAM o 3.4 DDR2 SDRAM o 3.5 DDR3 SDRAM 4 Módulos de la memoria RAM 5 Relación con el resto del sistema 6 Detección y corrección de errores 7 Memoria RAM registrada 8 Véase también

- 32. 9 Referencias 10 Enlaces externos [editar]Nomenclatura La expresión memoria RAM se utiliza frecuentemente para describir a los módulos de memoria utilizados en los computadores personales y servidores. En el sentido estricto, esta memoria es solo una variedad de la memoria de acceso aleatorio: las ROM, memorias Flash, caché (SRAM), los registros en procesadores y otras unidades de procesamiento también poseen la cualidad de presentar retardos de acceso iguales para cualquier posición. Los módulos de RAM son la presentación comercial de este tipo de memoria, que se compone de circuitos integrados soldados sobre un circuito impreso independiente, en otros dispositivos como las consolas de videojuegos, la RAM va soldada directamente sobre la placa principal. [editar]Historia Integrado de silicio de 64 bits sobre un sector de memoria de núcleo magnético (finales de los 60). 4MiB de memoria RAM para un computador VAX de finales de los 70. Los integrados de memoria DRAM están agrupados arriba a derecha e izquierda.

- 33. Módulos de memoria tipo SIPP instalados directamente sobre la placa base. Uno de los primeros tipos de memoria RAM fue la memoria denúcleo magnético, desarrollada entre 1949 y 1952 y usada en muchos computadores hasta el desarrollo de circuitos integrados a finales de los años 60 y principios de los 70. Esa memoria requería que cada bit estuviera almacenado en untoroide de material ferromágnetico de algunos milímetros de diámetro, lo que resultaba en dispositivos con una capacidad de memoria muy pequeña. Antes que eso, las computadoras usaban relés y líneas de retardo de varios tipos construidas para implementar las funciones de memoria principal con o sin acceso aleatorio. En 1969 fueron lanzadas una de las primeras memorias RAM basadas en semiconductores de silicio por parte de Intel con el integrado 3101 de 64 bits de memoria y para el siguiente año se presentó una memoria DRAM de 1024 bytes, referencia 1103 que se constituyó en un hito, ya que fue la primera en ser comercializada con éxito, lo que significó el principio del fin para las memorias de núcleo magnético. En comparación con los integrados de memoria DRAM actuales, la 1103 es primitiva en varios aspectos, pero tenía un desempeño mayor que la memoria de núcleos. En 1973 se presentó una innovación que permitió otra miniaturización y se convirtió en estándar para las memorias DRAM: la multiplexación en tiempo de la direcciones de memoria. MOSTEK lanzó la referencia MK4096 de 4096 bytes en un empaque de 16 pines,1 mientras sus competidores las fabricaban en el empaque DIP de 22 pines. El esquema de direccionamiento2 se convirtió en un estándar de facto debido a la gran popularidad que logró esta referencia de DRAM. Para finales de los 70 los integrados eran usados en la mayoría de computadores nuevos, se soldaban directamente a las placas base o se instalaban en zócalos, de manera que ocupaban un área extensa de circuito impreso. Con el tiempo se hizo obvio que la instalación de RAM sobre el impreso principal, impedía la miniaturización , entonces se idearon los primeros módulos de memoria como el SIPP, aprovechando las ventajas de la construcción modular. El formato SIMM fue una mejora al anterior, eliminando los pines metálicos y dejando unas áreas de cobre en uno de los bordes del impreso, muy similares a los de las tarjetas de expansión, de hecho los módulos SIPP y los primeros SIMM tienen la misma distribución de pines.

- 34. A finales de los 80 el aumento en la velocidad de los procesadores y el aumento en el ancho de banda requerido, dejaron rezagadas a las memorias DRAM con el esquema original MOSTEK, de manera que se realizaron una serie de mejoras en el direccionamiento como las siguientes: Módulos formato SIMM de 30 y 72 pines, los últimos fueron utilizados con integrados tipo EDO-RAM. FPM-RAM (Fast Page Mode RAM) Inspirado en técnicas como el "BurstMode" usado en procesadores como el Intel 486,3 se implantó un modo direccionamiento en el que el controlador de memoria envía una sola dirección y recibe a cambio esa y varias consecutivas sin necesidad de generar todas las direcciones. Esto supone un ahorro de tiempos ya que ciertas operaciones son repetitivas cuando se desea acceder a muchas posiciones consecutivas. Funciona como si deseáramos visitar todas las casas en una calle: después de la primera vez no seria necesario decir el número de la calle únicamente seguir la misma. Se fabricaban con tiempos de acceso de 70 ó 60 ns y fueron muy populares en sistemas basados en el 486 y los primeros Pentium. EDO-RAM (Extended Data Output RAM) Lanzada en 1995 y con tiempos de accesos de 40 o 30 ns suponía una mejora sobre su antecesora la FPM. La EDO, también es capaz de enviar direcciones contiguas pero direcciona la columna que va utilizar mientras que se lee la información de la columna anterior, dando como resultado una eliminación de estados de espera, manteniendo activo el búffer de salida hasta que comienza el próximo ciclo de lectura. BEDO-RAM (Burst Extended Data Output RAM) Fue la evolución de la EDO RAM y competidora de la SDRAM, fue presentada en 1997. Era un tipo de memoria que usaba generadores internos de direcciones y accedía a más de una posición de memoria en cada ciclo de reloj, de manera que lograba un desempeño un 50% mejor que la EDO. Nunca salió al

- 35. mercado, dado que Intel y otros fabricantes se decidieron por esquemas de memoria sincrónicos que si bien tenían mucho del direccionamiento MOSTEK, agregan funcionalidades distintas como señales de reloj. [editar]Tecnologías de memoria La tecnología de memoria actual usa una señal de sincronización para realizar las funciones de lectura- escritura de manera que siempre esta sincronizada con un reloj delbus de memoria, a diferencia de las antiguas memorias FPM y EDO que eran asíncronas. Hace más de una década toda la industria se decantó por las tecnologías síncronas, ya que permiten construir integrados que funcionen a una frecuencia superior a 66 MHz. Tipos de DIMMs según su cantidad de Contactos o Pines: 72-pin SO-DIMM (not the same as a 72-pin SIMM), usadospor FPM DRAM y EDO DRAM 100-pin DIMM, usados por printer SDRAM 144-pin SO-DIMM, usados por SDR SDRAM 168-pin DIMM, usadospor SDR SDRAM (less frequently for FPM/EDO DRAM in workstations/servers) 172-pin MicroDIMM, usados por DDR SDRAM 184-pin DIMM, usados por DDR SDRAM 200-pin SO-DIMM, usados por DDR SDRAM y DDR2 SDRAM 204-pin SO-DIMM, usados por DDR3 SDRAM 240-pin DIMM, usados por DDR2 SDRAM, DDR3 SDRAM y FB-DIMM DRAM 244-pin MiniDIMM, usados por DDR2 SDRAM Memorias RAM con tecnologías usadas en la actualidad. [editar]SDR SDRAM

- 36. Artículo principal: SDRAM. Memoria síncrona, con tiempos de acceso de entre 25 y 10 ns y que se presentan en módulos DIMM de 168 contactos. Fue utilizada en los Pentium II y en los Pentium III , así como en los AMD K6, AMD Athlon K7 y Duron. Está muy extendida la creencia de que se llama SDRAM a secas, y que la denominación SDR SDRAM es para diferenciarla de la memoria DDR, pero no es así, simplemente se extendió muy rápido la denominación incorrecta. El nombre correcto es SDR SDRAM ya que ambas (tanto la SDR como la DDR) son memorias síncronas dinámicas. Los tipos disponibles son: PC66: SDR SDRAM, funciona a un máx de 66,6 MHz. PC100: SDR SDRAM, funciona a un máx de 100 MHz. PC133: SDR SDRAM, funciona a un máx de 133,3 MHz. [editar]RIMM RDRAM Artículo principal: RIMM RDRAM. Se presentan en módulos RIMM de 184 contactos. Fue utilizada en los Pentium IV . Era la memoria masrapida en su tiempo pero por su elevado costo fue rapidamente cambiada por la economica DDR. Los tipos disponibles son: PC600: RIMM RDRAM, funciona a un máx de 300 MHz. PC700: RIMM RDRAM, funciona a un máx de 356 MHz. PC800: RIMM RDRAM, funciona a un máx de 400 MHz. PC1066: RIMM RDRAM, funciona a un máx de 533 MHz. [editar]DDR SDRAM Artículo principal: DDR SDRAM. Memoria síncrona, envía los datos dos veces por cada ciclo de reloj. De este modo trabaja al doble de velocidad del bus del sistema, sin necesidad de aumentar la frecuencia de reloj. Se presenta en módulos DIMM de 184 contactos en el caso de ordenador de escritorio y en módulos de 144 contactos para los ordenadores portátiles. Los tipos disponibles son: PC1600 o DDR 200: funciona a un máx de 200 MHz. PC2100 o DDR 266: funciona a un máx de 266,6 MHz. PC2700 o DDR 333: funciona a un máx de 333,3 MHz. PC3200 o DDR 400: funciona a un máx de 400 MHz. PC4500 o DR4 400: funciona a una máx de 500 MHz [editar]DDR2 SDRAM

- 37. Módulos de memoria instalados de 256 MiB cada uno en un sistema con doble canal. Artículo principal: DDR2. Las memorias DDR 2 son una mejora de las memorias DDR (Double Data Rate), que permiten que los búferes de entrada/salida trabajen al doble de la frecuencia del núcleo, permitiendo que durante cada ciclo de reloj se realicen cuatro transferencias. Se presentan en módulos DIMM de 240 contactos. Los tipos disponibles son: PC2-4200 o DDR2-533: funciona a un máx de 533,3 MHz. PC2-5300 o DDR2-667: funciona a un máx de 666,6 MHz. PC2-6400 o DDR2-800: funciona a un máx de 800 MHz. PC2-8600 o DDR2-1066: funciona a un máx de 1066,6 MHz. PC2-9000 o DDR2-1200: funciona a un máx de 1200 MHz [editar]DDR3 SDRAM Artículo principal: DDR3. Las memorias DDR 3 son una mejora de las memorias DDR 2, proporcionan significantes mejoras en el rendimiento en niveles de bajo voltaje, lo que lleva consigo una disminución del gasto global de consumo. Los módulos DIMM DDR 3 tienen 240 pines, el mismo número que DDR 2; sin embargo, los DIMMs son físicamente incompatibles, debido a una ubicación diferente de la muesca. Los tipos disponibles son: PC3-6400 o DDR3-800: funciona a un máx de 800 MHz. PC3-8500 o DDR3-1066: funciona a un máx de 1066,6 MHz. PC3-10600 o DDR3-1333: funciona a un máx de 1333,3 MHz. PC3-12800 o DDR3-1600: funciona a un máx de 1600 MHz.

- 38. PC3-14900 o DDR3-1866: funciona a un máx de 1866,6 MHz. PC3-17000 o DDR3-2133: funciona a un máx de 2133,3 MHz. [editar]Módulos de la memoria RAM Formato SO-DIMM. Los módulos de memoria RAM son tarjetas de circuito impreso que tienen soldados integrados de memoria DRAM por una o ambas caras. La implementación DRAM se basa en una topología de Circuito eléctrico que permite alcanzar densidades altas de memoria por cantidad de transistores, logrando integrados de cientos o miles de megabits. Además de DRAM, los módulos poseen un integrado que permiten la identificación de los mismos ante el computador por medio del protocolo de comunicación SPD. La conexión con los demás componentes se realiza por medio de un área de pines en uno de los filos del circuito impreso, que permiten que el modulo al ser instalado en un zócalo apropiado de la placa base, tenga buen contacto eléctrico con los controladores de memoria y las fuentes de alimentación. Los primeros módulos comerciales de memoria eran SIPP de formato propietario, es decir no había un estándar entre distintas marcas. Otros módulos propietarios bastante conocidos fueron los RIMM, ideados por la empresa RAMBUS. La necesidad de hacer intercambiable los módulos y de utilizar integrados de distintos fabricantes condujo al establecimiento de estándares de la industria como los JEDEC. Módulos SIMM: Formato usado en computadores antiguos. Tenían un bus de datos de 16 o 32 bits Módulos DIMM: Usado en computadores de escritorio. Se caracterizan por tener un bus de datos de 64 bits. Módulos SO-DIMM: Usado en computadores portátiles. Formato miniaturizado de DIMM. [editar]Relación con el resto del sistema

- 39. Diagrama de la arquitectura de un ordenador. Dentro de la jerarquía de memoria la RAM se encuentra en un nivel después de los registros del procesador y de las cachés en cuanto a velocidad. Los módulos de memoria se conectan eléctricamente a un controlador de memoria que gestiona las señales entrantes y salientes de los integrados DRAM. Las señales son de tres tipos: direccionamiento, datos y señales de control. En el módulo de memoria esas señales están divididas en dos buses y un conjunto misceláneo de líneas de control y alimentación, Entre todas forman el bus de memoria que conecta la RAM con su controlador: Bus de datos: Son las líneas que llevan información entre los integrados y el controlador. Por lo general están agrupados en octetos siendo de 8,16,32 y 64 bits, cantidad que debe igualar el ancho del bus de datos del procesador. En el pasado, algunos formatos de modulo, no tenían un ancho de bus igual al del procesador.En ese caso había que montar módulos en pares o en situaciones extremas, de a 4 módulos, para completar lo que se denominaba banco de memoria, de otro modo el sistema no funciona. Esa fue la principal razón para aumentar el número de pines en los módulos, igualando al ancho de bus de procesadores como el Pentium a 64 bits, a principios de los 90. Bus de direcciones: Es un bus en el cual se colocan las direcciones de memoria a las que se requiere acceder. No es igual al bus de direcciones del resto del sistema, ya que está multiplexado de manera que la dirección se envía en dos etapas.Para ello el controlador realiza temporizaciones y usa las líneas de control. En cada estándar de módulo se establece un tamaño máximo en bits de este bus, estableciendo un límite teórico de la capacidad máxima por módulo. Señales misceláneas: Entre las que están las de la alimentación (Vdd, Vss) que se encargan de entregar potencia a los integrados. Están las líneas de comunicación para el integrado de presencia que sirve para identificar cada módulo. Están las líneas de control entre las que se encuentran las llamadas RAS (rowaddressstrobe) y CAS (columnaddressstrobe) que controlan el bus de direcciones, por último están las señales de reloj en las memorias sincrónicas SDRAM.

- 40. Algunos controladores de memoria en sistemas como PC y servidores se encuentran embebidos en el llamado "North Bridge" o "Puente Norte" de la placa base. Otros sistemas incluyen el controlador dentro del mismo procesador (en el caso de los procesadores desde AMD Athlon 64 e Intel Core i7 y posteriores). En la mayoría de los casos el tipo de memoria que puede manejar el sistema está limitado por los sockets para RAM instalados en la placa base, a pesar que los controladores de memoria en muchos casos son capaces de conectarse con tecnologías de memoria distintas. Una característica especial de algunos controladores de memoria, es el manejo de la tecnología canal doble (Dual Channel), donde el controlador maneja bancos de memoria de 128 bits, siendo capaz de entregar los datos de manera intercalada, optando por uno u otro canal, reduciendo las latencias vistas por el procesador. La mejora en el desempeño es variable y depende de la configuración y uso del equipo. Esta característica ha promovido la modificación de los controladores de memoria, resultando en la aparición de nuevos chipsets (la serie 865 y 875 de Intel) o de nuevos zócalos de procesador en los AMD (el 939 con canal doble , reemplazo el 754 de canal sencillo). Los equipos de gama media y alta por lo general se fabrican basados en chipsets o zócalos que soportan doble canal o superior, como en el caso del zócalo (o socket, en inglés) 1366 de Intel, que usaba un triple canal de memoria, o su nuevo LGA 2011 que usa cuádruple canal. [editar]Detección y corrección de errores Existen dos clases de errores en los sistemas de memoria, las fallas (Hardfails) que son daños en el hardware y los errores (softerrors) provocados por causas fortuitas. Los primeros son relativamente fáciles de detectar (en algunas condiciones el diagnóstico es equivocado), los segundos al ser resultado de eventos aleatorios, son más difíciles de hallar. En la actualidad la confiabilidad de las memorias RAM frente a los errores, es suficientemente alta como para no realizar verificación sobre los datos almacenados, por lo menos para aplicaciones de oficina y caseras. En los usos más críticos, se aplican técnicas de corrección y detección de errores basadas en diferentes estrategias: La técnica del bit de paridad consiste en guardar un bit adicional por cada byte de datos, y en la lectura se comprueba si el número de unos es par (paridad par) o impar(paridad impar), detectándose así el error. Una técnica mejor es la que usa ECC, que permite detectar errores de 1 a 4 bits y corregir errores que afecten a un sólo bit. Esta técnica se usa sólo en sistemas que requieren alta fiabilidad. Por lo general los sistemas con cualquier tipo de protección contra errores tiene un costo más alto, y sufren de pequeñas penalizaciones en desempeño, con respecto a los sistemas sin protección. Para tener un sistema con ECC o paridad, el chipset y las memorias deben tener soporte para esas tecnologías. La mayoría de placas base no poseen dicho soporte.

- 41. Para los fallos de memoria se pueden utilizar herramientas de software especializadas que realizan pruebas sobre los módulos de memoria RAM. Entre estos programas uno de los más conocidos es la aplicación Memtest86+ que detecta fallos de memoria. [editar]Memoria RAM registrada Es un tipo de módulo usado frecuentemente en servidores, posee circuitos integrados que se encargan de repetir las señales de control y direcciones: las señales de reloj son reconstruidas con ayuda del PLL que está ubicado en el módulo mismo. Las señales de datos se conectan de la misma forma que en los módulos no registrados: de manera directa entre los integrados de memoria y el controlador. Los sistemas con memoria registrada permiten conectar más módulos de memoria y de una capacidad más alta, sin que haya perturbaciones en las señales del controlador de memoria, permitiendo el manejo de grandes cantidades de memoria RAM. Entre las desventajas de los sistemas de memoria registrada están el hecho de que se agrega un ciclo de retardo para cada solicitud de acceso a una posición no consecutiva y un precio más alto que los módulos no registrados. La memoria registrada es incompatible con los controladores de memoria que no soportan el modo registrado, a pesar de que se pueden instalar físicamente en el zócalo. Se pueden reconocer visualmente porque tienen un integrado mediano, cerca del centro geométrico del circuito impreso, además de que estos módulos suelen ser algo más altos.4 Durante el año 2006 varias marcas lanzaron al mercado sistemas con memoria FB-DIMM que en su momento se pensaron como los sucesores de la memoria registrada, pero se abandono esa tecnología en 2007 dado que ofrecía pocas ventajas sobre el diseño tradicional de memoria registrada y los nuevos modelos con memoria DDR3.5 Interrupción Este artículo o sección necesita referencias que aparezcan en una publicación acreditada, como revistas especializadas, monografías, prensa diaria o páginas de Internet fidedignas. Puedes añadirlas así o avisar al autor principal del artículo en su página de discusión pegando: {{subst:Avisoreferencias|Interrupción}} ~~~~ Interrupción (también conocida como interrupción de hardware o petición de interrupción) es una señal recibida por el procesador de un ordenador, indicando que debe "interrumpir" el curso de ejecución actual y pasar a ejecutar código específico para tratar esta situación. Una interrupción es una suspensión temporal de la ejecución de un proceso, para pasar a ejecutar una subrutina de servicio de interrupción, la cual, por lo general, no forma parte del programa (generalmente

- 42. perteneciente al sistema operativo, o al BIOS). Luego de finalizada dicha subrutina, se reanuda la ejecución del programa. Las interrupciones surgen de las necesidades que tienen los dispositivos periféricos de enviar información al procesador principal de un sistema de computación. La primera técnica que se empleó fue que el propio procesador se encargara de sondear (polling) los dispositivos cada cierto tiempo para averiguar si tenía pendiente alguna comunicación para él. Este método presentaba el inconveniente de ser muy ineficiente, ya que el procesador constantemente consumía tiempo en realizar todas las instrucciones de sondeo. El mecanismo de interrupciones fue la solución que permitió al procesador desentenderse de esta problemática, y delegar en el dispositivo la responsabilidad de comunicarse con el procesador cuando lo necesitara. El procesador, en este caso, no sondea a ningún dispositivo, sino que queda a la espera de que estos le avisen (le "interrumpan") cuando tengan algo que comunicarle (ya sea un evento, una transferencia de información, una condición de error, etc.). Contenido [ocultar] 1 Funcionamiento del mecanismo de interrupciones 2 Líneas de petición de interrupción 3 Mecanismo de interrupciones en un PC 4 Tipos de interrupciones 5 Usos de las interrupciones o 5.1 Interrupciones de hardware o 5.2 Trampas o 5.3 Interrupciones por software 6 Determinación de la dirección de la rutina de servicio de interrupción 7 Direcciones variables 8 Determinación de la fuente que genera la interrupción 9 Sistemas de prioridad o 9.1 Interrupciones simultáneas o 9.2 Interrupciones anidadas o 9.3 Inhibición de interrupciones 10 Tormenta de interrupciones 11 Véase también

- 43. [editar]Funcionamiento del mecanismo de interrupciones Cada dispositivo que desea comunicarse con el procesador por medio de interrupciones debe tener asignada una línea única capaz de avisar al CPU que le requiere para una operación. Esta línea es la llamada IRQ ("InterruptReQuest", petición de interrupción). Las IRQ son líneas que llegan al controlador de interrupciones un componente de hardware dedicado a la gestión de las interrupciones, y que puede estar integrado en el procesador principal o ser un circuito separado conectado al procesador principal. El controlador de interrupciones debe ser capaz de habilitar o inhibir líneas de interrupción (operación llamada comúnmente enmascarar por la utilización de una máscara), y establecer prioridades entre las distintas interrupciones habilitadas. Cuando varias líneas de petición de interrupción se activan a la vez, el controlador de interrupciones utilizará estas prioridades para escoger la interrupción sobre la que informará al procesador principal. También puede darse el caso de que una rutina de tratamiento de interrupción sea interrumpida para realizar otra rutina de tratamiento de una interrupción de mayor prioridad a la que se estaba ejecutando.Sin embargo hay interrupciones que no se pueden enmascarar o deshabilitar, las conocidas como interrupciones no enmascarables o NMI. Un procesador principal que no tenga un controlador de interrupciones integrado, suele tener una única línea de interrupción llamada habitualmente INT. Esta línea es activada por el controlador de interrupciones cuando tiene una interrupción que servir. Al activarse esta línea, el procesador consulta los registros del controlador de interrupciones para averiguar cual IRQ hay que atender. A partir del número del IRQ busca en la tabla de vectores de interrupción la dirección de la rutina que debe llamar para atender una petición del dispositivo asociado a dicha IRQ. Las rutinas de interrupción generalmente toman un pequeño y orejon tiempo de ejecución. Pasos para el procesamiento de una IRQ: 1. Terminar la ejecución de la instrucción de máquina en curso. 2. Salva el valor de contador de programa, IP, en la pila, de manera que en la CPU, al terminar el proceso, pueda seguir ejecutando el programa a partir de la última instrucción. 3. La CPU salta a la dirección donde está almacenada la rutina de servicio de interrupción (InterruptServiceRoutine (ISR)) y ejecuta esa rutina que tiene como objetivo atender al dispositivo que generó la interrupción. 4. Una vez que la rutina de la interrupción termina, el procesador restaura el estado que había guardado en la pila en el paso 2 y retorna al programa que se estaba usando anteriormente. [editar]Líneas de petición de interrupción

- 44. El bus de control dispone de líneas específicas para el sistema de interrupciones. En el IBM PC y XT existen 8 líneas de petición de interrupción manejadas por el controlador de interrupciones Intel 8259. Estas líneas están numeradas del 0 al 7, las dos primeras están asignadas al timertick del temporizador Intel 8253, y al teclado. Solo quedaban 6 líneas para otros dispositivos, que aparecen como tales en el bus de control (IRQ2 - IRQ7). A partir del modelo AT se añadieron otras 8 líneas, numeradas del 8 al 15, mediante un segundo controlador de interrupciones (PIC), aunque la tecnología empleada exigió colgarlo de la línea IRQ2 del primero, de forma que esta línea se dedica a atender las interrupciones del segundo controlador a través de la línea 9 de este último, y la línea 8 se dedicó al reloj de tiempo real, un dispositivo que no existía en los modelos XT. Aunque internamente se manejan 16 líneas, no todas tienen contacto en los zócalos del bus externo (son las marcadas con asterisco en la tabla que sigue). La razón de esta ausencia en los zócalos de conexión es que son de asignación fija, y solo son usadas por ciertos dispositivos instalados en la propia placa base. En concreto la línea NMI está asignada al mecanismo de control de paridad de la memoria, la línea 0 está asignada al cronómetro del sistema y la línea 1 al chip que controla el teclado (dispositivos que pueden requerir atención urgente por parte del procesador). Es costumbre denominar IRQx a las que tienen prolongación en el bus. Teóricamente las restantes líneas podrían ser asignadas a cualquier nuevo dispositivo, pero en la práctica algunas están reservadas a dispositivos estándar. Por ejemplo, IRQ3 está casi siempre asignado al puerto serie COM2 y el IRQ4 al COM1; IRQ6 al controlador estándar de disquetes y IRQ7 al puerto de impresora LPT1. La tabla 1 muestra las asignaciones clásicas para el XT y el AT En sistemas más modernos utilizan la arqitectura APIC de Intel con 24 líneas y 8 extra para enrutar las interrupciones PCI. Nombre Int (hex) XT: Descripción AT: Descripción NMI --- Paridad* Paridad* 0 08 Temporizador* Temporizador* 1 09 Teclado* Teclado* IRQ2 0A Reservado Interrupciones 8 a 15 (PIC#2)

- 45. IRQ3 0B Puertos serie COM2/COM4 Puerto serie COM2/COM4 IRQ4 0C Puertos serie COM1/COM3 Puertos serie COM1/COM3 IRQ5 0D Disco duro Impresora secundaria LPT2 IRQ6 0E Disquete Disquete IRQ7 0F Impresora primaria LPT1 Impresora primaria LPT1 8 70 No aplicable Reloj de tiempo real* 9 71 No aplicable Redirigido a IRQ2* IRQ10 72 No aplicable no asignado IRQ11 73 No aplicable no asignado IRQ12 74 No aplicable Ratón PS2 13 75 No aplicable Coprocesador 80287* IRQ14 76 No aplicable Contr. disco IDE primario IRQ15 77 No aplicable Contr. disco IDE secundario Cuando se instala un dispositivo de E/S que puede necesitar atención del procesador, debe asignársele una IRQ adecuada. Dicho en otras palabras, cuando requiera atención debe enviar una señal en la línea IRQ especificada. Inicialmente esta asignación se efectuaba de forma manual, por medio de puentes (jumpers) en la placa o dispositivo, pero actualmente esta selección puede hacerse por software. [editar]Mecanismo de interrupciones en un PC

- 46. Un ordenador PC típico dispone en su placa base de un controlador de interrupciones 8259 de Intel o de un circuito integrado análogo. Este dispositivo electrónico dispone de hasta 16 líneas IRQ, numeradas desde el 00 hasta el 15. En las nuevas placas base este circuito está integrado junto con el resto del chipset y permite hasta 24 interrupciones. [editar]Tipos de interrupciones En este subapartado vamos a hacer una clasificación de las distintas clases de interrupciones que nos podemos encontrar atendiendo a la fuente que las produce. Por un lado distinguiremos si se producen por causas internas o externas al procesador y remarcaremos que este hecho está íntimamente ligado con que las interrupciones sean síncronas o asíncronas: Interrupciones de hardware. Estas son asíncronas a la ejecución del procesador, es decir, se pueden producir en cualquier momento independientemente de lo que esté haciendo el CPU en ese momento. Las causas que lo producen son externas al procesador y a menudo suelen estar ligadas con distintos dispositivos de E/S. Traps. Normalmente son causadas al realizarse operaciones no permitidas tales como la división por 0, el desbordamiento, el acceso a una posición de memoria no permitida, etc. Interrupciones por software. Las interrupciones por software son generadas por el programa en ejecución. Para generarla, existen distintas instrucciones en el código máquina que permiten al programador producir una interrupción, suelen tener nemotécnicos tales como INT. Suelen ser de vital importancia ya que a partir de estas interrupciones se solicita al sistema operativo realizar determinadas funciones, para ello. Por ejemplo, en DOS se realiza la instrucción INT 0x21 y en Unix se utiliza INT 0x80 para hacer llamadas de sistema. [editar]Usos de las interrupciones Se utilizan las interrupciones generalmente para dos motivos: Permitir una comunicación sin bloqueo con los periféricos externos. Conmutar las tareas dentro de un planificador [editar]Interrupciones de hardware Son interrupciones que se producen como resultado de, normalmente, una operación de E/S. No son producidas por ninguna instrucción de un programa sino por señales que producen los dispositivos para indicarle al procesador que necesitan ser atendidos. Las interrupciones de hardware son interesantes en cuanto a que permiten mejorar la productividad del procesador ya que este último puede ordenar una operación de E/S y en lugar de tener que esperar realizando una espera activa, a que el dispositivo termine, es decir, sin hacer ningún trabajo útil, se puede dedicar a atender a otro proceso o aplicaciones

- 47. y cuando el dispositivo esté de nuevo disponible será el encargado de notificarle al procesador mediante la línea de interrupción que ya está preparado para continuar/terminar la operación de E/S. Entradas/salidas: Cuando un microprocesador accesa un periférico (disco duro, puerto de comunicación...), puede transcurrir algún tiempo antes de que los datos puedan ser obtenidos o bien transmitidos. La solución más simple es esperar hasta recibir un dato o bien hasta que se efectúa una transmisión (espera ocupado, o polling), pero esta solución bloquea todos los programas en ejecución, y eso no puede admitirse bajo un sistema multitarea. En los sistemas modernos se prefiere un funcionamiento mediante interrupciones: El periférico señala una eventualidad mediante una interrupción, como por ejemplo que ha acabado la transmisión de los datos, y una rutina trata esta interrupción. Para que la transferencia sea más eficiente suele usarse el acceso directo a memoria (DMA), mediante el cual los bloques son leídos o bien escritos en memoria sin la intervención del CPU. [editar]Trampas Es un tipo de interrupción sincrónica típicamente causada por una condición de error, por ej. una división por 0 o un acceso inválido a memoria en un proceso de usuario. Normalmente genera un cambio de contexto a modo supervisor para que el sistema operativo atienda el error. De manera que podemos ver como las excepciones son un mecanismo de protección que permite garantizar la integridad de los datos tanto en el espacio de usuario como en el espacio kernel. El SO cuando detecta una excepción intenta solucionarla pero en caso de no poder simplemente notificará la condición de error a la aplicación y abortará la misma. [editar]Interrupciones por software Este artículo o sección tiene un estilo difícil de entender para los lectores interesados en el tema. Si puedes, por favor edítalo y contribuye a hacerlo más accesible para el público general, sin eliminar los detalles técnicos que interesan a los especialistas. A las interrupciones por software, se las denomina excepciones. En este apartado se consideran las llamadas al sistema operativo mediante una instrucción, normalmente de Entrada/Salida, por ejemplo una división por 0. Una interrupción por software, se generará por un programa mientras está ejecutándose. En general actúa de la siguiente manera:

- 48. 1. Un programa que se venía ejecutando luego de su instrucción I5 , llama al Sistema Operativo, por ejemplo para leer un archivo de disco.(cuando un programa necesita un dato exterior , se detiene y pasa a cumplir con las tareas de recojer ese dato) 1. A tal efecto, luego de I5 existe en el programa, la instrucción de código de máquina CD21, simbolizada INT 21 en Assembler, que realiza el requerimiento del paso 1. Puesto que no puede seguir le ejecución de la instrucción I6 y siguientes del programa hasta que no se haya leído el disco y esté en memoria principal dicho archivo, virtualmente el programa se ha interrumpido, siendo, además, que luego de INT 21, las instrucciones que se ejecutarán no serán del programa, sino del Sistema Operativo. ( se detiene el programa y ordena en este caso mediante INT21 ( interrupcion predefinida ) que recoge el dato solicitado, para poder sequir el programa que la ordeno ) 1. La ejecución de INT 21 permite hallar la subrutina del Sistema Operativo. 1. Se ejecuta la subrutina del Sistema Operativo que prepara la lectura del disco. 1. Luego de ejecutarse la subrutina del Sistema Operativo, y una vez que se haya leído el disco y verificado que la lectura es correcta, el Sistema Operativo ordenará reanudar la ejecución del programa autointerrumpido en espera. 1. La ejecución del programa se reanuda. [editar]Determinación de la dirección de la rutina de servicio de interrupción Hay dos alternativas para determinar la dirección de la rutina de servicio de interrupción que debe ejecutarse al recibir una interrupción determinada: Direcciones fijas. Se hallan cableadas en el procesador y por tanto nunca pueden ser cambiadas. Esto implica que las RSI siempre estarán en una determinada posición de la memoria. Direcciones variables (por interrupciones vectorizadas). En este grupo se incluyen aquellas que presentan una dirección variable y que, por tanto, no se halla cableada en el procesador. De esta manera el dispositivo debe dar información acerca de la localización de la dirección de comienzo de la RSI asociada a dicho periférico. [editar]Direcciones variables

- 49. Hay distintas metodologías de diseño para las interrupciones con direcciones variables. En la actualidad, las alternativas que son implementadas de manera habitual son las siguientes: Direccionamiento absoluto. En este caso es el dispositivo o la interfaz del dispositivo la encargada de conocer la dirección de la RSI y de enviarla al procesador para que éste pueda localizar dicha subrutina y ejecutarla. Direccionamiento relativo. El dispositivo solo suministra parte de la dirección de comienzo y es el procesador el encargado de completarla (añadiendo bits o sumando una determinada cantidad, que siempre será fija). Esta alternativa tiene una ventaja sobre la anterior y es que permite especificar la dirección de comienzo con menos bits y por tanto simplifica el diseño. Ahora bien tiene una desventaja principal y es que limita el número de dispositivos que podemos conectar y además ciertos bits de la dirección quedan fijados de forma permanente por la CPU lo que reduce la capacidad de reubicabilidad de la RSI. Una alternativa que utilizan ciertos procesadores como el 8080 o el 8085 es que en vez de enviar solamente la dirección de comienzo de la RSI se envía también el código de la operación de salto (por ejemplo CALL). Direccionamiento indirecto. También conocida como direccionamiento por interrupciones vectorizadas. Se mantiene una tabla de vectores de interrupción (direcciones de comienzo de las distintas RSI) y a cada interrupción se le asocia un número que será el índice por el cual se accederá a la tabla y se recuperará la información de la dirección de comienzo. Necesita señales de conformidad o handshaking para sincronizar al procesador con la interfaz, ya que esta última tiene que indicarle al procesador cuando va a enviarle el índice que necesita para buscar el vector de interrupción (INT) y el procesador deberá enviar otra señal para indicar que se ha reconocido la interrupción (INTA#). [editar]Determinación de la fuente que genera la interrupción Hay distintas formas de identificar la fuente de una determinada interrupción. La primera alternativa que se consideró fue asignar una línea (un bit) para cada interrupción pero esto suponía un gran costo en cuanto a la relación de número de dispositivos y número de bits usados y a menudo fijaba el límite de dispositivos que se podían conectar. Por tanto, se pensó con posterioridad que en cada patilla de interrupción deberían poder conectarse más de un dispositivo, pero entonces tendríamos que imponer una metodología que permitiese identificar de forma unívoca de qué dispositivo se trataba. Para ello hay varias directrices: Polling. Se trata de que la CPU comprueba de manera sistemática todos los dispositivos de manera que "busca" cuál de ellos fue el que solicitó la interrupción. Esto tiene una ventaja y es que es barato a nivel de coste hardware ya que el "polling" se implementa en software, no obstante tiene

- 50. otras desventajas que no podemos olvidar y es que suele ser lento porque tiene que comprobar en serie todos los dispositivos y establece una prioridad en los dispositivos (el orden de sondeo) y por tanto puede provocar inanición. Interrupciones vectorizadas. Este concepto fue ya tratado en el apartado anterior y como ventajas podemos destacar que suele ser rápido pero implica un alto costo en el hardware. Hardware paralelo. Se utiliza un registro de interrupción cuyos bits se controlan de forma independiente por las señales de petición de interrupción de cada periférico. Según la posición de cada bit en el registro, se establece la prioridad. [editar]Sistemas de prioridad Se necesita un mecanismo para priorizar las interrupciones y tratar primero las más urgentes. Existen varias alternativas: Interrupciones simultáneas. No tienen por qué ocurrir de manera simultánea sino que se refiere a que en un momento dado pueden haber varias interrupciones activas. Interrupciones anidadas. Mientras se está procesando una determinada rutina de servicio de interrupción sucede otra señal de interrupción. Inhibición de interrupciones. Se deshabilitan las demás interrupciones mientras se está tratando una. [editar]Interrupciones simultáneas En este método tenemos dos alternativas, una de ellas es que exista algún hardware que tenga como entradas las señales de interrupción y de como salida la interrupción más prioritaria que está activa en ese momento. Otra alternativa es tener un método de identificación de prioridades distribuida y no generalizada como en el caso anterior, en este caso tenemos que destacar dos técnicas distintas que se pueden implementar en la práctica: Polling. Como ya vimos es el CPU el que chequea los dispositivos y el orden de sondeo determina la prioridad. Daisy-chain. (conexión en cadena) Podemos conectar los distintos dispositivos en cadena, en orden decreciente de prioridad y por tanto la señal de reconocimiento de interrupción (INTA#) solo será pasada al siguiente dispositivo en caso de que el anterior (más prioritario) no haya solicitado los servicios del procesador. Sin embargo, algo importante es que las señales de interrupción que van al procesador están conectadas todas a un mismo cable, por tanto, deberemos utilizar alguna técnica especial para que no se produzca un cortocircuito. Para evitar precisamente que la pista se cortocircuite se utiliza la técnica del "open-collector" o "colector abierto" y consiste en conectar el colector de un transistor a la pista común (un transistor por cada dispositivo) y por tanto estarán

- 51. tantos colectores conectados como dispositivos tengamos (se entiende que son dispositivos que mandan petición de interrupción al procesador). Híbrida. Mezcla las dos técnicas explicadas anteriormente. [editar]Interrupciones anidadas Existen dos métodos para tratar las interrupciones anidadas. El primero se basa en inhabilitar las interrupciones mientras se está ejecutando una determinada RSI. Esto puede realizarlo el hardware de manera automática en algunos procesadores, pero en otros será el usuario el encargado de deshabilitarlas en caso de que no desee que ninguna otra interrupción pueda interrumpir el transcurso normal de la rutina de servicio de interrupción. No es aconsejable deshabilitar las interrupciones durante mucho tiempo ya que esto puede provocar errores y pérdida de información. La otra alternativa es permitir que solo las interrupciones más prioritarias puedan suspender la ejecución de la RSI actual. Para esto tendremos que definir qué líneas son más prioritarias que otras. Otra consideración de esta segunda alternativa es que al anidar distintas llamadas a rutinas tendremos que contar con una pila suficientemente grande para que esta no se desborde. [editar]Inhibición de interrupciones Hay distintas alternativas de inhibición de interrupciones. Como ya hemos visto estas se pueden hacer de manera automática por el hardware en algunos casos mientras que en otros será el usuario el encargado de realizarlo por software y esto depende de la arquitectura del procesador que consideremos. Las distintas opciones son: Deshabilitar todas las interrupciones. Para esto basta con inhibir el bit del registro de flag dedicado a las interrupciones. Deshabilitar al principio de la RSI y activarlas de nuevo al finalizar la misma. Puede ser de manera automática o por el usuario. Desactivar solo las interrupciones que tengan menor prioridad que la asociada a la RSI que se está ejecutando en ese momento. Deshabilitar de forma selectiva distintos niveles de prioridad de interrupción. Para lo cual se emplean registros especiales denominados máscaras en el que cada uno de sus bits identifican a un nivel distinto y modificando su contenido se puede establecer que niveles están activos en ese momento. Se puede cambiar por el programador. [editar]Tormenta de interrupciones Este evento se puede producir cuando un procesador recibe un número demasiado grande de interrupciones, las cuales consumen la mayor parte del tiempo del procesador. Las tormentas de

- 52. interrupciones suelen ser causadas por dispositivos de hardware que no son compatibles con una tasa de interrupción limitante. Como curiosidad, se conjetura que la primera tormenta de interrupciones pudo ocurrir durante el descenso lunar del Apollo 11 en 1969. [editar]Véase también Modos de direccionamiento Los llamados modos de direccionamiento son las diferentes maneras de especificar en informática un operando dentro de una instrucción en lenguaje ensamblador. Un modo de direccionamiento especifica la forma de calcular la dirección de memoria efectiva de un operando mediante el uso de la información contenida en registros y / o constantes, contenida dentro de una instrucción de la máquina o en otra parte. Contenido [ocultar] 1 ¿Cuántos modos de direccionamiento existen? 2 Advertencia 3 Tipos de Direccionamiento o 3.1 Implícito o 3.2 Inmediato o 3.3 Directo o 3.4 Indirecto o 3.5 Absoluto o 3.6 De registro o 3.7 Indirecto mediante registros o 3.8 De desplazamiento o 3.9 De pila o 3.10 Respecto a un registro base o 3.11 Respecto a un registro índice o 3.12 Respecto al contador de programa o 3.13 Indexado con autoincremento/autodecremento o 3.14 Instrucción de salto con direccionamiento absoluto o 3.15 Instrucción de salto con direccionamiento relativo