Examen arch

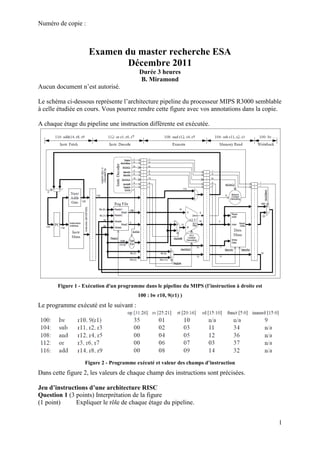

- 1. Numéro de copie : 1 Examen du master recherche ESA Décembre 2011 Durée 3 heures B. Miramond Aucun document n’est autorisé. Le schéma ci-dessous représente l’architecture pipeline du processeur MIPS R3000 semblable à celle étudiée en cours. Vous pourrez rendre cette figure avec vos annotations dans la copie. A chaque étage du pipeline une instruction différente est exécutée. Figure 1 - Exécution d'un programme dans le pipeline du MIPS (l’instruction à droite est 100 : lw r10, 9(r1) ) Le programme exécuté est le suivant : Figure 2 - Programme exécuté et valeur des champs d’instruction Dans cette figure 2, les valeurs de chaque champ des instructions sont précisées. Jeu d’instructions d’une architecture RISC Question 1 (3 points) Interprétation de la figure (1 point) Expliquer le rôle de chaque étage du pipeline.

- 2. Numéro de copie : 2 (1 point) Pour quel type d’instruction génère-t-on le signal MemWr et le signal MemRd (sous la Data Mem dans la figure 1) ? (1 point) Indiquer plusieurs éléments de différence entre une architecture RISC et une architecture CISC. Question 2 (2,5 points) Indiquer quel format de codage correspond aux instructions suivantes : SUB, Rd := Rs - Rt ORI, Rd := s(Imm) or Rs SLA, Rd := s(Ra << 1) BGE, PC := PC + Rb if Rs >= 0 BRI, PC := PC + s(Imm) Dans les sémantiques des instructions précédentes, s(x) indique une extension de signe à 32 bits de x. Vous préciserez la signification de chaque type d’instruction de ce programme. Question 3 (1,5 points) Représentez par des figures le codage sur 32 bits d’une instruction dans les différents formats de la question précédente (jeu d’instruction MIPS-IV). Performances Pour la plupart des instructions l’exécution de chaque étage prend 1 cycle, et le temps d’exécution d’une instruction est alors égal au nombre d’étages. Cependant, certaines instructions complexes demandent plusieurs cycles pour effectuer l’étage d’exécution. Ceci ne tient pas compte d’éventuels aléas d’accès à la mémoire qui peuvent retarder certaines instructions ou encore d’éventuels conflits dans le pipeline. Question 4 (4 points) Les instructions de calcul flottant (FADD, FSUB, FMUL) prennent par exemple 6 cycles dans l’étage EX. Et l’instruction de division flottante FDIV prend 30 cycles avec un circuit de calcul flottant FPU classique. On étudie une application qui après compilation serait composée de 100.000 instructions réparties de la manière décrite dans le tableau ci-dessous. Le programme peut s’exécuter soit sur des nombres entiers soit sur des nombres flottants (lignes 5 et 6) di le processeur dispose d’une FPU. Instruction Pourcentage d’apparition par rapport au nombre total d’instructions du programme 1 LW 23% 2 ADD 14% 3 FLT 13% 4 SW 12% 5 (F)ADD 11% 6 (F)DIV 8% 7 BNE 7% 8 CALL 5% 9 RTSD 5% 10 SRL 2% En négligeant les aléas de pipeline et de mémoire, quel est le temps d’exécution de ce programme travaillant en virgule fixe ? Quel est le temps d’exécution de ce programme travaillant en virgule flottante ?

- 3. Numéro de copie : 3 Quel serait l’accélération obtenue si l’on réalisait une FPU 2 fois plus rapide que la précédente ? Vous préciserez la signification de chaque type d’instruction de ce programme. Fonctionnement du pipeline Question 5 (2 point) Dans la figure 2, en supposant que l’instruction 104 devienne sub r4, r2, r3 ajouter à l’architecture un mécanisme permettant de conserver le remplissage du pipeline. Faites un schéma à part. Expliquer son fonctionnement. Question 6 (4 points) Expliquez comment fonctionne une instruction de saut conditionnel sans prise en compte du mode pipeline. Pour cela, vous surlignerez le chemin de donnée emprunté ainsi que les signaux spécifiques à positionner. Pour ce type d’instruction, expliquer ce que fait le contrôleur de l’architecture, en prenant en compte le mode pipeline, vis-à-vis des autres instructions entrée dans le pipeline. Quelle solution est communément employée pour garder le remplissage maximum du pipeline dans ce cas ? Architecture multiprocesseur Question 7 (4 points) On cherche à implanter une application se résumant à une somme matricielle S de 2 tableaux entiers bidimensionnels M1 et M2 de taille 1000x1000 telle que S=∑ i=0 999 ∑ i=0 999 M1i, j∗M2i , j On voudrait déterminer l’architecture multiprocesseur qui offre le meilleur temps d’exécution. En supposant un modèle multiprocesseur à mémoire partagée, une lecture mémoire est supposée prendre un nombre de cycle égal au nombre de processeur (1cycle pour 1 proc, 2 cycles pour 2 proc…) à cause des problèmes d’arbitrage et de cohérence de cache. L’écriture prend quant à elle toujours 1 cycle. Sachant que le pipeline permet de démarrer une instruction par cycle (supposé sans conflit dans cette question), quel est le nombre de processeur optimal pour cette application ? Expliquez.