Denunciar

Compartir

Recomendados

Más contenido relacionado

La actualidad más candente

La actualidad más candente (20)

Enrichment towards the design of efficient 4 bit reversible subtractor 2

Enrichment towards the design of efficient 4 bit reversible subtractor 2

Eceg 3201-dld-lec 11-registers_and_asynchoronous_counters

Eceg 3201-dld-lec 11-registers_and_asynchoronous_counters

Low Power Area Efficient Arithmetic and Logical Control Unit Using Reversible...

Low Power Area Efficient Arithmetic and Logical Control Unit Using Reversible...

A Computers Architecture project on Barrel shifters

A Computers Architecture project on Barrel shifters

Similar a Lecture 2

Similar a Lecture 2 (20)

A Wireless Application of The Rain, Humidity and Temperature Sensors Based on...

A Wireless Application of The Rain, Humidity and Temperature Sensors Based on...

Design and Implementation of FPGA Based Low Power Pipelined 64 Bit Risc Proce...

Design and Implementation of FPGA Based Low Power Pipelined 64 Bit Risc Proce...

Digital Electronics viva and interview questions-min.pdf

Digital Electronics viva and interview questions-min.pdf

Digital Electronics viva and interview questions-min.pdf

Digital Electronics viva and interview questions-min.pdf

IRJET- Analog to Digital Conversion Process by Matlab Simulink

IRJET- Analog to Digital Conversion Process by Matlab Simulink

Más de RahulRathi94

Más de RahulRathi94 (20)

Lecture 2

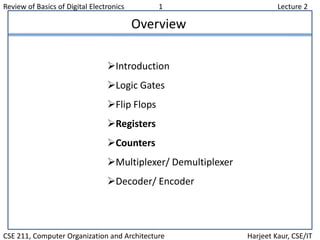

- 1. Review of Basics of Digital Electronics 1 Lecture 2 CSE 211, Computer Organization and Architecture Harjeet Kaur, CSE/IT Overview Introduction Logic Gates Flip Flops Registers Counters Multiplexer/ Demultiplexer Decoder/ Encoder

- 2. Review of Basics of Digital Electronics 2 Lecture 2 CSE 211, Computer Organization and Architecture Harjeet Kaur, CSE/IT Registers D Q C D Q C D Q C D Q C Clock I0 I1 I2 I3 Register With Parallel Load Clear

- 3. Review of Basics of Digital Electronics 3 Lecture 2 CSE 211, Computer Organization and Architecture Harjeet Kaur, CSE/IT Shift Register Shift Registers D Q C D Q C D Q C D Q C Serial Input Clock Serial Output

- 4. Review of Basics of Digital Electronics 4 Lecture 2 CSE 211, Computer Organization and Architecture Harjeet Kaur, CSE/IT Bidirectional Shift Register with Parallel Load Bidirectional Shift Register with Parallel Load D Q C D Q C D Q C D Q C A0 A1 A2 A3 4 x 1 MUX 4 x 1 MUX 4 x 1 MUX 4 x 1 MUX Clock S0S1 I0 I1 I2 I3