105926921 cmos-digital-integrated-circuits-solution-manual-1

•

131 recomendaciones•58,784 vistas

Denunciar

Compartir

Denunciar

Compartir

Descargar para leer sin conexión

Recomendados

Recomendados

IJRET : International Journal of Research in Engineering and Technology is an international peer reviewed, online journal published by eSAT Publishing House for the enhancement of research in various disciplines of Engineering and Technology. The aim and scope of the journal is to provide an academic medium and an important reference for the advancement and dissemination of research results that support high-level learning, teaching and research in the fields of Engineering and Technology. We bring together Scientists, Academician, Field Engineers, Scholars and Students of related fields of Engineering and Technology.Design and implementation of high speed baugh wooley and modified booth multi...

Design and implementation of high speed baugh wooley and modified booth multi...eSAT Publishing House

Más contenido relacionado

La actualidad más candente

IJRET : International Journal of Research in Engineering and Technology is an international peer reviewed, online journal published by eSAT Publishing House for the enhancement of research in various disciplines of Engineering and Technology. The aim and scope of the journal is to provide an academic medium and an important reference for the advancement and dissemination of research results that support high-level learning, teaching and research in the fields of Engineering and Technology. We bring together Scientists, Academician, Field Engineers, Scholars and Students of related fields of Engineering and Technology.Design and implementation of high speed baugh wooley and modified booth multi...

Design and implementation of high speed baugh wooley and modified booth multi...eSAT Publishing House

La actualidad más candente (20)

Fpga implementation of high speed 8 bit vedic multiplier using barrel shifter(1)

Fpga implementation of high speed 8 bit vedic multiplier using barrel shifter(1)

Design and implementation of high speed baugh wooley and modified booth multi...

Design and implementation of high speed baugh wooley and modified booth multi...

Más de Savvas Dimopoulos

Más de Savvas Dimopoulos (9)

Communication systems 4 th edition simon haykin with solutions manual

Communication systems 4 th edition simon haykin with solutions manual

105926921 cmos-digital-integrated-circuits-solution-manual-1

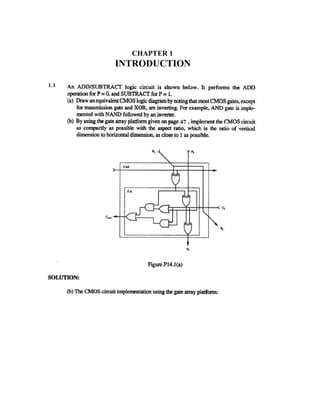

- 1. CHAPTER 1 INTRODUCTION 1.1 47

- 4. 1.2 1.1

- 8. 1.3

- 9. 1.4 1.5 1.6

- 10. 1.7

- 125. Chapter 14 DESIGN FOR MANUFACTURABILITY NOTE: All solutions numbered 15.x (x = 1 through 15) on the following pages apply to exercise problems numbered 14.x in the 3rd edition. There are no changes in the content and ordering.

- 142. Chapter 15 DESIGN FOR TESTABILITY NOTE: All solutions numbered 16.x (x = 1 through 8) on the following pages apply to exercise problems numbered 15.x in the 3rd edition. There are no changes in the content and ordering.