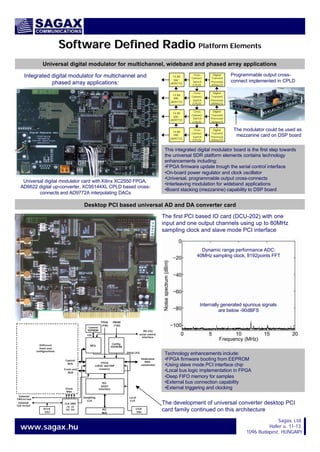

Project poster: SDR platform elements

•

0 recomendaciones•282 vistas

Denunciar

Compartir

Denunciar

Compartir

Descargar para leer sin conexión

Más contenido relacionado

La actualidad más candente

La actualidad más candente (20)

Destacado

Explotación capitalista (48 páginas). AÑO: 1971. Publicado el 12 de julio de ...

Explotación capitalista (48 páginas). AÑO: 1971. Publicado el 12 de julio de ...PERIODISTAS DE LAS CALLES

Destacado (20)

Explotación capitalista (48 páginas). AÑO: 1971. Publicado el 12 de julio de ...

Explotación capitalista (48 páginas). AÑO: 1971. Publicado el 12 de julio de ...

Composite Plate Optimization with Practical Design Constraints

Composite Plate Optimization with Practical Design Constraints

Similar a Project poster: SDR platform elements

High Performance DSP with Xilinx All Programmable Devices (Design Conference ...

High Performance DSP with Xilinx All Programmable Devices (Design Conference ...Analog Devices, Inc.

Similar a Project poster: SDR platform elements (20)

High Performance DSP with Xilinx All Programmable Devices (Design Conference ...

High Performance DSP with Xilinx All Programmable Devices (Design Conference ...

Design and Implementation of FPGA Based Signal Processing Card

Design and Implementation of FPGA Based Signal Processing Card

High Speed Data Connectivity: More Than Hardware - VE2013

High Speed Data Connectivity: More Than Hardware - VE2013

Final presentation [dissertation project], 20192 esv0002![Final presentation [dissertation project], 20192 esv0002](data:image/gif;base64,R0lGODlhAQABAIAAAAAAAP///yH5BAEAAAAALAAAAAABAAEAAAIBRAA7)

![Final presentation [dissertation project], 20192 esv0002](data:image/gif;base64,R0lGODlhAQABAIAAAAAAAP///yH5BAEAAAAALAAAAAABAAEAAAIBRAA7)

Final presentation [dissertation project], 20192 esv0002

Design and Implementation of Low Power High Speed Symmetric Decoder Structure...

Design and Implementation of Low Power High Speed Symmetric Decoder Structure...

Learn the cutting edge technologies in Data Acquistion, Industrial Control an...

Learn the cutting edge technologies in Data Acquistion, Industrial Control an...

Más de Bertalan EGED

Más de Bertalan EGED (19)

Último

Making_way_through_DLL_hollowing_inspite_of_CFG_by_Debjeet Banerjee.pptx

Making_way_through_DLL_hollowing_inspite_of_CFG_by_Debjeet Banerjee.pptxnull - The Open Security Community

Último (20)

SQL Database Design For Developers at php[tek] 2024![SQL Database Design For Developers at php[tek] 2024](data:image/gif;base64,R0lGODlhAQABAIAAAAAAAP///yH5BAEAAAAALAAAAAABAAEAAAIBRAA7)

![SQL Database Design For Developers at php[tek] 2024](data:image/gif;base64,R0lGODlhAQABAIAAAAAAAP///yH5BAEAAAAALAAAAAABAAEAAAIBRAA7)

SQL Database Design For Developers at php[tek] 2024

Human Factors of XR: Using Human Factors to Design XR Systems

Human Factors of XR: Using Human Factors to Design XR Systems

Transcript: #StandardsGoals for 2024: What’s new for BISAC - Tech Forum 2024

Transcript: #StandardsGoals for 2024: What’s new for BISAC - Tech Forum 2024

08448380779 Call Girls In Civil Lines Women Seeking Men

08448380779 Call Girls In Civil Lines Women Seeking Men

The Codex of Business Writing Software for Real-World Solutions 2.pptx

The Codex of Business Writing Software for Real-World Solutions 2.pptx

Tech-Forward - Achieving Business Readiness For Copilot in Microsoft 365

Tech-Forward - Achieving Business Readiness For Copilot in Microsoft 365

Unblocking The Main Thread Solving ANRs and Frozen Frames

Unblocking The Main Thread Solving ANRs and Frozen Frames

Transforming Data Streams with Kafka Connect: An Introduction to Single Messa...

Transforming Data Streams with Kafka Connect: An Introduction to Single Messa...

Hyderabad Call Girls Khairatabad ✨ 7001305949 ✨ Cheap Price Your Budget

Hyderabad Call Girls Khairatabad ✨ 7001305949 ✨ Cheap Price Your Budget

Making_way_through_DLL_hollowing_inspite_of_CFG_by_Debjeet Banerjee.pptx

Making_way_through_DLL_hollowing_inspite_of_CFG_by_Debjeet Banerjee.pptx

Presentation on how to chat with PDF using ChatGPT code interpreter

Presentation on how to chat with PDF using ChatGPT code interpreter

Neo4j - How KGs are shaping the future of Generative AI at AWS Summit London ...

Neo4j - How KGs are shaping the future of Generative AI at AWS Summit London ...

Azure Monitor & Application Insight to monitor Infrastructure & Application

Azure Monitor & Application Insight to monitor Infrastructure & Application

Project poster: SDR platform elements

- 1. www.www.sagaxsagax..huhu SagaxSagax,, LtdLtd.. HallerHaller u. 11-13.u. 11-13. 1096 Budapest, HUNGARY1096 Budapest, HUNGARY Software Defined RadioSoftware Defined Radio Platform ElementsPlatform Elements This integrated digital modulator board is the first step towards the universal SDR platform elements contains technology enhancements including: •FPGA firmware update trough the serial control interface •On-board power regulator and clock oscillator •Universal, programmable output cross-connects •Interleaving modulation for wideband applications •Board stacking (mezzanine) capability to DSP board Universal digital modulator card with Xilinx XC2S50 FPGA, AD6622 digital up-converter, XC95144XL CPLD based cross- connects and AD9772A interpolating DACs Integrated digital modulator for multichannel and phased array applications: 14-Bit DAC (AD9772) 14-Bit DAC (AD9772) 14-Bit DAC (AD9772) 14-Bit DAC (AD9772) Cross Connect Switch (CPLD) Cross Connect Switch (CPLD) Cross Connect Switch (CPLD) Cross Connect Switch (CPLD) Digital Transmit Processor (AD6622) Digital Transmit Processor (AD6622) Digital Transmit Processor (AD6622) Digital Transmit Processor (AD6622) Programmable output cross- connect implemented in CPLD The modulator could be used as mezzanine card on DSP board PCI HOST Interface PCI BUS FPGA LOGIC and DSP resource MCU Config EEPROM Control EEPROM PROM JTAG FPGA JTAG Dedicated data connection RS-232 serial control interface Front-end BUS Control BUS CLK DRV /2, /4 X2, X4SCLK OSC External CLK in/out LCLK OSC Sampling CLK Local CLK I2C FPGA CFG Clock lines Different front-end configurations External TRG in/out Desktop PCI based universal AD and DA converter card The development of universal converter desktop PCI card family continued on this architecture The first PCI based IO card (DCU-202) with one input and one output channels using up to 80MHz sampling clock and slave mode PCI interface Technology enhancements include: •FPGA firmware booting from EEPROM •Using slave mode PCI interface chip •Local bus logic implementation in FPGA •Deep FIFO memory for samples •External bus connection capability •External triggering and clocking Dynamic range performance ADC: 40MHz sampling clock, 8192points FFT Internally generated spurious signals are below -90dBFS Universal digital modulator for multichannel, wideband and phased array applications