Taller Paginacion Abril 12 2010

•Descargar como DOC, PDF•

0 recomendaciones•221 vistas

Taller para ser resuelto y aclarar dudas...

Denunciar

Compartir

Denunciar

Compartir

Recomendados

Manual practica final publicacion de contenidos de exe learning en moodle

Manual practica final publicacion de contenidos de exe learning en moodleDayner Felipe Ordoñez López

Más contenido relacionado

Similar a Taller Paginacion Abril 12 2010

Similar a Taller Paginacion Abril 12 2010 (20)

ARQUITECTURA DE COMPUTADORES (I Bimestre Abril agosto 2011)

ARQUITECTURA DE COMPUTADORES (I Bimestre Abril agosto 2011)

Más de Dayner Felipe Ordoñez López

Manual practica final publicacion de contenidos de exe learning en moodle

Manual practica final publicacion de contenidos de exe learning en moodleDayner Felipe Ordoñez López

Más de Dayner Felipe Ordoñez López (20)

Manual practica final publicacion de contenidos de exe learning en moodle

Manual practica final publicacion de contenidos de exe learning en moodle

Ruta de formación tutor virtual Uimayor IV cohorte

Ruta de formación tutor virtual Uimayor IV cohorte

Taller Paginacion Abril 12 2010

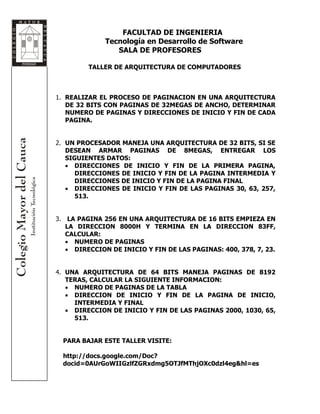

- 1. FACULTAD DE INGENIERIA Tecnología en Desarrollo de Software SALA DE PROFESORES TALLER DE ARQUITECTURA DE COMPUTADORES 1. REALIZAR EL PROCESO DE PAGINACION EN UNA ARQUITECTURA DE 32 BITS CON PAGINAS DE 32MEGAS DE ANCHO, DETERMINAR NUMERO DE PAGINAS Y DIRECCIONES DE INICIO Y FIN DE CADA PAGINA. 2. UN PROCESADOR MANEJA UNA ARQUITECTURA DE 32 BITS, SI SE DESEAN ARMAR PAGINAS DE 8MEGAS, ENTREGAR LOS SIGUIENTES DATOS: • DIRECCIONES DE INICIO Y FIN DE LA PRIMERA PAGINA, DIRECCIONES DE INICIO Y FIN DE LA PAGINA INTERMEDIA Y DIRECCIONES DE INICIO Y FIN DE LA PAGINA FINAL • DIRECCIONES DE INICIO Y FIN DE LAS PAGINAS 30, 63, 257, 513. 3. LA PAGINA 256 EN UNA ARQUITECTURA DE 16 BITS EMPIEZA EN LA DIRECCION 8000H Y TERMINA EN LA DIRECCION 83FF, CALCULAR: • NUMERO DE PAGINAS • DIRECCION DE INICIO Y FIN DE LAS PAGINAS: 400, 378, 7, 23. 4. UNA ARQUITECTURA DE 64 BITS MANEJA PAGINAS DE 8192 TERAS, CALCULAR LA SIGUIENTE INFORMACION: • NUMERO DE PAGINAS DE LA TABLA • DIRECCION DE INICIO Y FIN DE LA PAGINA DE INICIO, INTERMEDIA Y FINAL • DIRECCION DE INICIO Y FIN DE LAS PAGINAS 2000, 1030, 65, 513. PARA BAJAR ESTE TALLER VISITE: http://docs.google.com/Doc? docid=0AUrGoWIIGzlfZGRxdmg5OTJfMThjOXc0dzl4eg&hl=es