Bc0040

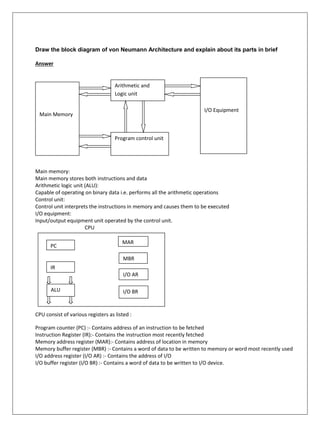

- 1. Draw the block diagram of von Neumann Architecture and explain about its parts in brief Answer Main memory: Main memory stores both instructions and data Arithmetic logic unit (ALU): Capable of operating on binary data i.e. performs all the arithmetic operations Control unit: Control unit interprets the instructions in memory and causes them to be executed I/O equipment: Input/output equipment unit operated by the control unit. CPU CPU consist of various registers as listed : Program counter (PC) :- Contains address of an instruction to be fetched Instruction Register (IR):- Contains the instruction most recently fetched Memory address register (MAR):- Contains address of location in memory Memory buffer register (MBR) :- Contains a word of data to be written to memory or word most recently used I/O address register (I/O AR) :- Contains the address of I/O I/O buffer register (I/O BR) :- Contains a word of data to be written to I/O device. Arithmetic and Logic unit Main Memory Program control unit I/O Equipment PC IR ALU MAR MBR I/O AR I/O BR

- 2. Draw the block diagram of Intel 8085 CPU organization and explain the different flag bits supported by the 8085 CPU Answer Internal CPU Bus Control Bus Address Bus Address/data bus The Different flag bits supported are as follows: 1) Z: zero flag , this bit is set when the result of ALU operation is zero , when Z=1(zero), Z=0(non zero) 2) S: Sign flag, set when the result of ALU operation is negative , when S=1(-ve result), S=0(non –ve) 3) P: Parity flag, set when the result of ALU operation results in even parity=1(even no of ones),P=0(Odd) 4) AC: Auxiliary carry flag, set when results in carry between 3th and 5th bit 5) CY: Carry flag, set when the results of ALU operation results in overflow, CY=1(overflow),CY=0(no overflow) Explain direct addressing mode and Register addressing Mode with example Answer Direct addressing mode: algorithm defined as EA = A , where EA= actual address of the location containing the reference operand. And A = contents of the address field in the instruction. In direct addressing mode address fiels contains address of operand e.g ADD A Add contents of cell A to accumulator. Look in the memory at address A for operand It gives single memory reference to access data Limited address space. B reg C reg D reg E reg H reg L reg Stack pointer Program counter Accumulator Temp reg Flags ALU Instruction register Control Unit Address buffer Address/ data buffer

- 3. Register Addressing mode: Algorithm defined as EA = R In register addressing mode operand is held in register named in address field. It has limited number of registers also it needs very small address fiels Shorter instructions due to this instruction fetch is faster Register addressing mode has no memory access and also have very limited address space It requires a good assembly programming e.g register int a; What is memory interleaving? Explain it with necessary figures. Answer Memory interleaving divides the system into a number of modules and arranges them so that successive words in the address space are placed in different modules. therefore if memory access request are made for consecutive addresses , then the access will be made for different modules . Address lines Data lines 4 words wide As from the figure main memory is divided into 4 different modules. When an instruction FETCH is issued by processor, a memory access circuit creates four consecutive addresses and places them in four MARs. A memory read command reads all the four modules simultaneously and retrieves four instructions. These are sent to processor. Thus each FETCH instruction fetches 4 consecutive instructions. M1 M2 M3 M4 MA MD MA MD MA MD MA MD MEMORY SWITCHING SYSTEM 4 INSTRUTION BUFFERS IN THE PROCESSOR

- 4. Write down the characteristics of RISC and CISC. Answer Characteristics of CISC: 1) CISC termed as Complex instruction set computers 2) Consist of large number of instructions from 100 to 250 instructions 3) It consist of large variety of addressing modes typically from 5 to 20 different modes 4) It consist of variable length instruction formats 5) Instructions that manipulate, operands in memory. 6) Provides backward compatibility with other processor in their family. Characteristics of RISC: 1) RISC stands for reduced instruction set computers. 2) It consist of few instructions 3) Consist of relatively few addressing modes 4) Memory access is limited to load and store instructions 5) All operations are done within the registers of CPU 6) Single cycle instruction execution 7) Hard wired rather than micro-programmed control 8) Control units are less complex and easier to design. Explain the basic structure of Linear pipeline Processor Answer Structure of Linear Pipeline processor: Output Pipelining is an implementation technique whereby multiple instructions are overlapped in execution. Pipelining is the key implantation technique used to make fast CPUs. To achieve pipelining , one must subdivide the input task (process) into a sequence of subtasks , each of which can be executed by a specialized hardware stage that operates concurrently with other stage in the pipeline. As from above figure : the pipeline consist of a cascade of processing stages . the stages are pure combinational circuits performing arithmetic or logical operations over the data stream flowing through the pipe. The stages are separated high speed interface latches separate the stages. The latches are fast registers for holding the intermediate results between the stages. Information that flows between adjacent stages are under the control of a common clock applied to all the latches simultaneously. S1 S2 Sk

- 5. Draw the I/O module of computer system and explain its functions Answer System Bus interface External device interface Data Data Lines Status Control Address Data lines Data Status Lines Control It is an entity within a computer that is responsible for the control of one or more external devices and exchange of data between those devices and main memory or CPU.I/O module may control more than one external device. We usually refer to each of the interface of the external device as a port. I/O modules also sends interrupt signal to the CPU. Following are the sequence of operation: CPU checks I/O module device status I/O module returns device status If ready , CPU requests data transfer I/O module gets data from device I/O module transfers data to CPU Data register Status/control register Input/Output Logic External Device interface logic External Device interface logic

- 6. Explain the characteristics of vector processing Answer Vector processor executes vector instructions on arrays of data. Here each instruction involves a string of repeated operations. Characteristics of vector processing are as follows: 1) Each element in a vector is a scalar quantity, which may be floating point , integer, logical value or a character. 2) Register based vector instructions appear in most of the register-to-register vector processor 3) Memory based vector operations are found in memory to memory vector processors. 4) A Boolean vector can be generated as a result of comparing two vectors and can be used for masking vector for enabling or disabling component operations in vector instructions. 5) A merge instruction combines two vectors under the control of a masking vector. 6) Vector operation performs same operations on different data sets repeatedly 7) A vector processor performs better with longer vectors. Explain how pipelining improve the performance of a computer? Answer Pipelining is an implementation technique whereby multiple instructions overlapped in execution. To achieve pipelining, one must subdivide the input task into a sequence of subtasks, each of which can be executed by a specialized hardware stage that operates concurrently with other stages in the pipeline. Pipelining is the key implementation technique used to make fast CPUs. In computer pipeline, each step in the pipeline completes a part of an instruction. Each of these steps is called pipe stages. The stages are connected one to the next to form a pipe –instructions enter at one end, progress through the stages and exit at the other end. Throughput of an instruction pipeline is determined by how often an instruction exits the pipeline. The time required between moving an instruction one step down the pipeline is a machine cycles as all the stages proceed at the same time, the length of machine cycle is determined by the time required for the slowest pipe stage and the longest step would determine the time between advancing the line. Thus pipelining yields a reduction in the average execution time per instruction, reduction can be viewed as decreasing the number of clock cycles per instructions

- 7. Draw the block diagram of DMA controller and explain it briefly. Answer A DMA controller is a device, usually peripheral to a computer CPU that is programmed to perform a sequence of data transfer on behalf of the CPU. A DMA controller can directly access memory and is used to transfer data from one memory location to another or from an I/O device to memory and vice-versa. A DMA controller manages several DMA channels, each of which can be programmed to perform a sequence of these DMA transfers. A DMA request signal for each channel is routed to the DMA controller. This signal is monitored and responded in same way as the processor handles the interrupts. When DMA controller sees DMA requests, the DMA controller responds by performing one or many data transfers that I/O device into system memory or vice-versa. Channel must be enabled by the processor for the DMA controller to respond to DMA requests. The number of transfer performed, transfer modes used and memory location accessed depends on how the DMA channel is programmed. A DMA controller shares the system memory and I/O bus with the CPU and has both bus master and slave capability. In master mode DMA controller acquires the system bus from the CPU to perform DMA transfers. In slave mode DMA controller is accessed by the CPU, which programs the DMA controllers’ internal registers to set up DMA transfers. Internal registers consist of source and destination address registers and transfer count registers for each DMA channel, as well as control and status registers for initiating, monitoring and sustaining the operation of the DMA controller. DMA Controller Bus request Bus grant DACKX DRQX TC PC BUS CPU Status register Mask register DMA Channel Base count Current count Base address Current address DMA arbitration logic