Vlsi Projects titles 2018 19

•

1 recomendación•512 vistas

Live Projects,B.Tech Projects,M.Tech Projects,BE Projects,ME Projects,EEE Projects,CSE Projects,ECE Projects,Diploma Projects,polytechnic Projects,Hardware kits,school projects,Sciencefare projects,Java projects,dotnet projects,embedded projects,real time projects,power system projects,power electronic projects,matlab projects,vlsi projects,image processing projects,signal processing projects,project reports,academic projects,technofest projects,Robotics projects,IOT Projects,Mechaical Projects,embedded c language,c language,Java course,Embedded Systems projects,computer training institute,computer courses,Nellore,Document support for projects,Project Report works,Plagiarism reports,Plagiarism works.

Denunciar

Compartir

Denunciar

Compartir

Descargar para leer sin conexión

Recomendados

DOTNET/JAVA/MATLAB/VLSI/NS2/EMBEDDED IEEE 2014 PROJECTS FOR ME/BE/B.TECH STUDENTS. FINAL YEAR 2014 PROJECTS FOR CSE/IT/ECE/EEE/ STUDENTS IN CHENNAI (S3 INFOTECH : 09884848198).

Final year IEEE 2014 projects for BE, BTech, ME, MTech &PHD Students (09884848198 : S3 Infotech)

Dear Students,

Greetings from S3 INFOTECH (0988 48 48 198). We are doing Final year (IEEE & APPLICATION) projects in DOTNET, JAVA, MATLAB, ANDROID, VLSI, NS2, EMBEDDED SYSTEMS and POWER ELECTRONICS.

For B.E, M.E, B.Tech, M.Tech, MCA, M.Sc, & PHD Students.

We implement your own IEEE concepts also in ALL Technologies. We are giving support for Journal Arrangement & Publication also.

Send your IEEE base paper to yes3info@gmail.com (or) info@s3computers.com.

To Register your project: www.s3computers.com

We are providing Projects in

• DOT NET

• JAVA / J2EE / J2ME

• EMBEDDED & POWER ELECTRONICS

• MATLAB

• NS2

• VLSI

• NETWORKING

• HADOOP / Bigdata

• Android

• PHP

Vlsi IEEE 2014 titles 2014_2015_CSE/IT/ECE/EEE/ STUDENTS IN CHENNAI (S3 INFO...

Vlsi IEEE 2014 titles 2014_2015_CSE/IT/ECE/EEE/ STUDENTS IN CHENNAI (S3 INFO...S3 Infotech IEEE Projects

Recomendados

DOTNET/JAVA/MATLAB/VLSI/NS2/EMBEDDED IEEE 2014 PROJECTS FOR ME/BE/B.TECH STUDENTS. FINAL YEAR 2014 PROJECTS FOR CSE/IT/ECE/EEE/ STUDENTS IN CHENNAI (S3 INFOTECH : 09884848198).

Final year IEEE 2014 projects for BE, BTech, ME, MTech &PHD Students (09884848198 : S3 Infotech)

Dear Students,

Greetings from S3 INFOTECH (0988 48 48 198). We are doing Final year (IEEE & APPLICATION) projects in DOTNET, JAVA, MATLAB, ANDROID, VLSI, NS2, EMBEDDED SYSTEMS and POWER ELECTRONICS.

For B.E, M.E, B.Tech, M.Tech, MCA, M.Sc, & PHD Students.

We implement your own IEEE concepts also in ALL Technologies. We are giving support for Journal Arrangement & Publication also.

Send your IEEE base paper to yes3info@gmail.com (or) info@s3computers.com.

To Register your project: www.s3computers.com

We are providing Projects in

• DOT NET

• JAVA / J2EE / J2ME

• EMBEDDED & POWER ELECTRONICS

• MATLAB

• NS2

• VLSI

• NETWORKING

• HADOOP / Bigdata

• Android

• PHP

Vlsi IEEE 2014 titles 2014_2015_CSE/IT/ECE/EEE/ STUDENTS IN CHENNAI (S3 INFO...

Vlsi IEEE 2014 titles 2014_2015_CSE/IT/ECE/EEE/ STUDENTS IN CHENNAI (S3 INFO...S3 Infotech IEEE Projects

Más contenido relacionado

La actualidad más candente

La actualidad más candente (15)

VLSI ieee projects 2017-2018 | VLSI ieee projects Titles 2017-2018

VLSI ieee projects 2017-2018 | VLSI ieee projects Titles 2017-2018

Design and implementation of Closed Loop Control of Three Phase Interleaved P...

Design and implementation of Closed Loop Control of Three Phase Interleaved P...

Design & implementation of high speed carry select adder

Design & implementation of high speed carry select adder

Design of Adjustable Reconfigurable Wireless Single Core CORDIC based Rake Re...

Design of Adjustable Reconfigurable Wireless Single Core CORDIC based Rake Re...

A 12-Bit High Speed Analog To Digital Convertor Using μp 8085

A 12-Bit High Speed Analog To Digital Convertor Using μp 8085

Design of high speed adders for efficient digital design blocks

Design of high speed adders for efficient digital design blocks

BULK IEEE PROJECTS IN VLSI ,BULK IEEE PROJECTS, IEEE 2015-16 VLSI PROJECTS IN...

BULK IEEE PROJECTS IN VLSI ,BULK IEEE PROJECTS, IEEE 2015-16 VLSI PROJECTS IN...

Similar a Vlsi Projects titles 2018 19

Similar a Vlsi Projects titles 2018 19 (20)

A LIGHT WEIGHT VLSI FRAME WORK FOR HIGHT CIPHER ON FPGA

A LIGHT WEIGHT VLSI FRAME WORK FOR HIGHT CIPHER ON FPGA

International Journal of Engineering Research and Development

International Journal of Engineering Research and Development

Pantech vlsi [xilinx ise & spartan fpga] 2016-17![Pantech vlsi [xilinx ise & spartan fpga] 2016-17](data:image/gif;base64,R0lGODlhAQABAIAAAAAAAP///yH5BAEAAAAALAAAAAABAAEAAAIBRAA7)

![Pantech vlsi [xilinx ise & spartan fpga] 2016-17](data:image/gif;base64,R0lGODlhAQABAIAAAAAAAP///yH5BAEAAAAALAAAAAABAAEAAAIBRAA7)

Pantech vlsi [xilinx ise & spartan fpga] 2016-17

Más de Green Corner Tech,Nellore

Greencornertech,Ieee 2015-16 Projects,Nellore,AndhraPradeshCSE Java ieee titles 2015-16,Live Projects,Green Corner Tech,Nellore,Andhra ...

CSE Java ieee titles 2015-16,Live Projects,Green Corner Tech,Nellore,Andhra ...Green Corner Tech,Nellore

Más de Green Corner Tech,Nellore (10)

cse projects,Dot net ieee projects 2015,green corner tech,nellore

cse projects,Dot net ieee projects 2015,green corner tech,nellore

CSE Java ieee titles 2015-16,Live Projects,Green Corner Tech,Nellore,Andhra ...

CSE Java ieee titles 2015-16,Live Projects,Green Corner Tech,Nellore,Andhra ...

Último

https://app.box.com/s/x7vf0j7xaxl2hlczxm3ny497y4yto33i80 ĐỀ THI THỬ TUYỂN SINH TIẾNG ANH VÀO 10 SỞ GD – ĐT THÀNH PHỐ HỒ CHÍ MINH NĂ...

80 ĐỀ THI THỬ TUYỂN SINH TIẾNG ANH VÀO 10 SỞ GD – ĐT THÀNH PHỐ HỒ CHÍ MINH NĂ...Nguyen Thanh Tu Collection

https://app.box.com/s/7hlvjxjalkrik7fb082xx3jk7xd7liz3TỔNG ÔN TẬP THI VÀO LỚP 10 MÔN TIẾNG ANH NĂM HỌC 2023 - 2024 CÓ ĐÁP ÁN (NGỮ Â...

TỔNG ÔN TẬP THI VÀO LỚP 10 MÔN TIẾNG ANH NĂM HỌC 2023 - 2024 CÓ ĐÁP ÁN (NGỮ Â...Nguyen Thanh Tu Collection

Último (20)

HMCS Max Bernays Pre-Deployment Brief (May 2024).pptx

HMCS Max Bernays Pre-Deployment Brief (May 2024).pptx

Food safety_Challenges food safety laboratories_.pdf

Food safety_Challenges food safety laboratories_.pdf

80 ĐỀ THI THỬ TUYỂN SINH TIẾNG ANH VÀO 10 SỞ GD – ĐT THÀNH PHỐ HỒ CHÍ MINH NĂ...

80 ĐỀ THI THỬ TUYỂN SINH TIẾNG ANH VÀO 10 SỞ GD – ĐT THÀNH PHỐ HỒ CHÍ MINH NĂ...

Sensory_Experience_and_Emotional_Resonance_in_Gabriel_Okaras_The_Piano_and_Th...

Sensory_Experience_and_Emotional_Resonance_in_Gabriel_Okaras_The_Piano_and_Th...

HMCS Vancouver Pre-Deployment Brief - May 2024 (Web Version).pptx

HMCS Vancouver Pre-Deployment Brief - May 2024 (Web Version).pptx

Interdisciplinary_Insights_Data_Collection_Methods.pptx

Interdisciplinary_Insights_Data_Collection_Methods.pptx

TỔNG ÔN TẬP THI VÀO LỚP 10 MÔN TIẾNG ANH NĂM HỌC 2023 - 2024 CÓ ĐÁP ÁN (NGỮ Â...

TỔNG ÔN TẬP THI VÀO LỚP 10 MÔN TIẾNG ANH NĂM HỌC 2023 - 2024 CÓ ĐÁP ÁN (NGỮ Â...

On National Teacher Day, meet the 2024-25 Kenan Fellows

On National Teacher Day, meet the 2024-25 Kenan Fellows

ICT role in 21st century education and it's challenges.

ICT role in 21st century education and it's challenges.

Plant propagation: Sexual and Asexual propapagation.pptx

Plant propagation: Sexual and Asexual propapagation.pptx

Exploring_the_Narrative_Style_of_Amitav_Ghoshs_Gun_Island.pptx

Exploring_the_Narrative_Style_of_Amitav_Ghoshs_Gun_Island.pptx

Vlsi Projects titles 2018 19

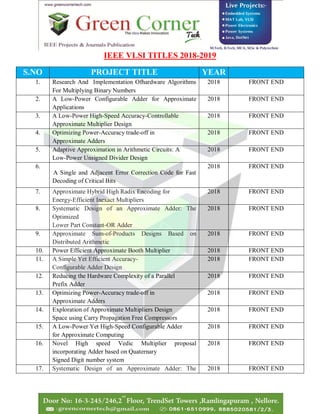

- 1. IEEE VLSI TITLES 2018-2019 S.NO PROJECT TITLE YEAR 1. Research And Implementation Ofhardware Algorithms For Multiplying Binary Numbers 2018 FRONT END 2. A Low-Power Configurable Adder for Approximate Applications 2018 FRONT END 3. A Low-Power High-Speed Accuracy-Controllable Approximate Multiplier Design 2018 FRONT END 4. Optimizing Power-Accuracy trade-off in Approximate Adders 2018 FRONT END 5. Adaptive Approximation in Arithmetic Circuits: A Low-Power Unsigned Divider Design 2018 FRONT END 6. A Single and Adjacent Error Correction Code for Fast Decoding of Critical Bits 2018 FRONT END 7. Approximate Hybrid High Radix Encoding for Energy-Efficient Inexact Multipliers 2018 FRONT END 8. Systematic Design of an Approximate Adder: The Optimized Lower Part Constant-OR Adder 2018 FRONT END 9. Approximate Sum-of-Products Designs Based on Distributed Arithmetic 2018 FRONT END 10. Power Efficient Approximate Booth Multiplier 2018 FRONT END 11. A Simple Yet Efficient Accuracy- Configurable Adder Design 2018 FRONT END 12. Reducing the Hardware Complexity of a Parallel Prefix Adder 2018 FRONT END 13. Optimizing Power-Accuracy trade-off in Approximate Adders 2018 FRONT END 14. Exploration of Approximate Multipliers Design Space using Carry Propagation Free Compressors 2018 FRONT END 15. A Low-Power Yet High-Speed Configurable Adder for Approximate Computing 2018 FRONT END 16. Novel High speed Vedic Multiplier proposal incorporating Adder based on Quaternary Signed Digit number system 2018 FRONT END 17. Systematic Design of an Approximate Adder: The 2018 FRONT END

- 2. Optimized Lower Part Constant-OR Adder 18. Towards Efficient Modular Adders based on Reversible Circuits 2018 FRONT END 19. Low Power and Low Noise Shift Register for In-Cell Touch Display Applications 2018 BACK END 20. Reducing the Hardware Complexity of a Parallel Prefix Adder 2018 BACK END 21. Low Power 4-Bit Arithmetic Logic Unit Using Full- Swing GDI Technique 2018 BACK END 22. A 7-nm Dual Port 8T SRAM with Duplicated InterPort Write Data to Mitigate Write Disturbance 2018 BACK END 23. Low Power 4×4 Bit Multiplier Design using Dadda Algorithm and Optimized Full Adder 2018 BACK END 24. Low-Power Area Efficient Reconfigurable Multiplier Architecture for FIR Filter 2018 BACK END 25. A Review on Various Divider Circuit Designs in VLSI 2018 BACK END 26. A High Performance Gated Voltage Level Translator with Integrated Multiplexer 2018 BACK END 27. A 0.6V Retention VMIN Ultra-Low Leakage High Density 6T SRAM in 40nm CMOS Technology using Adaptive Source Bias 2018 BACK END 28. Novel High speed Vedic Multiplier proposal incorporating Adder based on Quaternary Signed Digit number system 2018 BACK END 29. Low Power and Low Noise Shift Register for In-Cell Touch Display Applications 2018 BACK END 30. Reducing the Hardware Complexity of a Parallel Prefix Adder 2018 BACK END 31. A 4096-Point Radix-4 Memory-Based FFT Using DSP Slices 2017 FRONT END 32. An Improved DCM-Based Tunable True Random Number Generator for Xilinx FPGA 2017 FRONT END 33. Design of Power and Area Efficient Approximate Multipliers 2017 FRONT END 34. High-Speed Parallel LFSR Architectures Based on Improved State-Space Transformations 2017 FRONT END

- 3. 35. Improved 64-bit Radix-16 Booth Multiplier Based on Partial Product Array Height Reduction 2017 FRONT END 36. Overloaded CDMA Crossbar for Network-On-Chip 2017 FRONT END 37. Probability-Driven Multibit Flip-Flop Integration With Clock Gating 2017 FRONT END 38. RoBA Multiplier: A Rounding-Based Approximate Multiplier for High-Speed yet Energy-Efficient Digital Signal Processing 2017 FRONT END 39. A Method to Design Single Error Correction Codes With Fast Decoding for a Subset of Critical Bits 2016 FRONT END 40. A Mixed-Decimation MDF Architecture for Radix-2k Parallel FFT 2016 FRONT END 41. High-Speed and Energy-Efficient Carry Skip Adder Operating Under a Wide Range of Supply Voltage Levels 2016 FRONT END 42. High performance pipelined Architecture of elliptic curve scaller multiplication over GF(2m) 2016 FRONT END 43. Digital multiplierless realization of two coupled biological hindmarsh-Rose Neuron model 2016 FRONT END 44. Multiple constant multiplication algorithm for high speed and low power design 2016 FRONT END 45. VLSI Design for Convolutive Blind Source Separation 2016 FRONT END 46. Aging-Aware Reliable Multiplier Design With Adaptive Hold Logic 2015 FRONT END 47. In-Field Test for Permanent Faults in FIFO Buffers of NoC Routers 2015 FRONT END 48. On-Chip Codeword Generation to Cope With Crosstalk 2014 FRONT END 49. 4-2 Compressor Design with New XOR-XNOR Module[Back End] 2014 BACK END 50. Z-TCAM: An SRAM-based Architecture for TCAM 2014 FRONT END 51. High Throughput Architecture for the Advanced Encryption Standard Algorithm 2014 FRONT END 52. An Optimized Modified Booth Recoder for Efficient Design of the Add-Multiply Operator 2014 FRONT END 53. Design and estimation of delay, power and area for Parallel prefix Adders 2014 FRONT END 54. Area–Delay–Power Efficient Carry-Select Adder 2014 FRONT END 55. Design of High Performance 64 bit MAC Unit 2014 FRONT END

- 4. 56. Low voltage dual mode logic: Model analysis and parameter extraction 2013 FRONT END 57. A High Speed Low Power CAM With a Parity Bit and Power-Gated ML Sensing 2013 FRONT END 58. Design and Implementation of an On-Chip Permutation Network for Multiprocessor System-On-Chip 2013 FRONT END 59. Low-Power Dual Dynamic Node Pulsed Hybrid Flip- Flop Featuring Efficient Embedded Logic 2013 FRONT END 60. Least Complex S-Box and Its Fault Detection for Robust Advanced Encryption Standard Algorithm 2013 FRONT END 61. Novel method of digital clock frequency multiplication and division using floating point arithmetic 2013 FRONT END 62. A High Speed Binary Floating Point Multiplier Using Dadda Algorithm 2013 FRONT END 63. An FPGA Based High Speed IEEE-754 Double Precision Floating Point Multiplier U sing Verilog 2013 FRONT END 64. Design and Implementation of 32 Bit Unsigned Multiplier Using CLAA and CSLA 2013 FRONT END 65. VLSI Implementation of a High Speed Single Precision Floating Point Unit Using Verilog 2013 FRONT END 66. VLSI Implementation of a Low-Cost High-Quality Image Scaling Processor 2013 FRONT END 67. RTL Design and VLSI Implementation of an efficient Convolutional Encoder and Adaptive Viterbi Decoder 2013 FRONT END 68. Design of Low Logical Cost Conservative Reversible Adders using Novel PCTG 2013 FRONT END 69. Reliable and Higher Throughput Anti-Collision Technique for RFID UHF Tag 2012 FRONT END 70. Accumulator Based 3-Weight Pattern Generation 2012 FRONT END 71. Design and Characterization of Parallel Prefix Adders using FPGAs 2011 FRONT END 72. Self-Immunity Technique to Improve Register File Integrity against Soft Errors 2011 FRONT END 73. High Throughput DA-Based DCT With High Accuracy Error-Compensated Adder Tree 2011 FRONT END 74. High Speed ASIC Design of Complex Multiplier Using Vedic Mathematics 2011 FRONT END 75. Low-Power and Area-Efficient Carry Select Adder 2011 FRONT END

- 5. 76. Vlsi Architecture Of Parallel Multiplier–Accumulator Based On Radix-2 Modified Booth Algorithm 2011 FRONT END 77. Design and Characterization of Parallel Prefix Adders using FPGAs IEEE FRONT END 78. Implementation of a Self-Motivated Arbitration Scheme for the Multi-Layer AHB Bus matrix IEEE FRONT END 79. An Efficient Architecture for 3-D Discrete Wavelet Transform IEEE FRONT END 80. High Speed VLSI Architecture for General Linear Feedback Shift Register (LFSR) Structures IEEE FRONT END 81. Self-Immunity Technique to Improve Register File Integrity against Soft Errors IEEE FRONT END