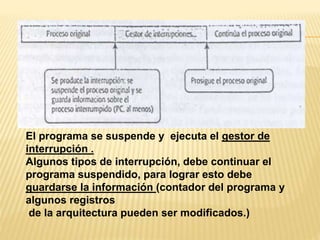

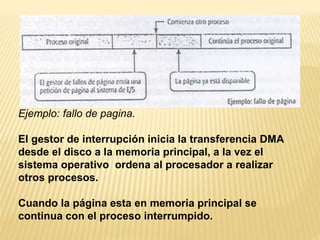

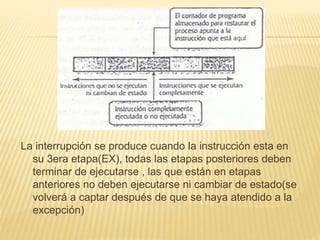

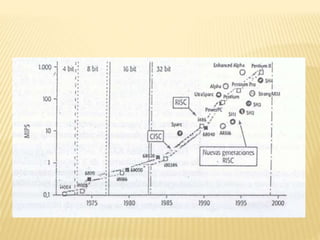

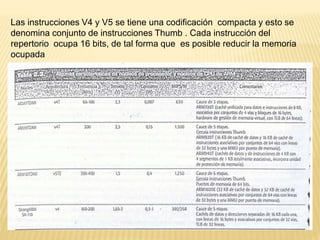

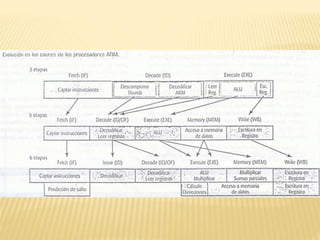

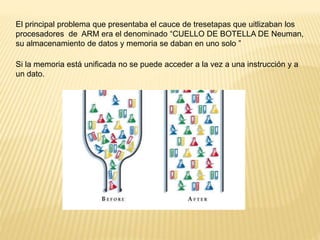

El documento aborda el procesamiento de interrupciones en procesadores segmentados, señalando su impacto negativo en el rendimiento debido a la interrupción del flujo de instrucciones. Describe la taxonomía de las interrupciones, diferenciando entre aquellas generadas por el propio procesador y las externas, así como los mecanismos para asegurar la continuidad en la ejecución de programas. Además, se discute la evolución de procesadores ARM y las mejoras en sus arquitecturas, enfocándose en la transición de diseños de 3 a 6 etapas para optimizar el rendimiento.