μP.pdf

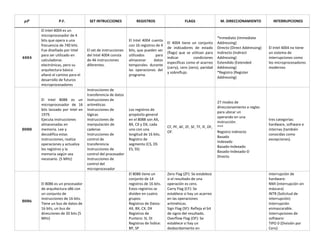

- 1. 𝝁𝑷 P.F. SET INTRUCCIONES REGISTROS FLAGS M. DIRECCIONAMIENTO INTERRUPCIONES 𝟒𝟎𝟎𝟒 El Intel 4004 es un microprocesador de 4 bits que opera a una frecuencia de 740 kHz. Fue diseñado por Intel para ser utilizado en calculadoras electrónicas, pero su arquitectura básica allanó el camino para el desarrollo de futuros microprocesadores El set de instrucciones del Intel 4004 consta de 46 instrucciones diferentes. El Intel 4004 cuenta con 16 registros de 4 bits, que pueden ser utilizados para almacenar datos temporales durante las operaciones del programa. El 4004 tiene un conjunto de indicadores de estado (flags) que se utilizan para indicar condiciones específicas como el acarreo (carry), cero (zero), paridad y sobreflujo. *Inmediato (Immediate Addressing) Directo (Direct Addressing) Indirecto (Indirect Addressing) Extendido (Extended Addressing) *Registro (Register Addressing) El Intel 4004 no tiene un sistema de interrupciones como los microprocesadores modernos 𝟖𝟎𝟖𝟖 El Intel 8088 es un microprocesador de 16 bits lanzado por Intel en 1979. Ejecuta instrucciones almacenadas en memoria. Lee y decodifica estas instrucciones, realiza operaciones y actualiza los registros y la memoria según sea necesario. (5 MHz) Instrucciones de transferencia de datos Instrucciones de aritméticas Instrucciones de lógicas Instrucciones de manipulación de cadenas Instrucciones de control de transferencia Instrucciones de control del procesador Instrucciones de control del microprocesador Los registros de propósito general en el 8088 son AX, BX, CX y DX, cada uno con una longitud de 16 bits. Registro de segmento (CS, DS ES, SS) CF, PF, AF, ZF, SF, TF, IF, DF, OF. 27 modos de direccionamiento o reglas para ubicar un operando en una instrucción. *** Registro indirecto Basado Indexado Basado-Indexado Basado-Indexado-D Directo tres categorías: hardware, software e internas (también conocidas como excepciones). 𝟖𝟎𝟖𝟔 El 8086 es un procesador de arquitectura x86 con un conjunto de instrucciones de 16 bits. Tiene un bus de datos de 16 bits, un bus de direcciones de 20 bits (5 MHz) El 8086 tiene un conjunto de 14 registros de 16 bits. Estos registros se dividen en cuatro grupos: Registros de Datos: AX, BX, CX, DX Registros de Puntero: SI, DI Registros de Índice: BP, SP Zero Flag (ZF): Se establece si el resultado de una operación es cero. Carry Flag (CF): Se establece si hay un acarreo en las operaciones aritméticas. Sign Flag (SF): Refleja el bit de signo del resultado. Overflow Flag (OF): Se establece si hay un desbordamiento en interrupción de hardware: NMI (interrupción sin máscara) INTR (Solicitud de interrupción) Interrupción enmascarable. interrupciones de software: TIPO 0 (División por Cero)

- 2. Registros de Segmento: CS, DS, ES, SS Registro de Puntero de Instrucción: IP (Puntero de Instrucción) Registro de Flags: Flags (Indicadores de Estado) operaciones aritméticas con signo. TIPO 1 (Ejecución en un Solo Paso para Depurar un Programa) TIPO 2 (NMI - Condición de Falla de Energía) TIPO 3 (Interrupción de Punto de Interrupción) TIPO 4 (Interrupción por Desbordamiento) 𝟖𝟎𝑪𝟏𝟖𝟕 El Coprocesador Matemático 80C187 proporciona instrucciones aritméticas para una gran variedad de tipos de datos numéricos. Ejecuta numerosas funciones trascendentales incorporadas (por ejemplo, tangente, seno, coseno y funciones logarítmicas). El 80C187 amplía efectivamente el conjunto de registros e instrucciones de la CPU 80C186 para los tipos de datos existentes y añade también varios tipos de datos nuevos. Registros de Datos (D0-D7): Utilizados para almacenar datos. Registros de Índice (X, Y): Utilizados para operaciones de indexación en direccionamiento indirecto. Registro de Puntero de Pila (SP): Utilizado para gestionar la pila en operaciones de llamada y retorno de subrutinas. Zero Flag (Z): Indica si el resultado de una operación es cero. Carry Flag (C): Indica si hubo un acarreo en operaciones aritméticas. Sign Flag (S): Indica el signo del resultado de una operación. Overflow Flag (V): Indica si se produjo un desbordamiento en operaciones aritméticas. El microprocesador 80C187 admite un sistema de interrupciones que permite a dispositivos externos interrumpir la secuencia normal de ejecución del programa. Esto es útil para gestionar eventos en tiempo real y mejorar la eficiencia del sistema. 𝒁𝟖𝟎 El microprocesador Z80 es un microprocesador de 8 bits diseñado por Zilog. 40 pines 2.5 – 8MHz 158 instrucciones. Manipulación de bits Carga e intercambio Aritmética y lógica Rotación y desplazamiento Transferencia y búsqueda de bloques Salto, llamda y retorno Entrada y salida Control de la CPU Registros de Datos (D): D, E, H, L. Registros de Propósito General (B, C, D, E, H, L): Pueden ser combinados como pares para formar registros de 16 bits (BC, DE, HL). Registros de 16 bits: SP (Stack Pointer), PC (Program Counter). D. inmediato, idexado, inmediato indexado, de registro, implícito, relativo, indirecto de registro, extendido y por bits. I. Enmascarables IM1 Y IM2 I. No Enmascarables RST7.5 NMI

- 3. 𝟖𝟎𝟐𝟖𝟔 Un 80286 con una frecuencia de 12 MHz ofrece un rendimiento seis veces o incluso superior al del 8086 estándar con 5 MHz. Transferencia de Datos, Operaciones Aritméticas, Operaciones Lógicas, Comparación y Salto Condicional, Manipulación de Pila, Manipulación de Segmentos, Control de Proceso, Registros generales, registros de segmento, registros base e índice, registro de status y control B. de acarreo (CF) B. de Paridad (PF) B. de cero (ZF) B. de signo (SF) B. de overflow (OF) B. de paso a paso (TF) B. de habilitación de interrupción (IF) B. de dirección (AF) M. Directo M. Indirecto de registro M. Relativo a base M. Indexado M. Indexado Relativo Base M. Indexado Relativo a base con desplazamiento INTERRUPCIONES DE HARDWARE: INTn, NMI, INTn, INT3, INTO, INT8, INT9. 𝟖𝟎𝟑𝟖𝟔 Es un procesador de 32 bits. Su arquitectura se basa en el conjunto de instrucciones x86 y consta de tres componentes principales: la Unidad de Ejecución (EU), la Unidad de Control (CU) y la Memoria Caché. 132 PINES 16-20-25-33MHz Tiene un conjunto de instrucciones extenso y complejo que incluye operaciones aritméticas, lógicas, de control de flujo y manipulación de datos. Soporta instrucciones de 32 bits, lo que lo distingue de sus predecesores de 16 bits. Registros de control: PG, ET, TS, EM, MP, PE. Registros de depuración y prueba: BT, BS, BD, LEN, RW, GD, GE, LE. Bits del TR6 y TR7: V, D, U, W, C, PL, REP. El 80386 utiliza un conjunto de flags (indicadores) en el registro EFLAGS para indicar condiciones y resultados de operaciones. Estos flags incluyen el Carry Flag, Zero Flag, Sign Flag, Overflow Flag, entre otros. El procesador 80386 admite varios modos de direccionamiento, como direccionamiento inmediato, directo, indirecto, base-indexado y de registro. El 80386 es capaz de manejar interrupciones mediante un sistema de vectores de interrupción. Puede manejar interrupciones de hardware y software, proporcionando una forma de cambiar de manera controlada de la ejecución normal del programa a un servicio específico. 𝟖𝟎𝟒𝟖𝟔 Microprocesador de 32 bits, utiliza una arquitectura de conjunto de instrucciones complejas (CISC) y opera internamente a velocidades de reloj 25- 33-50-66-100MHz. La arquitectura del 80486 consta de unidades de ejecución, registro y control. Incluye operaciones aritméticas, lógicas, de control de flujo y de manejo de datos. También introduce instrucciones SIMD (Single Instruction, Multiple Data) para mejorar el rendimiento en operaciones de datos simultáneas. El 80486 tiene 32 registros de uso general de 32 bits cada uno. Estos registros incluyen EAX, EBX, ECX, EDX, ESI, EDI, EBP y ESP, entre otros. Los registros de segmento, como CS, DS, SS y ES, se utilizan para el manejo de la memoria. El 80486 tiene un conjunto de indicadores de flags que reflejan el estado de las operaciones realizadas. Estos incluyen flags como zero flag (ZF), carry flag (CF), overflow flag (OF), entre otros, que son esenciales para la lógica de control de flujo. El 80486 admite varios modos de direccionamiento, como direccionamiento inmediato, directo, indirecto, base-indexado y registro-registro. Estos modos ofrecen flexibilidad en la manipulación de datos y direcciones de memoria. El procesador 80486 admite interrupciones, que pueden ser generadas internamente o externamente. Utiliza un controlador de interrupciones avanzado para gestionar estas interrupciones, permitiendo el manejo eficiente de eventos externos y la ejecución de rutinas específicas. 𝑷𝑬𝑵𝑻𝑰𝑼𝑴𝟏