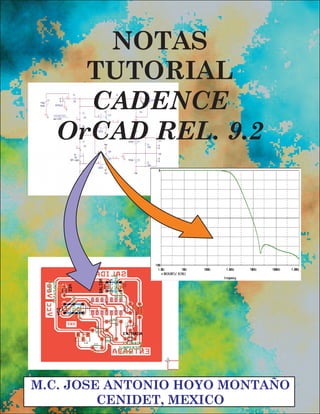

Este documento proporciona una guía de usuario para el software de diseño electrónico Cadence OrCAD rel. 9.2. Incluye instrucciones para la captura de esquemáticos, la creación de modelos, librerías y símbolos, y el uso de fuentes de señal. El documento contiene cuatro capítulos y cubre temas como la interfaz de usuario, el diseño de circuitos planos y jerárquicos, y la simulación de circuitos.

![cenidet

Para agregar nuevos modelos a librerías ya existentes se sigue el siguiente procedimiento:

1) Ejecutar el comando “OPEN” del menú “FILE”, o presionar “CTRL O”, o el botón “OPEN LIBRARY”.

2) Repetir los pasos b y c descritos anteriormente.

MODIFICAR UN MODELO EXISTENTE EN CAPTURE

MODELADO DE DISPOSITIVOS

Los modelos de los dispositivos son la forma que tiene PSPICE de recabar características de operación de un

circuito o de un dispositivo. Los elementos activos, tales como diodos y transistores, hacen necesario el recabar varios

parámetros que describan su comportamiento, y también el referirse a esos parámetros por un nombre corto. A

continuación veremos como modificar los parámetros de diodos, transistores bipolares, transistores de efecto de campo, y

transistores bipolares de compuerta aislada.

EL COMANDO.MODEL

El comando .MODEL fija un cierto número de parámetros de referencia para los dispositivos en PSPICE. No

todos los dispositivos necesitan un modelo; por ejemplo, las resistencias que no son referidas a un modelo, se supone tienen

un valor de resistencia constante para todas las simulaciones. Cada dispositivo que se referencia a un modelo debe tener ese

modelo definido, lo cual significa que necesita un comando .MODEL que complete la descripción de como opera el

dispositivo. La sintaxis para este corriendo es:

.MODEL nombre [AKO: modelo de referencia] tipo ([nombre del parámetro = valor [tolerancia]... ] )

El “nombre” es una etiqueta de identificación o “nombre del dispositivo” con el cual quiere referirse al dispositivo.

Por lo general es el número de parte del fabricante, como por ejemplo “MJE3055" para un transistor, o un nombre

descriptivo, como ”FILM" para una resistencia de película de metal. Puede usar cualquier nombre que cumpla las

convenciones para nombres del simulador; los nombres deben empezar con una letra del alfabeto, y continuar con caracteres

alfabéticos o numéricos, o “ - ” y “$”. Por ejemplo, el transistor “2N3904" generalmente es modificado a ”Q2N3904" para

cumplir con las convenciones para nombres.

AKO (siglas en inglés de: A Kind Of, una clase de) seguido del nombre de un modelo de referencia, nos indica los

que los parámetros usados en el modelo serán iguales a los del modelo de referencia,

El “tipo” es una descripción del tipo de dispositivo, el cual puede ser uno de los siguientes dispositivos lineales:

CAP capacitor.

IND inductor.

RES resistor.

o uno de los siguientes dispositivos semiconductores:

D diodo

NPN transistor bipolar NPN

PNP transistor bipolar PNP

Cadence 52

OrCAD REL. 9.2 LITE](https://image.slidesharecdn.com/tutorial-orcad-9-2-120624191743-phpapp02/85/Tutorial-or-cad-9-2-61-320.jpg)

![cenidet

función lineal, pero puede aproximarse así para polarizaciones mucho mayores a la barrera de potencial (F ) de la unión. El

error asociado con el uso de la ley cuadrática es algo pequeño (cuando se compara al análisis exacto así como a dispositivos

reales). El resultado de la ley cuadrática se aplica solo cuando VDS es mayor que VGS - Vumbral (donde Vumbral es

equivalente al voltaje de “agotamiento” del JFET, y es fijado por el parámetro VTO), cuando el canal del FET es saturado.

Cuando VDS está por debajo del Vumbral, la expresión que relaciona la corriente de dren con el voltaje de la unión de

compuerta es

I dren = b × ( × 2 ( V-

GS × ) )

Vumbral - VDS VDS

2

la cual describe una curva parabólica invertida pasando por el origen y la cual, en su valor pico (cuando VDS está en el

umbral), intersecta la formula de la ley cuadrática. Esta región parabólica de operación se llama región “lineal”; para

voltajes de dren pequeños, la expansión de la ecuación anterior es dominada por el termino lineal.

I dren = b × × 2 ( V- GS Vumbral VDS

× )

Finalmente, Idren es cero cuando VGS es menor que Vumbral. En la tabla VI se muestran algunos de los

parámetros más usados en la definición de modelos de JFET. El listado completo de los parámetros disponibles para definir

el modelo de un JFET se encuentran en el anexo B.

Tabla VI.- Parámetros comunes del modelado de JFET.

VALOR POR

PARAMETRO DESCRIPCION UNIDADES

OMISION

VTO Voltaje de umbral Voltios 0

BETA Coeficiente de transconductancia Amp/Volt2 1e-4

LAMBDA Modulación de longitud del canal Voltios-1 0

PARAMETROS DE MODELADO DE UN TRANSISTOR DE EFECTO DE CAMPO TIPO MOS

(MOSFET)

El MOSFET siendo una variante del JFET se rige básicamente por las mismas ecuaciones, sin embargo, por sus

diferencias de construcción en PSPICE se utilizan seis modelos diferentes, estos modelos difieren en la formulación de la

característica I-V. El parámetro “LEVEL” selecciona cual de los modelos se utilizará para la simulación. A continuación se

listan los tipos de modelos disponibles, para mayor información sobre los modelos puede revisar las referencias mostradas

[1], [2], [3], [7], [8] y [10] que aparecen en la página 174 del Manual de Referencia de PSPICE.

LEVEL= 1, Modelo Shichman-Hodges,

LEVEL= 2, Modelo analítico, basado en la geometría del MOSFET,

LEVEL=3, Modelo de canal corto, semi-empírico,

LEVEL=4, Modelo BSIM,

LEVEL=5, Modelo EKV versión 2.6,

LEVEL=6, Modelo BSIM3 versión 2.0,

LEVEL=7, Modelo BSIM3 versión 3.1

Cadence 56

OrCAD REL. 9.2 LITE](https://image.slidesharecdn.com/tutorial-orcad-9-2-120624191743-phpapp02/85/Tutorial-or-cad-9-2-65-320.jpg)

![cenidet

Fig. 151.- Símbolo de FILESTIMn y ventana de propiedades de FILESTIM4.

El archivo de definición de las señales digitales es el siguiente:

* ENCABEZADO, contiene el nombre de las señales

nombre1, nombre2 ....

* Inicio de la definición de transiciones. (NOTE QUE EXISTE UNA LINEA EN BLANCO)

tiempo valor digital

Por ejemplo:

Clock, reset, in1, in2 ; nombres de cuatro señales

0 0000 ; valores en base binaria

10ns 1100

20ns 0101

30ns 1110

40ns 0111

El encabezado tiene el siguiente formato:

[TIMESCALE=valor]

nombre1 ... nombren

OCT(nombre(bit3) ... nombre(bit lsb))...

HEX(nombre(bit4) ... nombre(bit lsb))..

Cadence 102

OrCAD REL. 9.2 LITE](https://image.slidesharecdn.com/tutorial-orcad-9-2-120624191743-phpapp02/85/Tutorial-or-cad-9-2-111-320.jpg)

![cenidet

nombre_del_parámetro = valor_central [dev = tolerancia] [lot = tolerancia]

El valor central (normalizado) se obtiene del promedio de los valores mínimo y máximo del parámetro, por

ejemplo, se tiene una resistencia cuyos valores de tolerancia van de +25% a –15%, el valor central de la resistencia se

obtiene de:

R = (1.25 + 0.85)/2 = 1.05

El valor de tolerancia para el análisis estadístico se obtiene de cualquiera de las siguientes expresiones:

Máximo = valor_central * (1 + tolerancia), o Mínimo = valor_central * (1 – tolerancia)

Para el ejemplo anterior, el valor de tolerancia se puede obtener de:

1.25 = 1.05 * (1 + tolerancia),

y el valor de tolerancia es de 19.04%.

De manera que en el modelo de la resistencia debe aparecer:

.model Nombre_modelo RES (R=1.05 [DEV=19.04%] [LOT=19.04%])

Hay que recordar que los parámetros que aparecen entre corchetes son opcionales, sin embargo, para el análisis de

Monte Carlo y Peor de los Casos debe aparecer al menos uno de los dos.

ANALISIS DE MONTE CARLO

El análisis de Monte Carlo se utiliza para calcular la respuesta de un circuito ante cambios aleatorios en los valores

de sus componentes o de alguno de los parámetros de los dispositivos dentro de un rango de tolerancia especificado. Este

análisis proporciona información estadística del impacto de la variación de un parámetro de un dispositivo. En el análisis de

Monte Carlo se definen tolerancias de ciertos parámetros de los dispositivos y el análisis principal (transitorio, barrido de

CD o barrido de CA) se realiza en varias corridas usando estas tolerancias.

ANALISIS TRANSITORIO

Al diseñar circuitos digitales o de conmutación, una de las preocupaciones principales es la variación de los

tiempos de subida y bajada de las señales debida a la tolerancia de los dispositivos que componen el circuito. Para

ejemplificar este caso, utilizaremos el circuito inversor implementado con un BJT que se muestra en la figura 282, el cual

guardaremos en el proyecto “ejemplo14”. Las resistencias utilizadas tienen una tolerancia de 5%, el transistor varía su Hfe

desde 50 hasta 350.

El modelo de las resistencias Rb y Rc, y del transistor deben cambiarse por el siguiente:

.model Rgauss RES(R=1 dev/gauss 5%)

.model Q2N3904 NPN(Is=6.734f Xti=3 Eg=1.11 Vaf=74.03

+ Bf=200 dev/uniform 150

+ Ne=1.259 Ise=6.734f Ikf=66.78m Xtb=1.5 Br=.7371 Nc=2 Isc=0 Ikr=0 Rc=1

+ Cjc=3.638p Mjc=.3085 Vjc=.75 Fc=.5 Cje=4.493p Mje=.2593 Vje=.75

+ Tr=239.5n Tf=301.2p Itf=.4 Vtf=4 Xtf=2 Rb=10)

* National pid=23 case=TO92

* 88-09-08 bam creation

Cadence 183

OrCAD REL. 9.2 LITE](https://image.slidesharecdn.com/tutorial-orcad-9-2-120624191743-phpapp02/85/Tutorial-or-cad-9-2-192-320.jpg)

![cenidet

DEFINICION DE FUNCIONES MACROS

Una función MACRO es una expresión que define un trazo. Esta expresión tiene un nombre y argumentos, los

cuales pueden ser transferidos a la expresión del trazo. Los MACROS se guardan en los archivos PRB y pueden ser

utilizados varias veces en el diseño donde fueron definidos y en otros diseños.

Las MACROS pueden contener constantes, funciones, expresiones o combinaciones de las anteriores. Las

funciones MACROS pueden hacer referencia a otras funciones MACROS, sin embargo, no se permiten definiciones

recursivas. El formato general de una función MACRO es el siguiente:

Nombre de MACRO[(argumento[,argumento])] = <definición>

La ventana de edición de MACROS, figura 381, permite la creación, modificación, eliminación y transferencia de

MACROS entre archivos PRB. A continuación se describe cada una de estas opciones.

Fig. 381.- Ventana de edición de MACROS.

CREACION DE MACROS

Para ejemplificar el proceso de creación de MACROS utilizaremos el archivo binario de salida producido por el

“ejemplo06”, circuito rectificador de onda completa monofásico. En PSPICE AD se abre el archivo binario de salida. Antes

de desplegar alguna señal crearemos las siguientes MACROS:

Vin=V(in1,in2),

Iin=-I(V1)

Pin=agv(Vin*Iin)

En el campo “DEFINITION” se escribe la definición de la MACRO, al terminar la definición de cada una de las

MACROS debe presionarse el botón “SAVE” para que la macro se agregue a la lista de definiciones disponibles, figura

382. Para verificar que las definiciones se han creado de manera correcta, agregaremos dos trazos al área de desplegado: Pin

y AVG(-W(V1)), si la definición de las MACRO es correcta, ambos trazos deben coincidir, figura 383. Para cerrar la

ventana de edición de MACROS debe presionarse el botón “CLOSE”.

Cadence 243

OrCAD REL. 9.2 LITE](https://image.slidesharecdn.com/tutorial-orcad-9-2-120624191743-phpapp02/85/Tutorial-or-cad-9-2-252-320.jpg)

![cenidet

(d)

Fig. 414.- Venana de propiedades de trazo.

Al terminar de cambiar estos atributos debe presionarse el botón “OK” para que los cambios tomen efecto. Si los

cambios no se visualizan inmediatamente, ejecute el comando “REDRAW” del menú “VIEW”.

Para modificar los colores de fondo y cuadrícula desplegados en PSPICE AD es necesario modificar el archivo

“PSPICE.INI” que se encuentra en la carpeta ”c:..OrcadLitePspice”. Este archivo puede ser abierto con el Bloque de

Notas o NOTEPAD. En la sección [Probe Display Colors] se puede modificar los colores asignados al fondo, cuadrícula y

trazos. El formato utilizado para la asignación de colores es:

<Nombre_propiedad> = <color>

Los nombres de propiedad validos en esta sección del archivo son: “BACKGROUND” (fondo),

“FOREGROUND” (usado para la cuadrícula) y TRACE_1 a TRACE_12 (trazos del 1 al 12). Los colores pueden ser

asignados por medio de nombres de color válidos o especificando una combinación de colores R (rojo), G (verde), B (azul)

en los rangos de 0 a 255 para cada color.

Los nombres válidos para colores son: BLACK (negro), BLUE (azul), GREEN (verde), CYAN (azul – verde),

RED (rojo), MAGENTA (magenta), YELLOW (amarillo), BRIGTHWHITE (blanco brillante), BROWN (café),

LIGHTGRAY (gris claro), DARKGRAY (gris oscuro), DARKBLUE (azul oscuro), DARKGREEN (verde oscuro),

DARKCYAN (azul – verde oscuro), DARKRED (rojo oscuro) y DARKMAGENTA (magenta oscuro), entre otros.

Después de realizar las modificaciones es necesario guardar los cambios en el archivo. La nueva asignación de

colores tomará efecto la siguiente vez que se ejecute el programa PSPCIE AD.

Cadence 266

OrCAD REL. 9.2 LITE](https://image.slidesharecdn.com/tutorial-orcad-9-2-120624191743-phpapp02/85/Tutorial-or-cad-9-2-275-320.jpg)

![cenidet

[PROBE DISPLAY COLORS]

NUMTRACECOLORS=12

BACKGROUND= 255 255 255

FOREGROUND=BLACK

TRACE_1=DARKGREEN

TRACE_2=BRIGHTRED

TRACE_3=BRIGHTBLUE

TRACE_4=BRIGHTYELLOW

TRACE_5=BRIGHTMAGENTA

TRACE_6=BRIGHTCYAN

TRACE_7=MUSTARD

TRACE_8=PINK

TRACE_9=LIGHTGREEN

TRACE_10=DARKPINK

TRACE_11=LIGHTBLUE

TRACE_12=PURPLE

select=BRIGHTRED

Fig. 415.- Ejemplo de la sección “PROBE DISPLAY COLORS”.

CONFIGURACION DE PSPICE AD

PSPICE AD permite configurar las barras de herramientas visibles, los comando contenidos en estas barras de

herramientas, secuencia de teclas para ejecutar comandos, características de desplegado de las áreas, modificación del

nombre asignado al desplegado de la simulación y el control o forma de desplegar los trazos en pantalla.

Para configurar las barras de herramientas y las secuencias de teclas asignadas a los comandos de PSPICE AD, se

utiliza el comando “CUSTOMIZE” del menú “TOOLS”, esto abre la ventana mostrada en la figura 416. Esta ventana

cuenta con tres secciones: “TOOLBARS”, “COMMANDS” y “KEYBOARD”.

La sección “TOOLBARS” permite seleccionar las barras de herramientas que estarán visibles en PSPICE AD,

definir las características de desplegado de estas barras, y definir esquemas de desplegado de estar barras de herramientas.

El campo “TOOLBARS” permite seleccionar cuales de las diez barras de herramientas se desplegarán, para seleccionar

una barra es necesario marcar el cuadro de selección que se encuentra a la izquierda de su nombre.

La opción “SHOW TOOLTIPS” permite que se despliegue un mensaje en la barra de estado de PSPICE con la

descripción del comando que ejecuta cada botón de las barras de herramientas cuando se posiciona el cursor sobre el botón.

La opción “COOL LOOK” permite que las barras de herramientas aparezcan como un conjunto de iconos continuos,

cuando esta opción está deseleccionada, los iconos en las barras de herramientas aparecen encerrados en cuadros. La opción

“LARGE BUTTONS” hace que los iconos de las barras de herramientas aparezcan de mayor tamaño.

Por último, la opción “SCHEME” permite definir el nombre con el cual se guardará en el disco duro la

configuración de desplegado de barra de herramientas, comandos y secuencia de teclas para ejecución de comandos.

Cadence 267

OrCAD REL. 9.2 LITE](https://image.slidesharecdn.com/tutorial-orcad-9-2-120624191743-phpapp02/85/Tutorial-or-cad-9-2-276-320.jpg)

![cenidet

Anexo C.- Comandos de descripción de modelos .MODEL y .SUBCKT

Sintaxis comando .MODEL

El comando .MODEL define el comportamiento de un dispositivo basado en un conjunto de parámetros que

pueden ser referenciados por otros dispositivos en el circuito.

La sintaxis del comando es la siguiente:

.MODEL <nombre del modelo> [AKO: <nombre del modelo de referencia>] <tipo de modelo>

+ ([<nombre del parámetro>=<valor del parámetro> [especificación de tolerancia]]

+ [T_MEASURED=<valor de temperatura>] [T_ABS=<valor de temperatura absoluta>] o

+ [T_REL_GLOBAL=<valor relativo a la temperatura actual>] o

+ [T_REL_LOCAL=<valor relativo al modelo AKO>])

Los campos encerrados en corchetes ( [] ) son opcionales.

<nombre del modelo> Nombre del modelo utilizado como referencia en el campo “IMPLEMENTATION” de los

símbolos gráficos.

[AKO: <nombre del modelo de referencia>] Permite utilizar los parámetros definidos en el modelo de referencia,

a menos que sean redefinidos en el modelo actual.

<Tipo de modelo> Define el tipo de dispositivo a modelar, a continuación se listan los tipos de modelos utilizados

por PSPICE.

TIPO DE MODELO EJEMPLO DE NOMBRE TIPO DE DISPOSITIVO

GASFET Bxxx GaAs MESFET DE CANAL N

CAP Cxxx CAPACITOR

D Dxxx DIODO

NJF Jxxx JFET DE CANAL N

PJF Jxxx JFET DE CANAL P

NUCLEO MAGNETICO NO LINEAL

CORE Kxxx

(TRANSFORMADOR)

IND Lxxx INDUCTOR

NMOS Mxxx MOSFET DE CANAL N

PMOS Mxxx MOSFET DE CANAL P

DISPOSITIVO DE ENTRADA DIGITAL

DINPUT Nxxx

(RECIVE SEÑAL DIGITAL)

DISPOSITIVO DE SALIDA DIGITAL

DOUTPUT Oxxx

(ENTREGA SEÑAL DIGITAL)

LPNP Qxxx BJT TIPO PNP LATERAL

Cadence 342

OrCAD REL. 9.2 LITE](https://image.slidesharecdn.com/tutorial-orcad-9-2-120624191743-phpapp02/85/Tutorial-or-cad-9-2-351-320.jpg)

![cenidet

TIPO DE MODELO EJEMPLO DE NOMBRE TIPO DE DISPOSITIVO

NPN Qxxx BJT TIPO NPN

PNP Qxxx BJT TIPO PNP

RES Rxxx RESISTENCIA

INTERRUPTOR CONTROLADO POR

VSWITCH Sxxx

VOLTAJE

LINEA DE TRANSMISION CON

TRN Txxx

PERDIDAS

UADC Uxxx ADC MULTIBIT

UDAC Uxxx DAC MULTIBIT

UDLY Uxxx LINEA DE RETARDO DIGITAL

UEFF Uxxx FLIP FLOP ACTIVADO POR FLANCOS

UGATE Uxxx COMPUERTA ESTANDAR

FLIP FLOP ACTIVADO POR

UGFF Uxxx

COMPUERTAS

UIO Uxxx MODELO DE E/S DIGITAL

UTGATE Uxxx COMPUERTA DE TERCER ESTADO

INTERRUPTOR CONTROLADO POR

ISWITCH Wxxx

CORRIENTE

NIGBT Zxxx IGBT DE CANAL N

[<nombre del parámetro=<valor del parámetro>] Se puede asignar valor a algunos, todos o ninguno de los

parámetros que definen a los dispositivos, ver en anexo B el listado completo. Para los parámetros no modificados

se utilizan los valores por omisión.

[especificación de tolerancia] La especificación de tolerancia se utiliza para efectuar análisis de Monte Carlo, el

formato para definir la tolerancia es:

[DEV [track&dist] <valor>[%]] [LOT [track&dist] <valor>[%]] Esta definición de tolerancia es para

cada parámetro que requiera asignarle tolerancia. La tolerancia LOT requiere que todos los dispositivos

que utilizan el mismo modelo tengan el mismo valor de tolerancia. La tolerancia DEV es independiente,

esto es, cada dispositivo que utiliza el modelo puede tener variaciones de tolerancia diferentes. El signo de

% define el valor de tolerancia como un porcentaje del valor del parámetro. Si es omitido, el valor se toma

en las mismas unidades del parámetro a variar.

[track&dist] Define el seguimiento y tipo de distribución de la variación, usando el siguiente formato:

[/<lot #>][/<nombre de distribución>] Estas definiciones deben seguir de las palabras DEV y LOT

(sin espacios) y deben estar separadas por un signo /.

<lot #> Especifica cual de los diez generadores de números aleatorios, numerados del 0 al 9, se

utilizarán para calcular el valor de desviación del parámetro.

<nombre de distribución> Especifica el tipo de distribución utilizada para el análisis. La

distribución utilizada por omisión puede fijarse con el parámetro DISTRIBUTION en la ventana

Cadence 343

OrCAD REL. 9.2 LITE](https://image.slidesharecdn.com/tutorial-orcad-9-2-120624191743-phpapp02/85/Tutorial-or-cad-9-2-352-320.jpg)

![cenidet

de configuración de PSPICE opción ANALYSIS, al configurar el análisis de MONTE

CARLO/WORST CASE.

Los siguientes parámetros se utilizan para introducir variaciones en algunos de los parámetros del dispositivo que

son afectados por la temperatura.

[T_MEASURED=<valor de temperatura>] Este parámetro anula el valor de TNOM definido en la opción

OPTIONS del perfil de simulación. PSPICE asume que todos los parámetros del dispositivo fueron extraidos a

esta temperatura.

[T_ABS=<valor de temperatura absoluta>] Define la temperatura del dispositivo AKO utilizado como modelo.

[T_REL_GLOBAL=<valor relativo a la temperatura actual>] Define la temperatura del dispositivo como la

temperatura global, fijada en análisis de temperatura o por TNOM, mas el valor relativo asignado.

[T_REL_LOCAL=<valor relativo al modelo AKO] Define la temperatura del dispositivo como la suma del valor

de T_ABS y el valor relativo asignado.

Sintaxis comando .SUBCKT

El comando .SUBCKT define el inicio de la descripción de un subcircuito. La descripción del subcircuito es una

red de conexiones de dispositivos que sigue las reglas de sintaxis de PSPICE, el final de la descripción del subcircuito debe

ser un comando .ENDS.

La definición del subcircuito debe contener el nombre del subcircuito, el nombre y orden de sus terminales, y los

nombres de los parámetros que definen su comportamiento. La sintaxis para definir subcircuitos es la siguiente:

.SUBCKT <nombre del subcircuito> [terminales]

+ [OPTIONAL: <nodo de interfaz>=<valor por omisión>]

+ [PARAMS: <nombre de parámetro>=<valor de parámetro>]

+ [TEXT: <nombre de parámetro de texto>=<nombre del archivo>]

.... (red de conexiones del subcircuito)

.ENDS

<nombre del subcircuito> Nombre del subcircuito utilizado como referencia en el campo

“IMPLEMENTATION” de los símbolos gráficos.

[terminales] Este campo es opcional, dado que es posible tener subcircuitos sin terminales de interfaz.

OPTIONAL: Permite especificar uno o mas terminales opcionales en la definición del subcircuito.

Cadence 344

OrCAD REL. 9.2 LITE](https://image.slidesharecdn.com/tutorial-orcad-9-2-120624191743-phpapp02/85/Tutorial-or-cad-9-2-353-320.jpg)

![cenidet

Anexo D.- Comandos de descripción de plantilla para símbolos de

PSPICE

Sintaxis de TEMPLATE

La propiedad TEMPLATE define la sintaxis de PSPICE para la entrada en el listado de red de la parte. Cuando se

crea un listado de red, CAPTURE substituye los valores del circuito en los lugares apropiados de la sintaxis de

TEMPLATE y guarda el comando traducido en el archivo de listado de red.

<letra del tipo de componente>^@REFDES %<terminal_1> .. %<terminal_n> <cadenas de control>

Existen tres reglas que hay que mantener presentes:

1.- Los nombre de las terminales en TEMPLATE deben ser iguales a las de la parte.

2.- El número y orden de las terminales listadas en TEMPLATE deben ser iguales a las definidas en el modelo o

subcircuito.

3.- El primer carácter en TEMPLATE debe ser una letra adecuada para el tipo de parte utilizada (por ejemplo, R

para resistencia, Q para BJT, etc.)

La sintaxis de TEMPLATE contiene:

a) caracteres regulares que el editor de esquemáticos interpreta literalmente,

b) nombre de propiedades y caracteres de control que el editor de esquemáticos traduce.

caracteres regulares en plantillas (TEMPLATES)

Los caracteres regulares incluyen alfanuméricos, cualquier carácter del teclado, con excepción de @, &, ?, ~, y #

que son utilizados como caracteres de control.

caracteres de control en plantillas.

Se define a un identificador como una cadena de caracteres regulares.

Los nombre de propiedades se preceden por un carácter especial de la siguiente manera:

[@ | ? | ~ | # | & ] identificador

La siguiente tabla muestra el significado de estas propiedades:

SINTAXIS ACCION

@<identficador> Se reemplaza por el valor del identificador, si el identificador está definido.

?<identificador> s...s Se reemplaza por el texto definido en s...s si el identificador está definido.

Se reemplaza por el primer texto definido en s...s si el identificador está definido, en caso

?<identificador> s...s s...s

contrario se reemplaza por el segundo texto.

~<identificador> s...s Se reemplaza por el valor definido en s...s si el identificador no está definido.

Cadence 346

OrCAD REL. 9.2 LITE](https://image.slidesharecdn.com/tutorial-orcad-9-2-120624191743-phpapp02/85/Tutorial-or-cad-9-2-355-320.jpg)