Apuntes ci 555

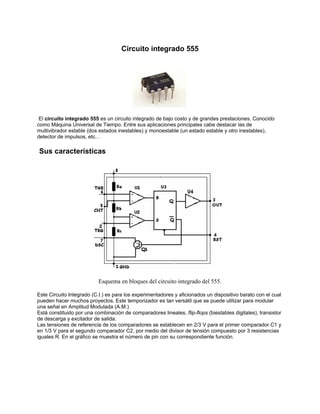

- 1. Circuito integrado 555 El circuito integrado 555 es un circuito integrado de bajo costo y de grandes prestaciones. Conocido como Máquina Universal de Tiempo. Entre sus aplicaciones principales cabe destacar las de multivibrador estable (dos estados inestables) y monoestable (un estado estable y otro inestables), detector de impulsos, etc… Sus características Esquema en bloques del circuito integrado del 555. Este Circuito Integrado (C.I.) es para los experimentadores y aficionados un dispositivo barato con el cual pueden hacer muchos proyectos. Este temporizador es tan versátil que se puede utilizar para modular una señal en Amplitud Modulada (A.M.) Está constituido por una combinación de comparadores lineales, flip-flops (biestables digitales), transistor de descarga y excitador de salida. Las tensiones de referencia de los comparadores se establecen en 2/3 V para el primer comparador C1 y en 1/3 V para el segundo comparador C2, por medio del divisor de tensión compuesto por 3 resistencias iguales R. En el gráfico se muestra el número de pin con su correspondiente función.

- 2. Descripción de las Patas o Pines del Temporizador 555 .- GND (PIN 1): es el polo negativo de la alimentación, generalmente tierra. .- Disparo (PIN 2): Es en esta patilla, donde se establece el inicio del tiempo de retardo, si el 555 es configurado como monoestable. Este proceso de disparo ocurre cuando este pin va por debajo del nivel de 1/3 del voltaje de alimentación. Este pulso debe ser de corta duración, pues si se mantiene bajo por mucho tiempo la salida se quedará en alto hasta que la entrada de disparo pase a alto otra vez. .- Salida (PIN 3): Aquí veremos el resultado de la operación del temporizador, ya sea que esté conectado como monoestable, astable u otro. Cuando la salida es alta, el voltaje será el voltaje de alimentación (Vcc) menos 1.7 Voltios. Esta salida se puede obligar a estar en casi 0 voltios con la ayuda de la patilla de reset (PIN 4). .- Reset (PIN 4): Si se pone a un nivel por debajo de 0.7 Voltios, pone la patilla de salida a nivel bajo. Si por algún motivo esta patilla no se utiliza hay que conectarla a Vcc para evitar que el 555 se "resetee". .-Control de voltaje (PIN 5): Cuando el temporizador se utiliza en el modo de controlador de voltaje, el voltaje en esta patilla puede variar casi desde Vcc (en la práctica como Vcc -1 voltio) hasta casi 0 V (aprox. 2 Voltios). Así es posible modificar los tiempos en que la salida está en alto o en bajo independiente del diseño (establecido por las resistencias y condensadores conectados externamente al 555). El voltaje aplicado a la patilla de control de voltaje puede variar entre un 45 y un 90 % de Vcc en la configuración monoestable. Cuando se utiliza la configuración astable, el voltaje puede variar desde 1.7 voltios hasta Vcc. Modificando el voltaje en esta patilla en la configuración astable causará la frecuencia original del astable sea modulada en frecuencia (FM). Si esta patilla no se utiliza, se recomienda ponerle un condensador de 0.01μF para evitar las interferencias. .- Umbral (PIN 6): Es una entrada a un comparador interno que tiene el 555 y se utiliza para poner la salida a nivel bajo. .- Descarga (PIN 7): Utilizado para descargar con efectividad el condensador externo utilizado por el temporizador para su funcionamiento. .-Vcc (PIN 8): Alimentación, es el pin donde se conecta el voltaje de alimentación que va de 4.5 voltios hasta 16 voltios (máximo). Funcionamiento del Circuito Integrado 555 El temporizador 555 se puede conectar para que funcione de diferentes maneras, entre los más importantes están: como multivibrador astable y como multivibrador monoestable. FUNCIONAMIENTO EN MODO ASTABLE: En el esquema de la figura se muestra la forma de conectar el circuito integrado 555 en el modo Astable, es decir como generador de trenes de pulsos.

- 3. C.I. 555 en su configuración Astable Esta configuración se denomina comúnmente circuito clock o de reloj, también timmer. Observe que la entrada de umbral (Pin6) está conectada a la entrada de disparo (PIN 2). El circuito formado por las resistencias RA y RB y el condensador C1 controla el voltaje de entrada de los comparadores. Cuando se conecta la fuente de alimentación, este voltaje es de 0v porque C1 está completamente descargado. Bajo esta condición, el comparador de umbral aplica un nivel bajo a la entrada R del FLIP-FLOP y al de disparo un nivel alto a la entrada S. Como resultado, la salida del circuito (pin3) muestra un nivel alto. Al mismo tiempo, la salida Q negado del FLIP-FLOP es de nivel bajo, el transistor de descarga está OFF, es decir en estado de corte, y C1 comienza a cargarse libremente a través de R1y R2. A medida que C1 se carga, el voltaje en sus terminales crece hasta alcanzar el valor de umbral (2/3 de VCC). Cuando esto sucede, el comparador de umbral aplica un nivel alto a la entrada R del FLIP-FLOP y el de disparo un nivel bajo a la entrada S del mismo. Como resultado, la salida del circuito (pin 3) se hace baja, la salida Q negado se hace alta, el transistor pasa al estado ON, es decir conduce, y el condensador C1 comienza a descargarse a través de la resistencia R2. Cuando el voltaje sobre C1 se hace ligeramente inferior al voltaje de disparo (1/3 de VCC), el comparador de disparo aplica un alto a la entrada S del FLIP-FLOP y el de umbral un bajo a la entrada R. La salida del circuito se hace nuevamente alta y se repite el mismo ciclo anterior. Como resultado de la carga y descarga de C1 la salida oscila indefinidamente entre los niveles alto y bajo, entregando de esta forma un tren continuo de pulsos que presentará una determinada frecuencia. En el esquema gráfico se representa este proceso.

- 4. Ecuaciones que definen la configuración Astable 1. Tiempo de Carga )()(693,01 segCRBRA ⋅+=τ 2.- Tiempo de Descarga )(693,02 segCRA⋅=τ 3.- Período )(21 segT ττ += )(2)2(693,0 segRBRAT += 4.- Frecuencia )( 1 Hz T f = )( )2(693,0 1 Hz CRBRA f + = 5.- Tasa de trabajo (DUTY CYCLE) (%)100 21 1 ⋅ + = ττ τ DC %100 )2( )( ⋅ + + = RBRA RBRA DC Nota: La configuración vista del 555 es para una tasa de trabajo (DUTY CYCLE) mayor al 50%. Para obtener una tasa de trabajo menor o igual al 50% hay que independizar las ecuaciones del tiempo en alta y tiempo en baja; y eso se logra utilizando un diodo rectificador en paralelo a RB como muestra la siguiente figura: Ecuaciones: 1.- tiempo de carga )(693,0 segCRAalta ⋅⋅=τ 2.- tiempo en baja )(693,0 segCRBbaja ⋅⋅=τ 3.- Período bajaaltaT ττ += 4.- Frecuencia )( 1 Hz T f = 5.- Tasa de trabajo %100⋅= T alta DC τ FUNCIONAMIENTO EN EL MODO MONOESTABLE:

- 5. En el circuito de la figura se muestra la forma de conectar el integrado LM-555 en el modo Monoestable, es decir como generador de pulsos de duración definida. Esta configuración se denomina comúnmente temporizador. Observar que la entrada de Umbral Pin 6 está conectada a la salida de descarga (Pin 7). Configuración Monoestable El circuito formado por la resistencias R2 y RA, el condensador C1 y el pulsador S1 , controla el voltaje de entrada aplicado a cada comparador y establece el momento de arranque y la duración del pulso de salida. En condiciones normales, con el pulsador S1, la entrada de disparo (PIN 2) está conectada a +VCC a través de R2 y el comparador de disparo (U2) aplica un nivel de tensión bajo a la entrada S del flip-flop. Al mismo tiempo, la salida del temporizador (Pin 3) es de nivel bajo. La salida Q del flip-flop es alta, el transistor Q1 está en saturación y su colector (PIN 7), descarga el condensador Cl y conecta a tierra la entrada de umbral (PIN 6). Como resultado, el comparador de umbral aplica un nivel bajo a la entrada R del flip-flop. Puesto que la entrada S del mismo es también de nivel bajo, el estado previo de la salida (PIN 3) se mantiene, es decir sigue en nivel bajo. Cuando se pulsa momentáneamente S1, el (PIN 2) recibe un nivel bajo y el comparador de disparo aplica un nivel alto a la entrada S del flip-flop. Como resultado, el (PIN 3) pasa del estado de nivel bajo al estado de nivel alto. Al liberar el pulsador S1, la entrada S retorna otra vez al estado de nivel bajo, pero la salida se mantiene en un nivel alto. Al mismo tiempo, la salida Q del flip-flop es baja, el transistor Q1 está off y el condensador C1 comienza a cargarse a través de la resistencia RA. Cuando el voltaje sobre C1 se hace ligeramente superior a los 2 / 3 de VCC, el comparador de umbral aplica un nivel alto a la entrada R del flip-flop y la salida del circuito adquiere nuevamente un nivel bajo. Como consecuencia de este proceso, la salida ha permanecido en un nivel alto durante un determinado tiempo, contado a partir del momento en que se aplicó la señal de disparo mediante S1. En otras palabras, el circuito ha emitido un pulso. La duración de este pulso viene determinado por :