7842803 capitulo2-arquitectura-del-a tmega32-espanol

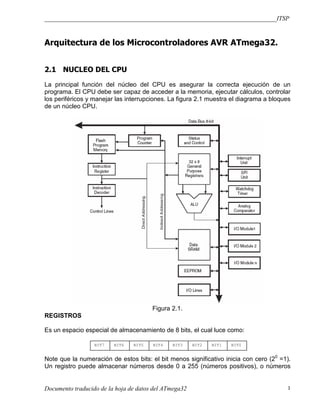

- 1. __________________________________________________________________________ITSP Documento traducido de la hoja de datos del ATmega32 1 Arquitectura de los Microcontroladores AVR ATmega32. 2.1 NUCLEO DEL CPU La principal función del núcleo del CPU es asegurar la correcta ejecución de un programa. El CPU debe ser capaz de acceder a la memoria, ejecutar cálculos, controlar los periféricos y manejar las interrupciones. La figura 2.1 muestra el diagrama a bloques de un núcleo CPU. Figura 2.1. REGISTROS Es un espacio especial de almacenamiento de 8 bits, el cual luce como: Note que la numeración de estos bits: el bit menos significativo inicia con cero (20 =1). Un registro puede almacenar números desde 0 a 255 (números positivos), o números BIT7 BIT6 BIT5 BIT4 BIT3 BIT2 BIT1 BIT0

- 2. __________________________________________________________________________ITSP Documento traducido de la hoja de datos del ATmega32 2 desde -128 a 127 (números con signo y magnitud), o valores que representan caracteres en el código ASCII. Las características especiales de los registros, comparados con otros sitios de almacenamiento, es que: Ellos se usan directamente en los comandos en ensamblador. Las operaciones de su contenido requieren solamente comandos de una palabra. Ellos están ligados directamente a la Unidad Central de Procesamiento. Ellos son la fuente o destino de los argumentos en las operaciones. Existen 32 registros en un AVR. Ellos se nombran como R0 a R31, pero puedes renombrarlos usando las directivas del ensamblador. Los AVR utilizan la Arquitectura Harvard, con el bus de datos y el bus de memorias separados. Mientras una instrucción se ejecuta, la próxima instrucción esta lista para ser ejecutada en la memoria de programa. Las instrucciones se ejecutan en cada ciclo de reloj. La memoria de programa esta en la memoria Flash. Al ejecutarse una operación en la ALU, los dos operandos están a la salida del archivo de registros y el resultado se almacena al fondo del archivo de registros en un solo ciclo de reloj. Seis de los 32 registros se pueden usar como registros apuntadores de direccionamiento indirecto a 16 bits para datos almacenados en memoria, siendo los registros de 16 bits X, Y y Z. Después de realizar una operación aritmética el Registro de Estado actualiza la información acerca del resultado de la operación. Durante las interrupciones o llamados a subrutinas, la dirección del Contador de Programa se almacena en la pila. La pila se localiza en la SRAM. El usuario al inicio de un programa deberá inicializar el SP en la rutina de reset. El espacio de memoria de I/O contiene 64 direcciones para las funciones periféricas del CPU como Registros de Control, SPI, y otras funciones de I/O. Las operaciones de la ALU se dividen en tres categorías, aritméticas, lógicas y operaciones a bits. REGISTRO DE ESTADO Este registro contiene información del resultado más reciente de la operación aritmética. Así, esta información puede ser útil para alterar el flujo del programa y ejecutar operaciones condicionales. Puede ser manejado por software. La figura 2.2 muestra los bits que maneja.

- 3. __________________________________________________________________________ITSP Documento traducido de la hoja de datos del ATmega32 3 Bit 7 – I: Habilitación de Interrupción Global. Se pone a 1 para habilitar las interrupciones. Si el bit esta en 0 ninguna interrupción se habilita. El bit I se limpia por hardware después de que una interrupción ha ocurrido, y es puesto a 1 por la instrucción RETI para habilitar las interrupciones subsecuentes. Bit 6 – T: Copia de un Bit. Un bit de un registro puede ser copiado al registro T por la instrucción BST (Bit STore) y el bit T puede ser copiado a un bit de un registro por la instrucción BLD (Bit LoaD). Bit 5 – H: Registro de Acarreo Intermedio. La bandera de acarreo intermedio se indica en cualquier operación aritmética. Se usa en operaciones en BCD. Bit 4 – S: Bit de Signo. Bit 3 – V: Bandera de Sobreflujo en Complemento a Dos. Bit 2 – N: Bandera de Negativo. Indica cuando un resultado es negativos de una operación aritmética o lógica. Bit 1 – Z: Bandera de Cero. Indica si el resultado es un cero de una operación aritmética o lógica. Bit 0 – C: Bandera de Acarreo. Indica un acarreo de una operación aritmética o lógica. REGISTROS DE TRABAJO DE PROPOSITO GENERAL En la figura 2.3 se observa el archivo de registros, donde los 32 registros de propósito general de 8 bits se localizan al inicio de las direcciones de memoria de la SRAM (0000h a la 001Fh).

- 4. __________________________________________________________________________ITSP Documento traducido de la hoja de datos del ATmega32 4 Figura 2.3. A partir de la dirección 001Ah a la 001Fh, comienzan los 3 registros de 16 bits (X, Y y Z), los cuales actúan como apuntadores de direcciones para direccionamiento indirecto a espacio de datos. Figura 2.4.

- 5. __________________________________________________________________________ITSP Documento traducido de la hoja de datos del ATmega32 5 APUNTADOR DE PILA La Pila se usa principalmente para almacenar datos temporales, para almacenamiento local de variables y para almacenar direcciones de retorno después de las interrupciones y los llamados a subrutina. El Registro de Apuntador de Pila siempre apunta al principio de la Pila. El Apuntador de la Pila apunta a los datos de la SRAM que funcionan como pila. El espacio de la pila la define el usuario y deberá apuntar a una dirección arriba de la 0060h TIEMPO DE EJECUCION DE UNA INSTRUCCION Ejecución y almacenamiento en fila de una instrucción. Ejecución en paralelo de la Arquitectura Harvard, se muestra en la figura 2.5. Figura 2.5. 2.2 MEMORIA DE PROGRAMA Y DE DATOS DEL AVR ATmega32. La arquitectura AVR tiene dos espacios principales de memoria, la Memoria de Datos y la Memoria de Programa. Así como también el Atmega32 posee la Memoria EEPROM para almacenar datos. El Atmega32 contiene 32K bytes de memoria Flash Reprogramable para almacenar el programa. Ya que todas las instrucciones de los AVR son de 16 o 32 bits de ancho, la Flash se organiza en 16K x 16. La memoria de Programa Flash se divide en dos secciones, la sección de “Booteo” de Programa y la sección de Aplicación del Programa. El contador de programa (PC) es de 14 bits de ancho, así direcciona localidades en la memoria de programa de 16K, véase la figura 2.5.

- 6. __________________________________________________________________________ITSP Documento traducido de la hoja de datos del ATmega32 6 Figura 2.6. Las 2144 (860h) localidades de Memoria de Datos direccionan el Archivo de Registros, la Memoria de I/O y los datos internos de la SRAM. Las primeras 96 (60h) localidades direccionan el Archivo de Registros y la Memoria de I/O, y las siguientes 2048 localidades direccionan los datos internos de la SRAM, véase la figura 2.7. Figura 2.7.

- 7. __________________________________________________________________________ITSP Documento traducido de la hoja de datos del ATmega32 7 2.3 SISTEMA DE RELOJ. En la figura 2.8 se muestra el sistema de reloj y su distribución para la arquitectura AVR. Puede que no todos los relojes estén activos al mismo tiempo. Para reducir el consumo de potencia, los relojes que no están siendo usados se paran usando los diferentes modos de ahorro de energía. Figura 2.8. Reloj del CPU – clkCPU. El reloj del CPU se dirige a las partes del sistema concernientes con la operación del núcleo AVR. Tales módulos serán el Archivo de Registros de Propósito General, el Registro de Estado y el Apuntador de Pila. Parando el reloj del CPU se inhibe el núcleo. Reloj de I/O – clkI/O. El reloj de I/O se usa para la mayoría de los módulos de I/O, tales como los Timers/Contadores, SPI y el USART, así como también el Módulo de Interrupciones Externas. Reloj de la Flash – clkFLASH. El reloj de la Flash controla la operación de la interfase Flash. Se activa simultáneamente con el reloj del CPU.

- 8. __________________________________________________________________________ITSP Documento traducido de la hoja de datos del ATmega32 8 Reloj del Timer Asíncrono – clkASY. El timer de reloj asíncrono permite recibir directamente un cristal externo de 32 KHz. Reloj del ADC – clkADC. El ADC es provisto con un reloj de dominio dedicado. Esto permite parar los relojes del CPU y de I/O para reducir el ruido generado por la circuitería digital. Esto proporciona más precisión en la conversión del ADC. FUENTES DE RELOJ El dispositivo tiene las siguientes fuentes de reloj, seleccionables por los bits de Flash Fusibles. El reloj de la fuente seleccionado es la entrada al reloj generador del AVR y se dirige a los módulos apropiados. Las fuentes de reloj son: Oscilador Externo RC, Reloj Externo, Cristal Oscilador, Oscilador de Cristal a Baja Frecuencia y el Oscilador Calibrado RC. El dispositivo es fabricado con un Oscilador Interno RC como fuente de reloj por default de 1 MHz. 2.4 ARCHIVO DE REGISTROS. La tabla 2.1 muestra el archivo de registros que utilizan el ATmega32, así como sus direcciones. Además de la lista se procederá a dar una breve explicación de los mismos, considerando que más adelante se realizara un análisis más profundo conforme se vean los ejercicios de aplicación. PUERTOS O REGISTROS DEL AVR ATMEGA32. Los puertos o registros especiales en el AVR son compuertas desde la Unidad Central de Procesamiento a los componentes de software y hardware tanto internos como externos. La comunicación del CPU con estos componentes es para leer o escribir en ellos. Existen 64 puertos diferentes, los cuales tienen una dirección fija. No tienes que memorizar todas las direcciones, ya que en el archivo de definición del ATmega32 vienen los alias. Por ejemplo, .EQU PORTB, 0x18.

- 9. __________________________________________________________________________ITSP Documento traducido de la hoja de datos del ATmega32 9

- 10. __________________________________________________________________________ITSP Documento traducido de la hoja de datos del ATmega32 10 SREG. Registro de Estado. Este registro contiene la información del resultado más reciente de una operación aritmética. SPH, SPL. Registro Apuntador de Pila. El Apuntador de la Pila apunta a los datos de la SRAM que funcionan como pila. Este apuntador del AVR se implementa en 2 registros de 8 bits como espacio de I/O. OCR0. REGISTRO DE COMPARACION DE SALIDA. Este registro contiene un valor de 8 bits que se compara continuamente con el valor del contador (TCNT0). Al ser iguales puede generar una interrupción de salida por comparación o generar una forma de onda de salida en el pin OC0. GICR. REGISTRO GENERAL DE CONTROL DE INTERRUPCIONES. Contiene los bits de habilitación de las interrupciones externas INT0, INT1 e INT2. Así como también los bits para mover el vector de interrupciones a principio de la memoria Flash o al inicio de la sección de “Boot”. GIFR. REGISTRO GENERAL DE BANDERAS DE LAS INTERRUPCIONES. Contiene las banderas de las interrupciones externas INT0, INT1 e INT2 cuando estas estén activas. TIMSK. REGISTRO ENMASCARABLE DE INTERRUPCIÓN DEL TIMER/CONTADOR. Contiene los bits para habilitar los registros de comparación y habilitar las interrupciones para cuando se cumpla la igualdad. TIFR. REGISTRO DE BANDERAS DE INTERRUPCIONES DEL TIMER/CONTADOR. Contiene los bits de las banderas cuando se cumpla la igualdad en la comparación del Timer/Contador y el dato de OCR. Así como también contiene los bits de bandera de Sobreflujo de los Timer/Contador. SPMCR. REGISTRO DE CONTROL PARA ALMACENAR EN LA MEMORIA DEL PROGRAMA. Este Registro contiene los bits necesarios para controlar las operaciones de “Boot Loader”. TWCR. REGISTRO DE CONTROL DE DOS LÍNEAS. Se usa para habilitar la Comunicación a Dos Líneas (TWI), al iniciar un acceso aplicando la condición de INICIO en el bus, generar un reconocimiento del receptor, generar la condición de stop, y controlar el bus mientras los datos de escriben en él. Así como también indica cuando existe una colisión de escritura si los datos se intentan escribir en TWDR y el registro no está disponible. MCUCR. REGISTRO DE CONTROL DE LA UNIDAD DEL MICROCONTROLADOR (MCU). Este registro contiene los bits de control para el manejo de la Energía. MCUCSR. REGISTRO DE CONTROL Y ESTADO DEL MCU. Este registro provee información acerca de cuales fueron las fuentes que causaron el reinicio del MCU.

- 11. __________________________________________________________________________ITSP Documento traducido de la hoja de datos del ATmega32 11 TCCR0. REGISTRO DE CONTROL DEL TIMER/CONTADOR “0”. TCNT0. REGISTRO DEL TIMER/CONTADOR “0”. OSCCAL. REGISTRO DE CALIBRACION DEL OSCILADOR. Escribiendo en este byte de calibración hará una variación en la frecuencia del oscilador. OSCDR. REGISTRO DE DEBUG DENTRO DEL SISTEMA. Este registro provee un canal de comunicación desde un programa corriendo en el microcontrolador hacia el debugger. SFIOR. REGISTRO DE FUNCIÓN ESPECIAL DE I/O. Ajusta el Pre-escalador del Timer 0, 1 y 2. Así como selecciona las fuentes para el auto-disparo. TCCR1A. REGISTRO DE CONTROL “A” PARA EL TIMER/CONTADOR “1”. TCCR1B. REGISTRO DE CONTROL “B” PARA EL TIMER/CONTADOR “1”. TCNT1H y TCNT1L. Las dos localidades del Timer/Contador I/O se combinan para TCNT1, dan acceso directo, ambas operaciones para leer y escribir, a la unidad de Timer/Contador de 16 bits. OCR1AH y OCR1AL; OCR1BH y OCR1BL. Los registros de Comparación de Salida contienen un valor de 16 bits que continuamente se compara con el valor del contador TCNT1. Una igualdad genera una interrupción de comparación de salida, o genera una forma de onda de salida en el pin OC1x. ICR1H e ICR1L. REGISTRO DE CAPTURA DE ENTRADA “1”. Este registro se actualiza con el valor del contador (TCNT1) cada vez que un evento ocurre en el pin ICP1 (o con el comparador análogo de salida para el Timer/Contador 1). TCCR2. REGISTRO DE CONTROL PARA EL TIMER/CONTADOR “2”. TCNT2. REGISTRO DEL TIMER/CONTADOR. Este registro da acceso directo, a ambas operaciones para leer y escribir a la unidad de 8 bits del contador. Escribiendo al registro TCNT2 remueve la comparación en el siguiente ciclo de reloj. OCR2. REGISTRO DE COMPARACION DE SALIDA “2”. Este registro contiene un valor de 8 bits que continuamente se compara con el valor del contador TCNT2. Una igualdad genera una interrupción de comparación de salida, o genera una forma de onda de salida en el pin OC2. ASSR. REGISTRO DE ESTADO ASÍNCRONO. WDTCR. REGISTRO DE CONTROL DEL TIMER “WATCHDOG”.

- 12. __________________________________________________________________________ITSP Documento traducido de la hoja de datos del ATmega32 12 UBRRH. PARTE ALTA DEL REGISTRO DE BAUD RATE DE LA UNIDAD DE TRANSFERENCIA SERIAL UNIVERSAL SINCRONA Y ASINCRONA (USART). UCSRC. REGISTRO “C” DE CONTROL Y ESTADO DE LA UNIDAD DE TRANSFERENCIA SERIAL UNIVERSAL SINCRONA Y ASINCRONA (USART). EEARH y EEARL. REGISTRO DE DIRECCIÓN DE LA PARTE ALTA Y BAJA DE LA EEPROM. EEDR. REGISTRO DE DATOS DE LA EEPROM. EECR. REGISTRO DE CONTROL DE LA EEPROM. PORTA. REGISTRO DE DATOS DEL PUERTO “A”. DDRA. REGISTRO DE DIRECCIÓN DE DATOS DEL PUERTO “A”. PINA. DIRECCIONES DE LOS PINS DE ENTRADA DEL PUERTO “A”. PORTB. REGISTRO DE DATOS DEL PUERTO “B”. DDRB. REGISTRO DE DIRECCIÓN DE DATOS DEL PUERTO “B”. PINB. DIRECCIONES DE LOS PINS DE ENTRADA DEL PUERTO “B”. PORTC. REGISTRO DE DATOS DEL PUERTO “C”. DDRC. REGISTRO DE DIRECCIÓN DE DATOS DEL PUERTO “C”. PINC. DIRECCIONES DE LOS PINS DE ENTRADA DEL PUERTO “C”. PORTD. REGISTRO DE DATOS DEL PUERTO “D”. DDRD. REGISTRO DE DIRECCIÓN DE DATOS DEL PUERTO “D”. PIND. DIRECCIONES DE LOS PINS DE ENTRADA DEL PUERTO “D”. SPDR. REGISTRO DE DATOS DE LA INTERFASE SERIAL PERIFERICA (SPI). En este registro se lee y se escribe y se usa para transferir datos entre el Archivo de Registros y el Registro de corrimiento SPI. Al escribir en este registro comienza la transmisión de datos. Al leer este registro causa que el Registro de corrimiento sea almacenado en el buffer. SPSR. REGISTRO DE ESTADO DE LA INTERFASE SERIAL PERIFERICA (SPI). SPCR. REGISTRO DE CONTROL DE LA INTERFASE SERIAL PERIFERICA (SPI)

- 13. __________________________________________________________________________ITSP Documento traducido de la hoja de datos del ATmega32 13 UDR. REGISTRO DE DATOS DE I/O DEL USART. UCSRA. REGISTRO “A” DE CONTROL Y ESTADO DE LA UNIDAD DE TRANSFERENCIA SERIAL UNIVERSAL SINCRONA Y ASINCRONA (USART). UCSRB. REGISTRO “B” DE CONTROL Y ESTADO DE LA UNIDAD DE TRANSFERENCIA SERIAL UNIVERSAL SINCRONA Y ASINCRONA (USART). UBRRL. PARTE BAJA DEL REGISTRO DE BAUD RATE DEL USART. ACSR. REGISTRO DE CONTROL Y ESTADO DEL COMPARADOR ANÁLOGO. ADMUX. REGISTRO DE SELECCIÓN DEL ADC MULTIPLEXADO. ADCSRA. REGISTRO “A” DE CONTROL Y ESTADO DEL ADC. ADCH y ADCL. REGISTRO DE DATOS DE LA CONVERSION DEL ADC PARTE ALTA Y BAJA. TWDR. REGISTRO DE DATOS DE LA COMUNICACIÓN A DOS LÍNEAS. En modo de Transmisión, TWDR contiene el próximo byte a ser transmitido. En modo Recepción, TWDR contiene el último byte recibido. TWAR. REGISTRO DE DIRECCIÓN DE LA COMUNICACIÓN A DOS LÍNEAS. TWAR deberá ser cargado con 7 bits de direcciones como esclavo, al cual TWI responderá cuando sea programado como transmisor o receptor esclavo. TWSR. REGISTRO DE ESTADO DE LA COMUNICACIÓN A DOS LÍNEAS. TWBR. REGISTRO DEL BIT RATE DE LA COMUNICACIÓN A DOS LÍNEAS. 2.5 OPERACIÓN DE RESET. Durante el RESET, todos los Registros de I/O son puestos en sus valores iniciales, y el programa comienza su ejecución desde el Vector Reset. La instrucción colocada en este Vector deberá ser un Salto Absoluto (JMP) a la rutina del programa ubicado en la memoria Flash o al área de “boot”. Las fuentes de RESET en el ATmega32 son 5: Power-on Reset. El MCU se reinicia cuando la fuente de voltaje esta por debajo del umbral VPOT. Reset Externo. El MCU se reinicia cuando un nivel bajo esta presente en el pin RESET por un tiempo de longitud mínimo a un pulso.

- 14. __________________________________________________________________________ITSP Documento traducido de la hoja de datos del ATmega32 14 Reset Watchdog. El MCU se reinicia cuando el periodo del Timer de Watchdog expira y el Watchdog esta habilitado. Brown-out Reset. El MCU se reinicia cuando la fuente de voltaje VCC esta por debajo del umbral VBOT y el Detector de Brown-out esta habilitado. JTAG AVR Reset. El MCU se reinicia tan pronto como haya un uno lógico en el Registro Reset. Figura 2.9.

- 15. __________________________________________________________________________ITSP Documento traducido de la hoja de datos del ATmega32 15 2.6 INTERRUPCIONES. Esta sección describe las especificaciones para el manejo de interrupciones que ejecuta el ATmega32. la tabla siguiente muestra el lugar de los vectores de Reset e Interrupción. Si un programa no habilita una fuente de interrupción, el Vector de Interrupciones no se usa, y el código de un programa regular puede ser colocado en estas localidades de memoria.

- 16. __________________________________________________________________________ITSP Documento traducido de la hoja de datos del ATmega32 16 Un programa para el Atmega32 con el vector completo de interrupciones se declara de la siguiente manera:

- 17. __________________________________________________________________________ITSP Documento traducido de la hoja de datos del ATmega32 17 2.7 PUERTOS DE ENTRADA/SALIDA. Todos los puertos de los AVRs tienen la característica de Leer-Modificar-Escribir, esto significa que la dirección de un pin de un puerto puede leerse o escribirse sin modificar al resto de los pines, usando las instrucciones SBI o CBI. Son tres localidades de memoria de I/O las que se asignan por cada puerto, una para el Registro de Datos – PORTx, otra para el Registro de Dirección de Datos – DDRx, y otra para los Pines del Puerto de Entrada – PINx. La localidad de I/O de los Pines de Puerto de Entrada es de lectura solamente, mientras que el Registro de Datos y el Registro de Dirección de Datos son de Lectura/Escritura. En suma, para deshabilitar la función del Pull-Up para todos los pines en los puertos se deberá colocar a uno el bit PUD en el registro SFIOR. Configuración de un Pin Cada pin del puerto consiste de tres registros de bits: DDRx, PORTxn y PINxn. Los bits DDxn se accesan en la dirección de I/O DDRx, los bits de PORTx en la dirección de I/O PORTx, y los bits de PINx en la dirección de I/O PINx. El bit DDxn en el Registro DDRx selecciona la dirección de ese pin. Si a DDxn se le escribe un uno lógico, Pxn se configura como un pin de salida. Si a DDxn se le escribe un cero lógico, Pxn se configura como un pin de entrada. Si se le escribe a PORTxn un uno lógico cuando el pin esta configurado como un pin de entrada, el resistor pull-up se activa. Para desactivar al resistor de pull-up, se le escribirá un cero lógico a PORTxn o se configura el pin como salida. Los pines de los puertos son de tres-estados cuando se tiene la condición de reset.

- 18. __________________________________________________________________________ITSP Documento traducido de la hoja de datos del ATmega32 18 Las configuraciones de los Puertos de los pines se muestran a continuación: En el siguiente ejemplo se muestra como configurar al Puerto B los pines 0 y 1 en alto, 2 y 3 en bajo y se definen los pines de 4 a 7 como entradas con pull-ups asignados a los pines 6 y 7. Una instrucción nop se incluye antes de leer el puerto de entrada justamente después de configurarlo como entrada.