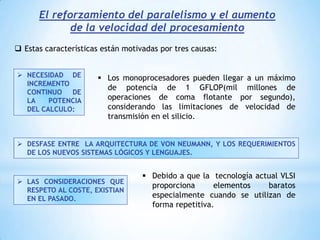

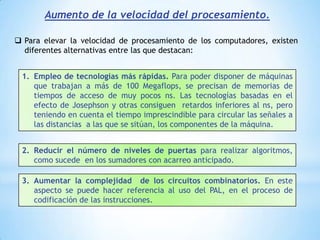

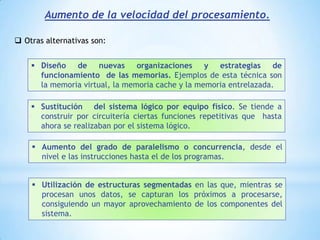

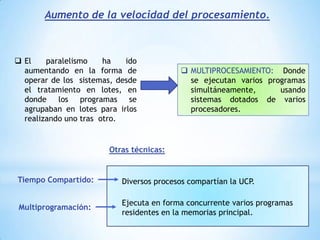

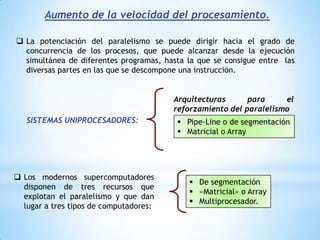

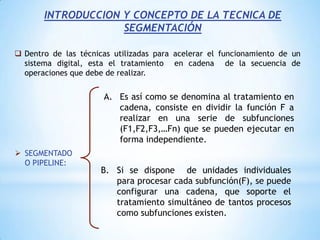

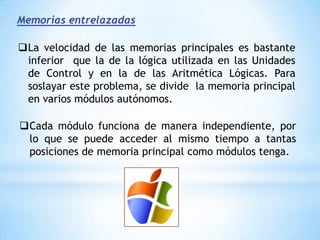

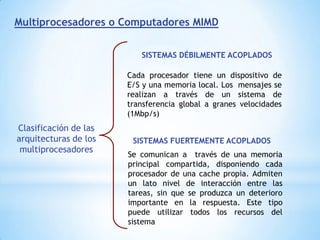

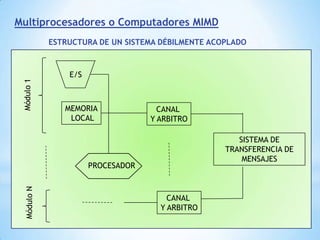

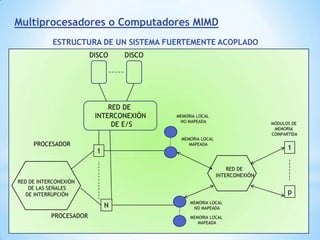

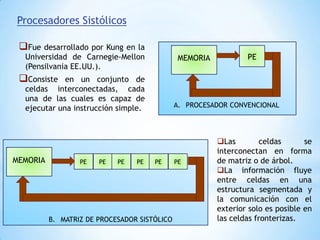

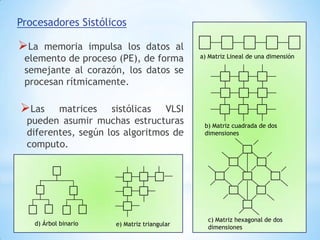

Este documento describe formas de aumentar la velocidad y el paralelismo en computadores de alto rendimiento. Menciona que el procesamiento paralelo es necesario para aplicaciones que requieren grandes cantidades de datos, como procesamiento de imágenes en tiempo real. Luego detalla algunas estrategias como usar tecnologías más rápidas, reducir los niveles de puertas lógicas, aumentar la complejidad de circuitos combinatorios, mejorar el diseño de memorias y sustituir parte del sistema lógico por hardware dedicado.