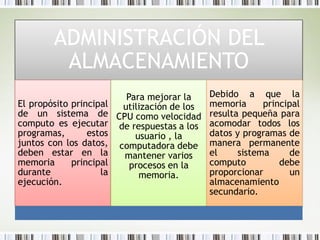

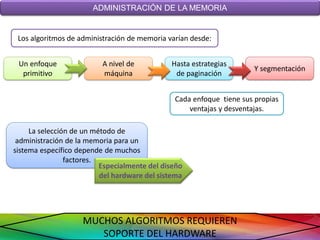

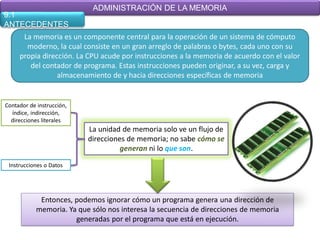

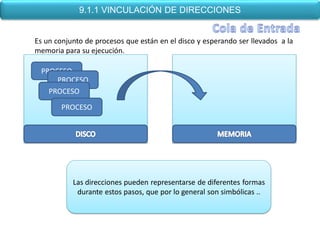

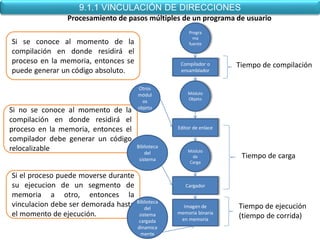

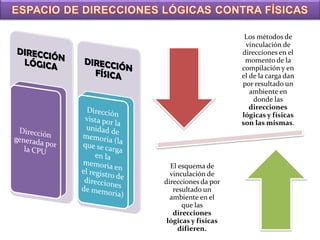

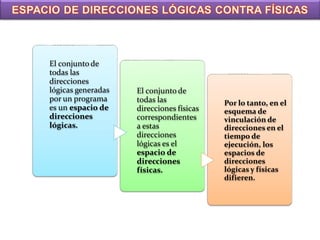

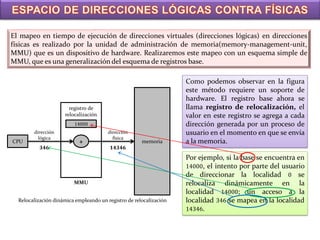

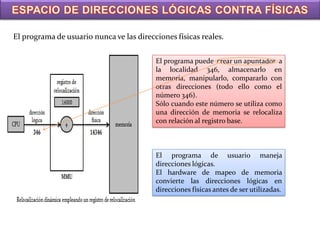

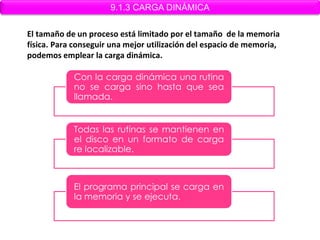

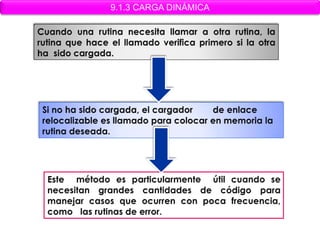

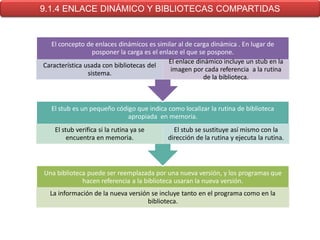

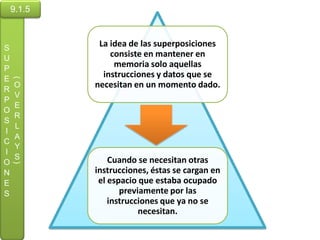

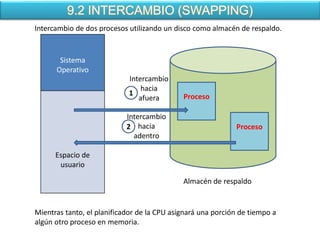

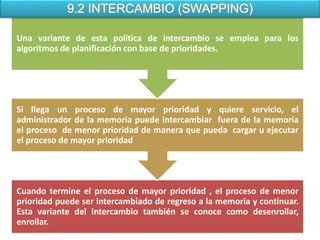

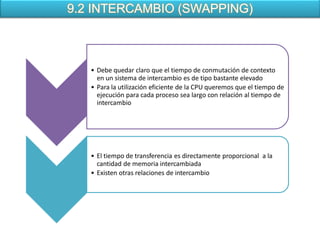

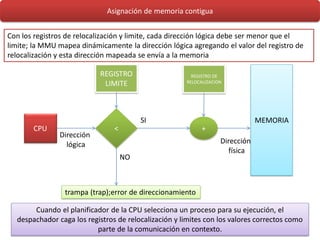

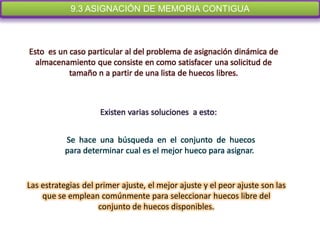

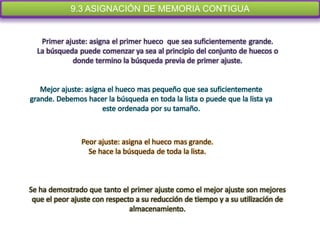

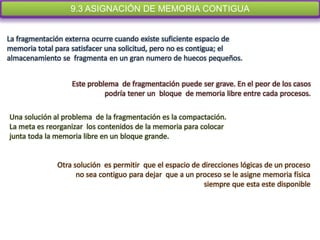

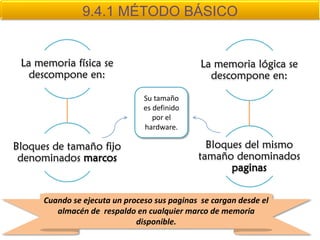

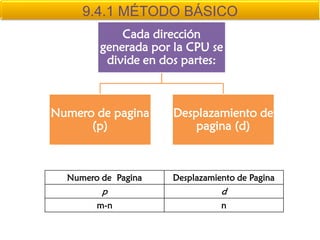

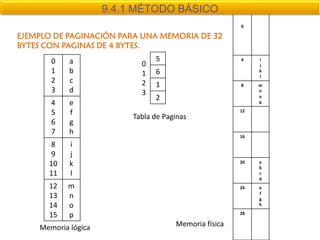

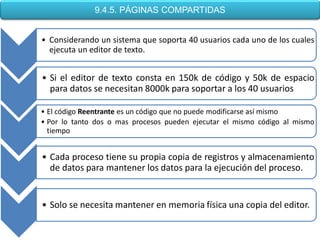

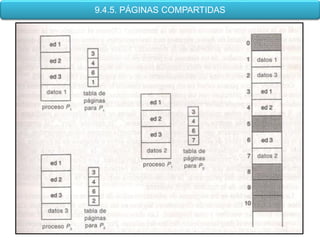

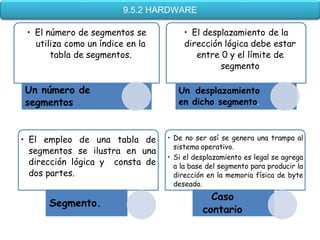

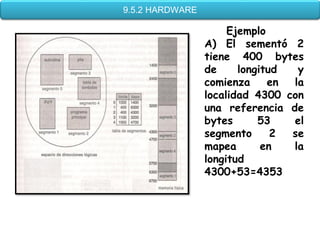

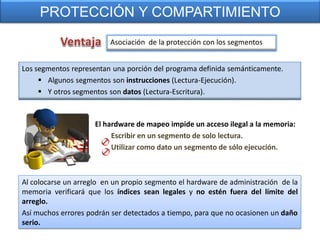

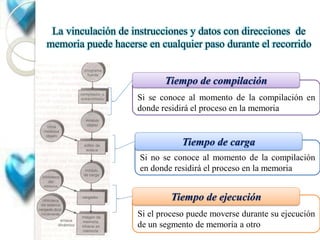

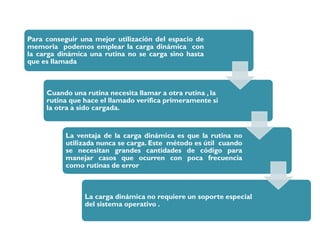

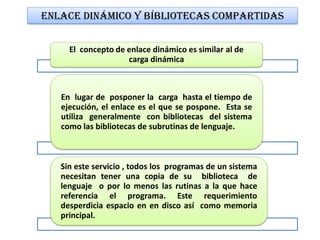

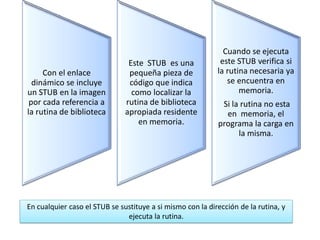

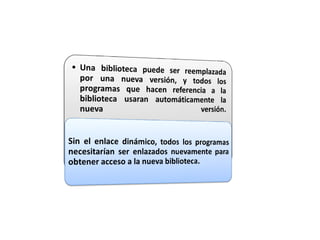

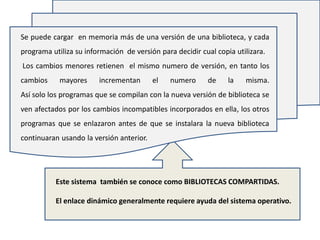

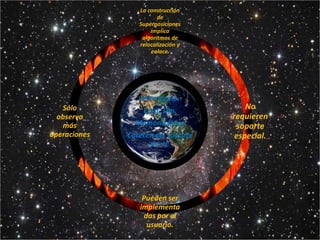

Este documento describe diferentes técnicas para la administración de la memoria en sistemas operativos, incluyendo la vinculación de direcciones, espacios de direcciones lógicas y físicas, carga dinámica, enlace dinámico y bibliotecas compartidas, superposiciones, intercambio y asignación de memoria contigua. Explica conceptos como registro de relocalización, carga y enlace dinámico para mejorar la utilización de la memoria.