Este documento introduce Verilog y el entorno de diseño XILINX para realizar prácticas de laboratorio sobre diseño de sistemas digitales. Los objetivos son familiarizarse con Verilog, conocer el entorno de diseño XILINX y desarrollar el proceso de diseño y simulación. Se describen dos circuitos, un decodificador 4 a 16 y un contador de 4 bits, para ser simulados. También se explican los pasos para crear un proyecto en XILINX, añadir los ficheros Verilog, y simular y verificar los diseños.

![Estructura de Computadores 3

A3 A2 A1 A0 W15W14W13W12W11W10W9W8W7W6W5W4W3W2W1W0

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1

0 0 0 1 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 0

0 0 1 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 0 0

0 0 1 1 0 0 0 0 0 0 0 0 0 0 0 0 1 0 0 0

0 1 0 0 0 0 0 0 0 0 0 0 0 0 0 1 0 0 0 0

0 1 0 1 0 0 0 0 0 0 0 0 0 0 1 0 0 0 0 0

0 1 1 0 0 0 0 0 0 0 0 0 0 1 0 0 0 0 0 0

0 1 1 1 0 0 0 0 0 0 0 0 1 0 0 0 0 0 0 0

1 0 0 0 0 0 0 0 0 0 0 1 0 0 0 0 0 0 0 0

1 0 0 1 0 0 0 0 0 0 1 0 0 0 0 0 0 0 0 0

1 0 1 0 0 0 0 0 0 1 0 0 0 0 0 0 0 0 0 0

1 0 1 1 0 0 0 0 1 0 0 0 0 0 0 0 0 0 0 0

1 1 0 0 0 0 0 1 0 0 0 0 0 0 0 0 0 0 0 0

1 1 0 1 0 0 1 0 0 0 0 0 0 0 0 0 0 0 0 0

1 1 1 0 0 1 0 0 0 0 0 0 0 0 0 0 0 0 0 0

1 1 1 1 1 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

Tabla 2: Tabla de verdad del codificador 4 a 16.

Para diseñar el código Verilog se ha usado una descripción procedimental, que es la que se muestra

en el fragmento de código 1 (fichero decodificador.v). Estudie dicha descripción hasta que tenga claro su

funcionamiento.

module dec4a16(

input [3:0] a,

output reg [15:0] w

);

always @ (a)

begin

w = 0;

w[a] = 1;

end

endmodule

Código 1. Fichero decodificador.v

2.2. Diseño del contador de 4 bits

Dicho contador está disparado por el flanco de subida del reloj, tiene una señal RESET síncrona de

puesta a cero. Además, incluye una señal carry (CY) que se activa cuando el contador llega al último

estado de cuenta.

El contador debe cumplir la tabla comportamiento de la figura 1b y, el código Verilog propuesto para

describirlo es el fragmento de código 2 (fichero contador.v). Debe estudiarlo hasta entender su

funcionamiento.](https://image.slidesharecdn.com/xilinxaprenderabrirlo-150612131609-lva1-app6891/85/Xilinx-aprender-abrirlo-3-320.jpg)

![Estructura de Computadores 4

CLK RESET UP CONT ←←←←

1 X CONT ← 0

0 1 CONT ← CONT+1

0 0 CONT ← CONT

CY = Si se cumple que...

0 [CONT] ≠ 1111

1 [CONT] = 1111

(a) (b)

Figura 1. Descripción del contador módulo 16: (a) Descripción estructural, (b) Descripción funcional.

module contador_mod_16(

input clk, up, reset,

output reg [3:0] q,

output cy

);

assign cy = &q;

always @(posedge clk)

if (reset==1 )

q <= 0;

else if (up==1)

q <= q + 1;

endmodule

Código 2. Fichero contador.v

3. Estudio experimental

En esta sesión de laboratorio se va a realizar la simulación del sistema digital diseñado con el

paquete de herramientas de Xilinx ISE. Se utilizarán unos ficheros con módulos verilog tanto de

circuitos como de testbench previamente preparados. Los pasos a seguir son los siguientes:

1. Siga los pasos del “Tutorial de uso de Xilinx ISE” (incluido en la siguiente sección de este

documento), para crear un nuevo proyecto de nombre PracticaEdC1 (por ejemplo),

incluyendo todos los ficheros Verilog de la tabla 1.

2. Realice la simulación del decodificador 4 a 16 (fichero decodificador.v) siguiendo los pasos

descritos en el “Tutorial de uso de Xilinx ISE”, con ayuda del testbench facilitado (fichero

decodificador_tb.v). Compruebe si el decodificador funciona correctamente.

3. Realice ahora la simulación del contador de 4 bits (contador.v), con ayuda del testbench

facilitado (fichero contador_tb.v). Compruebe si el contador funciona correctamente.

4. Fíjese que al simular el contador no aparecen todos los estados ni la activación de la señal

de Carry. Haga los cambios oportunos en el testbench del contador para poder visualizar al

CLK q2

CY

q1 q0

CONT MOD 16RESET

UP

q3](https://image.slidesharecdn.com/xilinxaprenderabrirlo-150612131609-lva1-app6891/85/Xilinx-aprender-abrirlo-4-320.jpg)

![Estructura de Computadores 5

menos un ciclo completo de cuenta y vuelva a realizar la simulación para comprobarlo.

5. Añada una descripción estructural en Verilog que interconecte ambos bloques: contador y

decodificador, de forma que ambos aparezcan incluidos por este nuevo fichero. Utilice como

plantilla el fragmento de código 3 (fichero lab1.v).

6. Realice por último la simulación de este nuevo módulo (fichero lab1.v), con ayuda del

testbench facilitado (fichero lab1_tb.v). Compruebe si el sistema completo funciona

correctamente.

// El modulo lab1 esta formado por la interconexion estructural

// de los modulos contador_mod_16 y dec4a16.

// Simplificando un poco, la idea es conectar la salida

// del contador con la entrada del decodificador.

module lab1(

input clk, up, reset,

output [15:0] z,

output cy);

wire [3:0] de_cont_a_dec; // necesitara el cable para unir los componentes

// Rellene los huecos para conectar correctamente las entradas del contador

// a las entradas del modulo lab1 y las salidas del contador a las entradas

// del decodificador o a las salidas del lab1, según corresponda.

contador_mod_16 instancia_contador(

.clk( ),

.up( ),

.reset( ),

.q( ),

.cy( )

);

// Rellene los huecos para conectar correctamente la entrada del decodificador

// a la salida del contador y la salida del decodificador a la salida del lab1.

dec4a16 instancia_decodificador(

.a( ),

.w( )

);

endmodule

Código 3. Fichero lab1.v

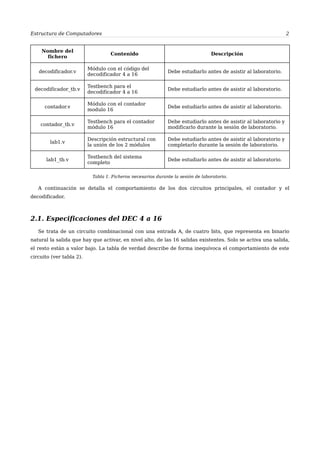

4. Tutorial de uso de Xilinx ISE

Esta sección describe el entorno ISE del fabricante XILINX. Este entorno, entre otras características,

incluye un simulador para el lenguaje Verilog que será utilizado en esta sesión de laboratorio.

4.1. Creación de un proyecto en Xilinx ISE

Tras iniciarse el sistema operativo, el primer paso es arrancar el entorno ISE y crear un nuevo

proyecto. En el menú File hay que utilizar la opción New Project, obteniéndose la ventana mostrada en

la figura 2 donde hay que escribir un nombre para el proyecto, por ejemplo PracticaEdC1. La

herramienta creará una carpeta con ese mismo nombre y guardará en su interior todo lo que se va gene-

rando a medida que vamos trabajando en ese proyecto.](https://image.slidesharecdn.com/xilinxaprenderabrirlo-150612131609-lva1-app6891/85/Xilinx-aprender-abrirlo-5-320.jpg)