Gestión de memoria dinámica

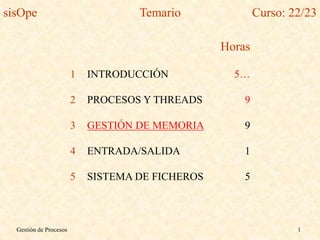

- 1. Gestión de Procesos 1 Horas 1 INTRODUCCIÓN 5… 2 PROCESOS Y THREADS 9 3 GESTIÓN DE MEMORIA 9 4 ENTRADA/SALIDA 1 5 SISTEMA DE FICHEROS 5 sisOpe Temario Curso: 22/23

- 2. Gestión de Memoria 2 Tema 3. Gestión de Memoria • INTRODUCCIÓN • SIN INTERCAMBIO NI MEMORIA VIRTUAL (Estático) • Monoprogramación • Multiprogramación con Particiones Fijas • INTERCAMBIO • Introducción • Particiones Variables • Algoritmos de gestión Libre / Ocupado – Lista encadenada y Mapa de bits • MEMORIA VIRTUAL • Paginación • Algoritmos de sustitución de páginas • Cuestiones de diseño

- 3. Gestión de Memoria 3 Introducción Cada vez, más memoria, más barata y ocupa menos: 1982 16KB 16.000 pts. PseudoPC 1985 1MB 500.000 pts. Victory (Unix) PC 1991 8MB 77.500 pts. 1998 64MB 17.900 pts. 128MB 51.900 pts. 2005 512MB 57 €. 1GB 180 €. 2013 4GB 48 €. 8GB 92 €. Sin embargo, ¡ SIEMPRE AMPLIANDO ! 512K, 640K, 1M, 4M, 8M, 16M, 32M, 64M, 128M MSDOS Win95 WinNT Win00 70MB 120MB 275MB Ley de Parkinson 2GB + 20GB ¡ Estable ! 1982 1995 1993 2000 ¿Windows 764? 2009 58€ MB

- 4. Gestión de Memoria 4 Introducción (objetivos) Memoria: Recurso escaso y compartido (Multiprogramación) Poca memoria para los muchos procesos que quieren ejecutarse • Proteger • Compartir • Organización eficiente • Reubicación de procesos Memoria Principal P1 P2 P3 P6 P5 P4 OBJETIVOS Gestión eficiente Secundaria Principal Caché segmentada lineal ?

- 5. Gestión de Memoria 5 Introducción (objetivos) Jerarquía de Memoria: Capacidad y Tiempos 6ª Ed Computer Architecture … Hennessy & Patterson - 2019 %vecesQueAparece 33 800000 14,292 segundos %vecesQueAparece 33 1600000 41,579 segundos ? ?

- 6. Gestión de Memoria 6 Introducción (¿Proceso en memoria?) Programa Objeto n Programa Objeto 2 Compilador Programa Objeto 1 Enlazador Fichero Ejecutable Cargador Memoria Programa Fuente 1 Program principal; var Vector1: array [0..$FFF] of byte := (23,43,…,53); Vector2: array [0..$4FF] of byte; begin ... if Vector1[0] = Vector2[0] then Subrutina; ... end. $5000 … $5030 cmp $9000,$A000 $5036 bnz $503E $503A bsr $5200 $503E … $5200 (codigo de subrutina) … $9000 (valores de vector1) … $A000 (valores de vector2) … Proceso Código máquina ¿ ?

- 7. Gestión de Memoria 7 Introducción (¿Formato de un fichero ejecutable?) Nº mágico CP inicial --------- Tabla secciones Código máquina Variables inicializadas ..... Otras secciones Tabla símbolos (depurador) $0000 $1000 $5000 $8000 • Fichero ejecutable UNIX Secciones Cabecera #file miabuelo miabuelo: MINIX-PC 32-bit executable $file barreraArbol barreraArbol: ELF 64-bit LSB executable, x86-64 CP inicial

- 8. Gestión de Memoria 8 Introducción (¿Formato de un fichero ejecutable?) Código Var. Inic. Var. No Inic. --------------- Tabla Símbolos Inicio Tamaño $1000 $5000 $8000 ------- $4000 $1000 $500 ------- $2000 Nº mágico CP inicial --------- Tabla secciones Código máquina Variables inicializadas ..... Otras secciones Tabla símbolos (depurador) $0000 $1000 $5000 $8000 • Fichero ejecutable UNIX Var. No Inic. ¡ Algunas secciones no ocupan espacio en el fichero ejecutable y sí en memoria ! Secciones Cabecera #file miabuelo miabuelo: MINIX-PC 32-bit executable $file barreraArbol barreraArbol: ELF 64-bit LSB executable, x86-64 5 int b = 5; int a; globales

- 9. Gestión de Memoria 9 Introducción (¿Imagen de un proceso en memoria?) Nº mágico CP inicial --------- Tabla secciones Código máquina Variables inicializadas ..... Otras secciones Tabla símbolos (depurador) $0000 $1000 $5000 $8000 • Fichero ejecutable UNIX Código máquina Variables inicializadas Variables no inicializadas Memo. Dinámica Pila $5000 $0000 $4000 $5500 • Imagen de un proceso $xxxx “0” $0000 Memoria S.O. P1 P2 P4 ? $yyyy Pn pc sp ... ... ... CPU P1 sp ... ... ... P4 sp ... ... ... Pn sp ... ... ...

- 10. Gestión de Memoria 10 M.P. Introducción (modelo estático vs dinámico) Pi exec Pi se ejecuta en la misma zona de memoria desde que se crea hasta que termina M.P. Pi exec exit Pi Pi Pi exit Pi puede ir cambiando en su totalidad de zona de memoria Intercambio M.P. Pi puede ir cambiando por trozos de zona de memoria Memoria Virtual ¡ Reubicar !

- 11. Gestión de Memoria 11 • Máquina con S.O. (MSDOS) IPL + drivers FFFFF 00000 ROM RAM Monitor “Primeras máquinas” Monoprogramación • Máquina desnuda con monitor Cargar y depurar programas Programa de usuario + drivers “Sistemas empotrados” S.O. Power Point Excel Word Word S.O. + drivers RAM ? Word S.O. + drivers RAM ROM ? “Prácticas de arquitectura” RS232

- 12. Gestión de Memoria 12 Estático “En arranque” Multiprogramación ( Particiones Fijas ) Se trocea la M.P. libre para procesos de usuario en particiones fijas, de diversos tamaños y reconfigurable sólo en arranque S.O. 300K 300K 200K 100K 115K ? 320K S.O. 600K 250K 50K CUESTIONES DE DISEÑO • ¿Cuántas particiones? • ¿De qué tamaño? • Reubicación • Protección • ¿Planificación? • Tabla de particiones Tamaño y Libre / Ocupada • Cola/s de procesos entrantes

- 13. Gestión de Memoria 13 Particiones Fijas ( ¿Cuántas particiones? ) Aprovechar UCP Índice / Nivel de multiprogramación % de uso de la UCP Nivel de Multipro- gramación 1 2 3 4 5 6 7 8 9 10 100 80 60 40 20 50% de su tiempo hacen E/S ¿Caracterización de los procesos? 80% de su tiempo hacen E/S 20% de su tiempo hacen E/S ¡ Ojo ! Aprovechar la UCP al 100% no es el único objetivo Usuarios interactivos ¿ProbLibre? 0,5 * 0,5 = 0,25 ?

- 14. Gestión de Memoria 14 Particiones Fijas ( ¿De qué tamaño? ) Intentar aprovechar la memoria al máximo (ocupada al 100% por Pi) • GRANDES S.O. 300K 300K 50K Fragmentación interna 40K 200K P200K no puede ejecutarse pese a haber 510K sin usar • PEQUEÑAS S.O. 250K 50K 50K 40K 200K 60K P60K no puede ejecutarse pese a haber 5 particiones libres Fragmentación externa

- 15. Gestión de Memoria 15 Particiones Fijas ( Planificación ) • COLAS MÚLTIPLES / SEPARADAS S.O. 200K 400K 300K 100K 350K 80K Entra un Proceso Cola de la partición “Mejor Ajuste” A 250 B 70 C 80 D 150 E 90 F 125 Sale un Proceso P100K ¿Quién entra? • FIFO B • Más grande E • Más corto C 110 5 15 Tiempos Se libera P400K Partición grande libre y 6 procesos bloqueados ¿Particiones de igual tamaño? Equilibrar la carga

- 16. Gestión de Memoria 16 Particiones Fijas ( Planificación ) • COLA ÚNICA S.O. 200K 400K 300K 100K Entra un Proceso Partición para él o Se encola A 250 Sale un Proceso P200K ¿Quién entra? B 70 C 80 D 150 F 90 E 125 4 110 25 5 15 3 • FIFO B • Más grande D • Más corto F Tiempos • Más complejo y lento • Mejor aprovechamiento de UCP y memoria • Puede que injusticia: grandes vs pequeños

- 17. Gestión de Memoria 17 Particiones Fijas ( Reubicación ) S.O. A 250 128K 512K 256K 100K Programa Partición ¡No siempre la misma! IF V >= 0 THEN V := V-1 ELSE V := V+1 ¿Direcciones Absolutas? TST R0 JMI ELSE SUB #1,R0 JMP NEXT ELSE ADD #1,R0 NEXT 00000 00050 TST R0 00052 JMI 00060 00058 SUB #1,R0 0005A JMP 00062 00060 ADD #1,R0 00062 ? Problemas

- 18. Gestión de Memoria 18 Particiones Fijas ( Reubicación ) S.O. 20000 20050 TST R0 20052 JMI 00060 20058 SUB #1,R0 2005A JMP 00062 20060 ADD #1,R0 20062 ? a) Reubicar al cargar (reubicación estática) +20000 Direcciones Absolutas Dirección de carga 20060 20062 b) Reubicación dinámica Registro de Reubicación 20000 00060 dv + 20060 dr c) Código reubicable JMI 8(PC) SOLUCIONES

- 19. Gestión de Memoria 19 Particiones Fijas ( Protección ) S.O. 20000 20050 TST R0 20052 JMI 00060 20058 SUB #1,R0 2005A JMP 00062 20060 ADD #1,R0 20062 ........... 5FC00 • Controlar accesos de Pi fuera de su zona 20000 5FC00 00060 dv + 20060 dr Registro de Reubicación (Registro Base) No direccionable? SI dr>RL Excepción rpAux = rpAux->p_nextready

- 20. Gestión de Memoria 20 Intercambio ( Introducción ) Dos grandes problemas de las particiones fijas sin intercambio: A Muchos procesos interactivos y poca memoria para ellos B ¿Cómo gestionar la memoria dinámica de los procesos? 20 usuarios desean usar editor 1MB S.O. 16 particiones de 1MB Máximo 16 procesos 4 try later ¿Una solución? ? Ampliar la M.P. con más particiones en disco S.O. P1 P2 P16 P17 P18 P19 P20 P1 P19 ¡ Eficiente si no hay trasiego !

- 21. hdparm –tT /dev/sda1 128MB/s Gestión de Memoria 21 Intercambio ( Introducción ) • ¿ Cuándo intercambiar ? S.O. P2 P16 P17 P18 P20 P1 P19 ? Algunas cuestiones: • ¿ Quién por quién ? • ¿ Coste del intercambio ? Word Excel ¡ (20 + 30) MB … ! Pi.sleep Pi.read Cada x segundos Cerca saturación ¡Ojo E/S!

- 22. Gestión de Memoria 22 Intercambio ( Introducción => ¿ COSTE ? ) Word Excel ¡ (20 + 30) MB … !

- 23. Gestión de Memoria 23 Intercambio ( Introducción ) Dos grandes problemas de las particiones fijas sin intercambio: A Muchos procesos interactivos y poca memoria para ellos B ¿Cómo gestionar la memoria dinámica de los procesos? S.O. 300K 200K 100K P1 300 ¿Por qué P1 pide 300K? 300 250 200 150 100 ti tf K Particiones Fijas Partición de 300K ¿ Intercambio ? P100K P200K P300K P100K ¿Qué estructura tiene la memoria dinámica de un Pi? -heap reserve, commit -stack reserve, commit

- 24. Gestión de Memoria 24 Intercambio ( Introducción ) Componentes de MP de un Pi • Código • Pila • Datos Fijo Varía (bsr y rts) Varía (new y dispose) Necesita 325K y le doy 400K (crecer) 200K (C) + 75K (D) + 50K (P) Pila Código Datos 25K 50K ? S.O. $00000 400K 50K 300K $FFFFF Pila Código Datos Pila Código Datos Pila Código Datos 200K 200K Dos zonas no contiguas ? Fragmentación Protección Reubicación

- 25. Gestión de Memoria 25 Particiones Variables • Asignar a cada proceso sólo la memoria que necesita S.O. 800 224 A300K A 300 500 B100K B 100 400 C200K C 200 200 A C 200 200 B 100 300 S.O. D150K D C 200 200 B 100 150 S.O. 150 E225K B D C 200 200 150 S.O. 250 D C S.O. E Fragmentación externa E esperando ¿ Solución ? blockdev –getbsz /dev/sda1 Pide 3333 bytes Le doy 4096 bytes

- 26. Gestión de Memoria 26 Particiones Variables (Compactación) • Siempre un único hueco con toda la memoria libre S.O. 800 224 A300K A 300 500 B100K B 100 400 C200K C 200 200 A C 200 200 B 100 300 S.O. D150K D C 200 350 B 100 150 S.O. E225K B E D C 200 225 B 100 150 S.O. 125 E D C S.O. 225 C 200 B 100 500 Compactar Compactar Costoso en tiempo ¿ Siempre ? ¿ De vez en cuando ? ¿ Cuándo ? Gestión de huecos

- 27. Gestión de Memoria 27 S.O. P1 P3 P5 P2 P4 Algoritmos de gestión trozos (Lista Encadenada) • Lista encadenada: distribuida vs centralizada Ordenada por direcciones y de cada trozo saber (al menos): Tipo (Libre/Ocupado); Tamaño P1 Ocupado 5MB Libre 6MB Libre 4MB ¿Separar en 2 listas? • Huecos • Procesos ¿Peligroso?

- 28. Gestión de Memoria 28 S.O. Algoritmos de gestión trozos (Lista Encadenada) P1 P3 P5 • Lista encadenada: distribuida vs centralizada 64MB 20 5 6 4 13 12 4 Ocupado $0050 0000 $0140 0000 dirTrozo Tipo Tamaño Sig P1 Libre $0060 0000 $0190 0000 Ocupado $0040 0000 $01F0 0000 Libre $00D0 0000 $0230 0000 Libre $0040 0000 $03C0 0000 Ocupado $00C0 0000 $0300 0000 P3 P5 • ¿Lista dinámica? => Array estático => ¿Tamaño? • La memoria se da a trozos (sean de 4KB) P 00500 01400 H 00600 01900 P 00400 01F00 H 00D00 02300 P 00C00 03000 H 00400 03C00 Clicks MINIX

- 29. Gestión de Memoria 29 S.O. Algoritmos de gestión trozos (Lista encadenada) 0 1000 49999 1000 H 49000 -1 D D D D D 0 1 2 3 4 N dirTrozo Tipo Tamaño Sig P1.12000 P1 1000 P 12000 1 13000 H 37000 -1 D D D D P2.8000 P2 1000 P 12000 1 13000 P 8000 2 21000 H 29000 -1 D D D P3.20000 P3 1000 P 12000 1 13000 P 8000 2 21000 P 20000 3 41000 H 9000 -1 D D P1 P4.7000

- 30. Gestión de Memoria 30 S.O. Algoritmos de gestión trozos (Lista encadenada) 0 1000 49999 1000 P 12000 1 13000 P 8000 2 21000 P 20000 3 41000 H 9000 -1 D D P1 P4.7000 dirTrozo Tipo Tamaño Sig P1 P2 P3 1000 H 12000 1 13000 P 8000 2 21000 P 20000 3 41000 H 9000 -1 D D 0 1 2 3 4 N 1000 P 7000 4 13000 P 8000 2 21000 P 20000 3 41000 H 9000 -1 8000 H 5000 1 D P4 0 mem

- 31. Gestión de Memoria 31 Algoritmos de gestión trozos (Liberación de Memoria) P1 P2 P3 • Lista encadenada: Supongamos que termina un proceso (sea P2) • Hay que tener en cuenta cuatro situaciones: P1 P3 P1 P2 P2 P3 P2 P1 P3 • ¡ Fusionar ! Ventaja de tener la lista ordenada (contigüidad) • Conveniencia de tener la lista doblemente enlazada

- 32. Gestión de Memoria 32 Algoritmos de gestión trozos (Asignación de Memoria) • Lista encadenada: Asignación de memoria 1. First Fit “Primero en donde quepa” 2. Next Fit “Siguiente donde quepa” 3. Best Fit “Donde quepa mejor” Muchos huecos inútiles (demasiado pequeños) 4. Worst Fit “Donde quepa peor” ¡ Recorrer toda la lista ! 5. Lista de procesos por un lado y de huecos por otro ¿ Cómo acelerar la asignación ? Liberación ineficiente Ya lo tenemos [descriptores de procesos] Ordenados por tamaño First = Best ¿Next? 6. Quick Fit “Donde quepa antes”

- 33. Gestión de Memoria 33 Algoritmos de gestión trozos (First Fit) • FIRST FIT “Primero en donde quepa” P P P P P P P’ P P P P P P P’ Muchos huecos pequeños al principio y uno grande al final: Ejemplo: [Fork(P20K)]8 + [Exit(P20K) + Fork(P18K)]8 + Fork(P15K) P P P P P P P P P P P P P P P P P’ P’ ¡ Siempre recorriendo el principio !

- 34. Gestión de Memoria 34 Algoritmos de gestión trozos (Next Fit) • NEXT FIT “Siguiente donde quepa” Ejemplo: [Fork(P20K)]8 + [Exit(P20K) + Fork(P18K)]8 + Fork(P15K) P Inicio de búsqueda del siguiente hueco P P P P P P P P P P P P P P P P P P P P P P P P P P P P P P P ¿Pi grande? ! Huecos dispersos de tamaño moderado ! Fragmentación externa

- 35. Gestión de Memoria 35 Algoritmos de gestión trozos (Quick Fit) • QUICK FIT “Donde quepa antes” Idea: Varias listas que agrupan bloques de tamaño similar 64K 128K 256K 512K 1M 2M 4M Enormes 16 32 40 52 65 112 280 300 360 360 400 800 3 3,5 3,8 32 P310 P220 P500 P900 ¡ Todavía puede mejorarse tanto la asignación como la liberación ! Sistema Buddy (Compañeros) 100 1101 1000 0000 0000

- 36. Gestión de Memoria 36 S.O. • ¡Doy memoria a trozos! 64MB 00000000 -------- 11111111 11111111 11111111 -------- Algoritmos de gestión trozos (Mapa de Bits) Asignación a golpe de 4K (granularidad) Pi pide 10K Fragmentación Interna • ¿Tamaño del Mapa de Bits? 64MB/4KB = 16Kbits => 2KB • ¿Liberación de memoria? • ¿Asignación de memoria? ListaEncade ? First, Next, Best, Worst => Viables Quick, Buddy => Inviables ¡ No hay información explícita de tamaños ! 00000000 -------- 00011111 11111111 11111111 -------- Se le dan 12K (3 trozos) Pi Pj 00000000 -------- 00011111 00000000 11000111 -------- Pk 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 000....00 ocupado libre 0 0 0 0 0 0 0 0 0 0 0 0 0 0 Mbits = 64KB LEnc = 2,75KB • 1er click • numClicks descriptor

- 37. Gestión de Memoria 37 Paginación • PROBLEMÁTICA DEL INTERCAMBIO • ARQUITECTURA SUBYACENTE • TRADUCCIÓN DE DIRECCIONES • TABLA DE PÁGINAS MULTINIVEL • UNO O VARIOS ESPACIOS DE D.V. • TRATAMIENTO DE FALTA DE PÁGINA

- 38. Gestión de Memoria 38 ? M.P. Paginación ( Problemática del Intercambio ) ¿Su gran restricción? Exigir que un Pi esté entero en M.P. para poder ejecutarse A Un Pi más grande que la M.P. no podrá ejecutarse B Si {Procesos preparados} aumenta, no cabe en M.P. Trasiego C El intercambio Disco M.P. es mucho (dos procesos enteros) Compilador: 1 Análisis léxico 2 Análisis sintáctico 3 Análisis semántico 4 Generación de código ¿Solución general? Overlays (solapamientos) Trocear

- 39. Gestión de Memoria 39 M.P. Paginación ( Problemática del Intercambio ) Solución Darle al usuario la sensación de tener una M.P. enorme • El i7 9700 (48/64bits de direcciones) 256TB • Un PC medio dispone tan sólo de 16GB 16.384 veces menos M.P. Espacio de dir. del i7 Espacio de Direcciones Reales del PC • Teóricamente podemos escribir programas pensando en el i7 y 256TB ¿ Cómo funciona todo esto ? Arquitectura subyacente M.V. M.P. • Tendremos una Memoria Virtual de 256TB y mis programas se ejecutan aunque tenga menos Memoria Principal (16GB) siempre que quepan en la memoria virtual.

- 40. Gestión de Memoria 40 MEMORIA VIRTUAL Paginación ( Arquitectura Subyacente ) CPU dv Bus Datos M.V. La Memoria Virtual reside físicamente en memoria secundaria M.P. ¡ No caben ! • Principio de localidad: Meto en M.P. los trozos que hagan falta para ejecutar Pr y Pv

- 41. Gestión de Memoria 41 Paginación ( Arquitectura Subyacente ) CPU dv Bus Datos M.V. M.P. • La M.V. se divide en páginas (1000B?) 0 1 2 3 5 6 7 8 9 • La M.P. se divide en marcos 0 2 8 MMU fallo 9 S.O. ? 6 dr Traducir dvdr ¿Cachés? 0 1 2 3 4 5 6 7

- 42. Gestión de Memoria 42 Paginación ( Arquitectura Subyacente ) Resumiendo: • M.V. en disco y gestionado como un sistema de particiones variables (los trozos “granularidad” de M.V. son páginas) • Las páginas de M.V. necesarias para que se ejecute un Pi están en la M.P. en uno cualquiera de sus marcos ¡ Principio de localidad espacial y temporal ! • Función de traducción (dv dr) implementada en Hw ¡ MMU interna vs externa ! • Las páginas se intercambian MV MP (Falta de Página) gracias a la intervención del S.O. ¿ Cómo hacer la traducción dv dr ?

- 43. Gestión de Memoria 43 Paginación ( Traducción de direcciones ) M.V. M.P. 0 1 2 3 5 6 7 8 9 0 2 8 9 6 F.T. ? ¿ Qué páginas están cargadas y dónde ? ¡ Tabla de Páginas ! 0 1 2 3 4 5 6 7

- 44. Gestión de Memoria 44 Paginación ( Traducción de direcciones “decimal” ) ¿ # páginas ? ¿ # marcos ? 4096 256 M.V. de 16MB M.P. de 1MB Páginas de 4KB M.P. 0 4095 4096 8191 0 1 2 8192 12287 255 M.V. 0 4095 4096 8191 0 1 2 8192 12287 4095 MMU Página 2 en Marco 1 (4096) 8192 4096 12287 8191 11285 11285 4096 2 3093 + 7189 7189 4096 1

- 45. Gestión de Memoria 45 Paginación ( Traducción de direcciones “decimal” ) ¿ # páginas ? ¿ # marcos ? 4096 256 M.V. de 16MB M.P. de 1MB Páginas de 4KB MMU dv dr TamPag pag off marco TamPag + / * dv dr ? ¡ Veamos un ejemplo !

- 46. Gestión de Memoria 46 Paginación ( Traducción de direcciones “decimal” ) • TamPag = 1024 • MV = 8 páginas • MP = 4 marcos 3 1 * * 2 * 0 * Pag marco 0 1 2 3 4 5 6 7 • ¿Lista de dv que provocarán Falta de Página? [ 1ª dirección página 2 .. Última dirección página 3 ] 2 * 1024 = 2048 4 * 1024 - 1 = 4095 [ 2048 .. 4095 ] [ 5120 .. 6143 ] [ 7168 .. 8191 ] 0 0 3 656 Pag Off Mar Off 3 0 • Calcular direcciones reales dv 0 3728 4609 1023 1024 1025 7800 4096 dr 3072 FP 4 513 4609 / 1024 = 4 : 513 2 513 2 * 1024 = 2048 2561 + 2561 0 1023 1 0 1 1 7 632 4 0 3 1023 1 0 1 1 2 0 FP 4095 1024 1025 2048

- 47. Gestión de Memoria 47 Paginación ( Traducción de direcciones “binario” ) ¿ # bits dv ? ¿ # bits dr ? 24 20 M.V. de 16MB M.P. de 1MB Páginas de 4KB 0000 0000 0000 0000 0000 0000 0000 0000 0000 1111 1111 1111 0000 0000 0001 0000 0000 0000 0000 0000 0001 1111 1111 1111 0000 0000 0010 0000 0000 0000 0000 0000 0010 1111 1111 1111 M.V. 0 4095 4096 8191 8192 12287 12 bits Página Offset 12 12 dv M.P. 0 4095 4096 8191 8192 12287 0000 0000 0000 0000 0000 0000 0000 1111 1111 1111 0000 0001 1111 1111 1111 0000 0010 0000 0000 0000 0000 0010 1111 1111 1111 Marco Offset 8 12 dr 8192 12287 4096 8191 0000 0001 0000 0000 0000 HH HHH 2 3 HHH HHH 3 3 “hexadecimal” 11285 0000 0000 0010 1100 0001 0101 7189 0000 0001 1100 0001 0101

- 48. Gestión de Memoria 48 Paginación ( Traducción de direcciones “hexadecimal” ) M.V. 0 1 2 3 5 6 7 8 9 000 000 000 FFF HHH HHH PAG OFF 008 000 008 FFF FFF 000 FFF FFF M.P. 0 2 8 9 6 00 000 00 FFF HH HHH MAR OFF 02 000 02 FFF FF 000 FF FFF 0 1 2 3 4 5 6 7 8 9 A FFF Tabla de páginas 02 51A P 02 Presente Marco 008 51A ¿Dónde está?

- 49. Gestión de Memoria 49 • Toda la T.P. en M.P. M.P. Tabla de Páginas MMU CPU Paginación ( Ubicación de la Tabla de Páginas ) dato dv Se lee el descriptor dr Se lee el dato ¡ Intolerable por lento ! • Toda la T.P. en la M.M.U. M.P. T.P. CPU MMU dato dv dr • PDP11 8 páginas de 8K • ¿Viable en el 80486? 1M páginas 4K ¡ Intolerable por caro !

- 50. Gestión de Memoria 50 • Toda la T.P. en M.P. + una caché de la T.P. en la MMU Paginación ( Tabla de Páginas “M.P. + caché TLB” ) M.P. Tabla de Páginas dato 008 51A dv MMU 009 FF 006 63 000 40 008 52 002 A3 TLBcaché Página Marco Cachés de 8..2048 entradas 1M entradas 52 51A dr RBTP ¿ Fallo de TLBCaché ? ¡ Tasas de acierto del 98% !

- 51. Gestión de Memoria 51 Paginación ( Traducción de direcciones “descriptor” ) • Aspecto de un descriptor de página P B R M L E J MARCO PRESENTE Permisos: LECTURA BLOQUEADA ESCRITURA REFERENCIADA EJECUCIÓN MODIFICADA CACHE (Si/No) ¿ Dirección en disco ? • Un disco entero, o varios, o una parte de uno, para la M.V. • Un fichero especial “pagefile.sys” innecesario C

- 52. Gestión de Memoria 52 Paginación ( Tabla de Páginas “multinivel” ) Intel Core i7 => DV 48 bits, páginas 4KB y descriptores 4B => 256GB para la TP RegTP1 ¡Siempre en MP! Entran y salen de MP TP Nivel1 TP Nivel2 páginas VPN1 VPN2 OFF R PPN OFF dirVirtual dirReal Ejercicio 2 – 12.12.2001 ¿ Y si no cabe ?

- 53. Gestión de Memoria 53 Paginación ( Tabla de Páginas “multinivel” Intel Core i7 ) VPN 1 VPN 2 VPN 3 VPN 4 VP OFF 9 9 9 9 12 CR3 40 9 9 40 9 40 9 40 PPN [MARCO] PP OFF 12 Page global directory Page upper directory Page middle directory Page table dirVirtual dirFísica i3 10ª 64GB i5,i7 10ª 128GB Xeon 1..4,5TB 2019

- 54. Gestión de Memoria 54 Paginación ( Tabla de Páginas “multinivel” ) Intel 80386 => DV 32 bits, páginas 4KB y descriptores 4B => 4MB para la TP MINIX3 1986

- 55. Gestión de Memoria 55 P0 P1 P2 P3 P4 P5 P6 P7 P8 P9 P10 P11 P12 P13 P14 P15 M.V. FT M4 M5 M6 M7 M.P. M0 M1 M2 M3 Paginación ( Uno o varios espacios de dv ) • Un único espacio de direcciones virtuales para todos los procesos P1 P2 P3 • Una única T.P. Global • Reubicación: Carga Registro Reubicación • ¿ Cómo crece un Pi ? Muy problemático • Se adapta bien a tener un disco con n*sector = página Eficiencia Ver ejercicio 3 20/6/00

- 56. Gestión de Memoria 56 Paginación ( Uno o varios espacios de dv ) • Un espacio de direcciones virtuales para cada proceso P0 P1 P2 P3 M.V.(P1) FT(P1) P0 P1 P2 P3 P1 M4 M5 M6 M7 M.P. M0 M1 M2 M3 P0 P1 P2 P3 P4 P5 P2 • En la MMU, las dv se prefijan por un identificador de proceso (complejidad) • Una T.P. por proceso • Reubicación innecesaria • ¿ Fácil crecer ? • Se adapta bien a tener un fichero por Pi (ineficiente)

- 57. Gestión de Memoria 57 Paginación ( Tratamiento de Falta de Página ) • ¿Cuántas Faltas de Página puede generar una instrucción? 1. Extraer instrucción Leer dv $003000 F.P. 2. Decodificarla 3. Ejecutarla Escribir dv $0045FB F.P. ? move D0,$0045FB clr $0003FA M.V. $002FFA CPU PC M.P. Una instrucción, 0, 1, 2 o más F.P. $003000

- 58. Gestión de Memoria 58 Paginación ( Tratamiento de Falta de Página ) • El tratamiento de F.P. recae en el S.O. M.P. 0 2 8 9 6 (I) Hay marco libre M.V. 0 1 2 3 5 6 7 8 9 ? Política de ubicación simple: uno cualquiera (II) No hay marco libre M.P. 0 2 8 9 6 3 5 1 ? ? Política de sustitución no tan simple ¡ 1.048.576 marcos !

- 59. Gestión de Memoria 59 S.O. M.V. 0 1 2 3 5 6 7 8 9 mov C,D M.P. 0 2 8 6 0 1 2 3 4 5 6 7 3 5 7 1 M Marco P Paginación ( Tratamiento de Falta de Página “II” ) 3 Seleccionar víctima, tocar TP y arrancar E/S ¡ Sólo si sucia ! 2 5 1 0 0 0000 3 ¿Víctima 2 ? 1 1 5 0FA3 2 4 0FA3 4 Salvando (DMA) página sucia en disco 5 Fin E/S. Página 2 salvada. Marco 5 libre. 7 mov C,D 9 mov C,D 6 8 9 0 1 0 5 10 ¿ Quién actualiza la TLBcaché ?

- 60. Gestión de Memoria 60 Paginación ( Tratamiento de Falta de Página “II” ) Resumiendo: 1 Referencia a página no cargada en M.P. 2 Excepción BERR y se bloquea al proceso 3 Seleccionar víctima, tocar TP y arrancar E/S ¡ Sólo si sucia ! 4 Salvando (DMA) página sucia en disco. CPU para otro Pi 5 Fin E/S. Página 2 salvada.Marco 5 libre. 6 Arrancar E/S para cargar Página 9 en Marco 5. 7 Transferencia DMA discoMP. CPU para otro Pi 8 Fin E/S. Página 9 cargada en Marco 5. P Preparado 9 Actualizar TP 10 Rearrancar “Mov C,D” cuando preparado UCP ¿O continuar? 37 millones Inst

- 61. Gestión de Memoria 61 Paginación ( Algoritmos de sustitución de páginas ) OBJETIVO: Minimizar el número de Faltas de Página (F.P.) Accesos:{ ........ $001000, $0043FA, $001002, $006400, $001006, $006402, $006406, $006408, $001008, $00640A, $00100A, $00100E, $00640E, $001012 ..} { .. 1, 4, 1, 6, 1, 6, 1, 6, 1, 6, 1, ..} Serie de Referencia Un solo marco ? F.P. 11 3 o más marcos ? F.P. 3 ¿Cuantos más marcos mejor? Sean dos marcos M0 M1 1 1 4 1 6 F.P. 3 M0 M1 1 1 4 6 4 6 1 4 M0 M1 1 1 4 6 4 1 4 6 4 1 4 6 4 1 4 6 4 1 4 10 Margen para la mejora Algoritmos M0 M1 M0 M1

- 62. Gestión de Memoria 62 Paginación ( Algoritmos de sustitución de páginas ) {7,0,1,2,0,3,0,4,2,3,0,3,2,1,2,0,1,7,0,1} Serie de Referencia ALGORITMOS IDEAL Más tiempo tarde en volver a ser referenciada NRU No utilizada recientemente FIFO Más tiempo lleva en Memoria Principal LRU Menos recientemente usada 2nd Chance Segunda oportunidad RELOJ FIFO + LRU ¡ El mismo !

- 63. Gestión de Memoria 63 Paginación ( Algoritmos de sustitución de páginas ) 7,0,1,2,0,3,0,4,2,3,0,3,2,1,2,0,1,7,0,1 IDEAL FP 7 2 3 4 0 1 7 9 ● 0 1 ● ● ● ● ¿ Implementable ?

- 64. Gestión de Memoria 64 Paginación ( Algoritmos de sustitución de páginas ) 7,0,1,2,0,3,0,4,2,3,0,3,2,1,2,0,1,7,0,1 IDEAL FIFO FP 7 0 1 2 3 4 0 1 7 9 2 3 0 4 0 1 7 15 2 3 2 0 1 7 0 1 ● ● ● ● ● ● ? sigMarco 0 ++ mod numMarcos R0 R1 V0 V1 R2 V2 R3 R4 sigM ¡ FALLA ! V.exit R0 R1 R2 R3 R4 sigM N1,N0,R5 R0 R1 R5 N0 R2 N1 R3 R4 sigM ? R0 R1 R2 R3 R4 R5 N0 N1 cab cola array circular

- 65. Gestión de Memoria 65 Paginación ( Algoritmos de sustitución de páginas ) 7,0,1,2,0,3,0,4,2,3,0,3,2,1,2,0,1,7,0,1 IDEAL FIFO FP 7 0 1 2 3 4 0 1 7 9 2 3 0 4 0 1 7 15 2 3 2 0 1 7 0 1 9 3 0 4 2 3 1 1 2 0 3 marcos Anomalía de Belady 3 2 1 0 3 2 4 3 2 1 0 4 4 marcos 10 3 4 0 2 3 4 1 2 0 1

- 66. Gestión de Memoria 66 Paginación ( Algoritmos de sustitución de páginas ) 7,0,1,2,0,3,0,4,2,3,0,3,2,1,2,0,1,7,0,1 FIFO LRU FP 7 0 1 2 3 4 0 1 7 15 0 2 3 2 0 1 2 3 4 0 1 7 12 2 3 0 7 0 1 ● ● ● ● ● • Hw => Marca de tiempo en el descriptor de página “ultRef” 2557600 numCiclos 1GHz MMU TLBcaché 13A 2B 2530208 01C 30 1980513 2F4 8D 2500400 Pag ultRef marco 01C 51A dv 2557600 • ¿Falta de página? • Flush TLBcaché • Buscar víctima • ¿Desbordamiento? 32 bits 4 segundos

- 67. Gestión de Memoria 67 Paginación ( Algoritmos de sustitución de páginas ) 7,0,1,2,0,3,0,4,2,3,0,3,2,1,2,0,1,7,0,1 LRU FP 2 3 4 0 1 7 12 2 3 0 7 0 1 • Sw + Hw => Bit R + IntPeriódica (contador) t contador ++ 0 1 2 3 4 5 6 7 • ¿IntPeriódica? 8 Todas las páginas referenciadas aquí a 8 • Flush TLBcaché • Reset bits R en TLB • contador++ • Para toda página R==1 ultRef = contador R = 0 • ¿Falta de página? • Flush TLBcaché • Reset bits R en TLB • Buscar víctima actualizando R y ultRef ¡ LENTO !

- 68. Gestión de Memoria 68 Paginación ( Algoritmos de sustitución de páginas ) 7,0,1,2,0,3,0,4,2,3,0,3,2,1,2,0,1,7,0,1 IDEAL FIFO LRU RELOJ FP 7 0 1 2 3 4 0 1 7 9 7 0 1 2 3 4 0 1 7 15 0 2 3 2 0 1 7 0 1 2 3 4 0 1 7 12 2 3 0 7 0 1 2 3 4 0 1 7 14 2 3 2 0 1

- 69. Gestión de Memoria 69 CT(t2, 10) = t2 {3,4} Paginación (Cuestiones de diseño: conjunto de trabajo) • ¿Qué hacer cuando un proceso pasa a ejecución? Carga por Demanda • Se van cargando las páginas que el proceso vaya necesitando Muchas F.P. evitables Prealimentación • Se arranca la carga del conjunto de trabajo del proceso. “Páginas usadas más recientemente” 2,6,1,5,7,7,7,7,5,1,6,2,3,4,1,2,3,4,4,4,4,3,4,3,4,4,4,1,3,2,3,4,4,1,3 CT(t1, 10) = t1 {1,2,5,6,7} 5 900 300 40 128 5 128

- 70. Gestión de Memoria 70 Paginación ( Cuestiones de diseño: trasiego ) Páginas = 20 CT = 7 MV MP Cabe en MP ¿Más Procesos? Páginas = 26 CT = 11 MP MV No cabe en MP => CT mayor que MP => Trasiego ¿Tamaño de página? ¿Grandes? Más Fragmentación Interna Mejor rendimiento E/S ¿Pequeñas? Mejor ajuste de localidad Más ineficiencia de E/S 2n => 512B .. 4/8KB y aumentando ¡Superpáginas! sysconf (_SC_PAGESIZE)

- 71. Gestión de Memoria 71 Paginación (Cuestiones de diseño: superpáginas ) VPN 1 VPN 2 VPN 3 VP OFF 9 9 9 21 dirVirtual 2MB VPN 1 VPN 2 VP OFF 9 9 30 dirVirtual 1GB VPN 1 VPN 2 VPN 3 VPN 4 VP OFF 9 9 9 9 12 dirVirtual 4KB Intel Core i7 “long mode” Páginas de

- 72. Gestión de Memoria 72 Paginación ( Cuestiones de diseño: otras ) • Asignación local frente a global • Control de carga Pi Pj PFF FIN Asignar + marcos Devolver marcos Retirar temporalmente algún proceso ¿Intercambio?