Lattice

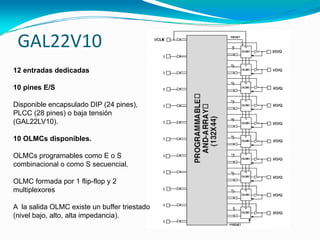

- 1. GAL22V10 12 entradas dedicadas 10 pines E/S Disponible encapsulado DIP (24 pines), PLCC (28 pines) o baja tensión (GAL22LV10). 10 OLMCs disponibles. OLMCs programables como E o S combinacional o como S secuencial. OLMC formada por 1 flip-flop y 2 multiplexores A la salida OLMC existe un buffer triestado (nivel bajo, alto, alta impedancia).

- 2. GAL22V10 OUTPUT LOGIC MACROCELL (OLMC) Matriz AND‐OR Multiplexor que activa el modo (combinacional o registrado)

- 3. Elementos para programar una GAL Ordenador (microcontrolador, memoria y sistema operativo). Software de programación(compilador lógico). ABEL, VHDL, VERILOG, AHDL. Permite simular y depurar de forma completa un diseño lógico antes de fabricar el hardware. Procesan y sintetizan el diseño lógico introducido, convierten los datos introducidos en un fichero intermedio y generan un archivo de salida JEDEC(mapa de estados o mapa de fusibles) Métodos para introducir el diseño lógico: ecuación booleana, tabla de verdad o máquina de estados; métodos de tipo esquemático: diagramas de tiempo y descripción hardware.

- 4. Elementos para programar una GAL Programador de SPLD(controlable por software). Tiene un programa controlador de software que lee el archivo JEDEC, generado por el compilador lógico, y lo convierte en instrucciones que aplican las tensiones requeridas en pines específicos del SPLD se alteran las celdas especificadas de la matriz según el JEDEC. JEDEC: Joint Electronic Device Engineering Council

- 5. Usando Lattice, IspLever Classic 1.- Crear una nueva carpeta 2.- Ejecutar 3.- File New Proyect

- 6. Seleccionar el tipo de GAL

- 7. Se puede Seleccionar adicionar un proyecto creado anteriormente en alguna plataforma de diseño (ISE de Xilinx ó Maxplus de Altera) mediante Add Source , y se selecciona nuestro archivo con extensión VHD o en su debido caso comenzar a crear un nuevo proyecto inicial. Adición de programa

- 8. Seleccionar un modulo de VHDL para el proyecto elegido o para el proyecto inicial. Damos siguiente y finalizamos para terminar de adicionar o crear el proyecto.

- 9. Dando Doble clic sobre el nuestro archivo ( xxx.vhd), nos abre el editor de texto donde aparece nuestro programa ya adicionado.

- 10. Si se desea partir de un proyecto nuevo, posicionándonos sobre el dispositivo (SPLD (GAL)) y con el botón derecho del mouse elegimos NEW, donde enseguida aparecerá la opción para la creación del modulo entidad con la definición de las variables de entrada y salida.

- 11. Creación y definición de la entidad

- 12. Diseño del programa para el sistema de la cuchilla

- 13. Para realizar la compilación del programa utilizamos la opción: precision synthesize VHDL file. O bien synplicity synthesize VHDL file

- 14. Es necesario generar el mapa de fusibles para la GAL, para ello, sobre la GAL Seleccionamos y elegimos crear mapa de fusibles (create fuse map) con el cual obtendremos el archivo tipo jedec (***.jed).

- 15. Para poder observar la asignación que el compilador genera, el mapa de fusibles sobre la GAL, seleccionamos el reporte del chip (chip report).

- 16. Se puede observar la colocación de las terminales en la ventana inferior, dentro del software ispLEVER.

- 17. Buscar y colocar el archivo que se va a descargar con la extensión XXX.JED. Este es el archivo que se debe guardar en un dispositivo extraíble (USB y/o diskette) para poderlo abrir en el programador de memorias. No olvidar que para programar la GAL hay que seleccionar en el Max loader el tipo de GAL, y después abrir el archivo de nuestro programa (xxx.JED),para posteriormente programar la GAL.

- 18. Max Loader Dentro del software MAX LOADER , primero debemos indicarle que tipo de dispositivo queremos programar. En este caso el tipo de GAL. Este paso se realiza dando click sobre la pestaña select,

- 19. Max Loader Escribiendo directamente sobre el espacio marcado por “FIND” el tipo de gal a programar. O bien ubicando dentro del espacio “Manufacturer” Al fabricante, en este caso “Lattice”. Y dentro del espacio “Device Name”, seleccionamos la matricula de la gal a programar Y por ultimo seleccionamos OK

- 20. Max Loader Una vez que hemos seleccionado el tipo de gal, procedemos a cargar el archivo xxx.jed, que nos permitirá grabar el mapa de fusibles dentro de la gal.

- 21. Max Loader Una vez que hemos cargado el archivo: Primero: insertamos la gal dentro del zócalo con la debida orientación, marcada en el programador.

- 22. Max Loader Segundo: borramos la gal con la opción “erase”. Tercero: programamos la gal con la opción “prog”. Finalmente retiramos la gal del programador.