Trabajo de circuito combinacionales

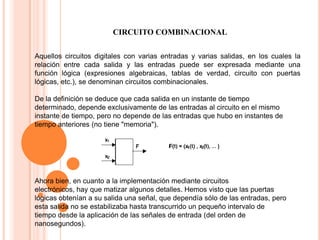

- 1. CIRCUITO COMBINACIONAL Aquellos circuitos digitales con varias entradas y varias salidas, en los cuales la relación entre cada salida y las entradas puede ser expresada mediante una función lógica (expresiones algebraicas, tablas de verdad, circuito con puertas lógicas, etc.), se denominan circuitos combinacionales. De la definición se deduce que cada salida en un instante de tiempo determinado, depende exclusivamente de las entradas al circuito en el mismo instante de tiempo, pero no depende de las entradas que hubo en instantes de tiempo anteriores (no tiene "memoria"). Ahora bien, en cuanto a la implementación mediante circuitos electrónicos, hay que matizar algunos detalles. Hemos visto que las puertas lógicas obtenían a su salida una señal, que dependía sólo de las entradas, pero esta salida no se estabilizaba hasta transcurrido un pequeño intervalo de tiempo desde la aplicación de las señales de entrada (del orden de nanosegundos).

- 2. Por otro lado, si el circuito combinacional tiene varias entradas (n), también puede tener varias salidas (m). Para "n" variables de entrada tenemos 2n combinaciones binarias posibles. Por tanto, podemos expresar un circuito combinacional mediante una tabla de verdad que lista los valores de todas las salidas para cada una de las combinaciones de entrada. Un circuito combinacional también puede describirse mediante "m" funciones lógicas, una para cada variable de salida; cada una de las cuales se presenta como función de las "n" variables de entrada. Multifunciones: Son aquellas funciones que tienen varias salidas, por lo que habrá una expresión lógica para cada salida.

- 3. Circuitos sumadores y restadores • Sumador binario El sumador binario es el elemento básico de la unidad aritmética de cualquier ordenador, pues cualquier operación aritmética básica puede realizarse a partir de sumas y restas repetidas. Para sumar dos números de n bits, hay que sumar dos a dos los bits del mismo peso y el acarreo de la suma de los bits de peso inmediato inferior. • Semisumador (half adder) Es un circuito combinacional que realiza la suma de dos dígitos binarios, obteniendo su suma y el acarreo para la etapa siguiente. No tiene en cuenta el bit de acarreo de la etapa anterior. Su tabla de verdad, y símbolo como bloque es:

- 4. • Puertas Lógicas Una de las principales ventajas de utilizar el álgebra de conmutación radica en que las operaciones básicas de este álgebra (operación AND, OR y NOT) tienen un equivalente directo en términos de circuitos. Estos circuitos equivalentes a estas operaciones reciben el nombre de puertas lógicas. No obstante, el resto de circuitos lógicos básicos también reciben el nombre de puertas, aunque su equivalencia se produce hacia una composición de las operaciones lógicas básicas. Las tres puertas fundamentales reciben el mismo nombre que los operadores, es decir, existen las puertas AND, puertas OR y puertas NOT. La última puerta recibe el nombre más usual de inversor.

- 5. Se puede probar que tanto las puertas NAND como las puertas NOR forman un conjunto com- pleto, como vemos en la figura En primer lugar debemos identificar aquellos conjuntos de puertas con los que se puede implementar cualquier función lógica. Así Un conjunto de puertas completo es aquel conjunto con el que se puede implementar cualquier función lógica El conjunto completo más intuitivo es aquel formado por todas las operaciones básicas del álgebra de conmutación, es decir, el conjunto formado por puertas AND, OR e inversores.

- 6. Implementando por "1": S = a' · b + a · b' = a Å b C=a·b La suma S responde a una función OR-exclusiva y el acarreo C a una función AND. Si no deseamos utilizar la puerta OR-Exclusiva por su coste superior, el semisumador se puede implementar de la siguiente forma:

- 7. Implementando por "0": S = (a+b) · (a'+b') = = ((a+b) · (a'+b'))' ' = ((a+b)' + (a'+b')')' = ((a+b)’ + (a·b))' = = (a+b) · (a·b)' C=a·b • Etapa de sumador (sumador completo) Es un circuito combinacional capaz de sumar dos dígitos (cifras) binarios, teniendo en cuenta el acarreo producido en la etapa anterior. Obtiene la suma y el acarreo para la etapa siguiente.Su tabla de verdad y símbolo como bloque es:

- 8. Simplificamos mediante tablas de Karnaugh las funciones de salida S y Cout. Para ello, construimos las tablas correspondientes implementando por "1“ desde la tabla de verdad. La función S no se puede simplificar, ya que tenemos 4 1's o 4 0's aislados, pero Cout si, obteniéndose (implementando por 1):

- 9. Hemos manipulado las funciones de salida S y Cout para que incluyan la OR-Exclusiva (recordar la función S del semisumador). Esto significa que para implementar la función sumador completo, se pueden utilizar dos puertas ORExclusiva. Por razones económicas, los fabricantes emplean para la implementación circuitos de nivel superior (más lentos), pero que permiten un gran ahorro en el número de puertas empleadas. Una forma simple de implementar la etapa de sumador es a partir de dos semisumadores. Como hay que sumar los dos bits (dígitos) del mismo peso más el acarreo anterior, se utiliza un semisumador para sumar los dos dígitos y el resultado se suma con el acarreo anterior mediante otro semisumador. Si en alguna de las dos sumas parciales se produce acarreo, habrá acarreo en la etapa de sumador (función OR). Esto puede comprobarse en la tabla de verdad. La etapa de sumador puede implementarse con el siguiente circuito.

- 10. • Sumador binario de n bits: Para sumar números de n bits, se pueden emplear diferentes circuitos, pero todos llevan como unidad básica la etapa de sumador. La forma más simple de realizar un sumador de n bits es disponer de n etapas de sumador, conectadas de tal forma que la salida de acarreo de cada etapa excita a la entrada de acarreo de la etapa siguiente. Este circuito se denomina sumador paralelo con acarreo en serie. Denotamos con subíndices cada uno de los bits de los sumandos, indicando con el subíndice 1 el bit menos significativo (LSB).

- 11. Téngase en cuenta que para la posición menos significativa se puede usar un semisumador, o bien, poner a 0 voltios (masa) la entrada de acarreo de un sumador completo, ya que no existe entrada de acarreo en la posición del bit menos significativo. Su diagrama funcional o de bloques es:

- 12. CODIFICADORES Y DECODIFICADORES • Codificadores Son circuitos combinacionales que permiten pasar una información en forma decodificada (dígito decimal u octal) a una forma codificada (BCD o binario). Si nos limitamos a sistemas binarios, el codificador deberá tener n salidas si queremos codificar m entradas, siendo m < 2n . De esta forma, m informaciones diferentes quedan representadas mediante grupos de n bits, es decir, las líneas de salida generan el código binario correspondiente al valor de entrada.

- 13. Ejemplo: Codificador octal a binario Tenemos 8 entradas, una para cada dígito octal, y tres salidas que generan el número binario correspondiente. Se supone que sólo una entrada tiene un valor de 1 en cualquier momento. Si implementamos por “1”, obtenemos las funciones lógicas de las 3 salidas: · S0 = E1 + E3 + E5 + E7 · S1 = E2 + E3 + E6 + E7 · S2 = E4 + E5 + E6 + E7

- 14. Ejemplo: Teclados Ejemplos típicos de codificación son los utilizados en los teclados de los computadores y máquinas de calcular. En un teclado alfanumérico, por ejemplo, tenemos 27 teclas para letras y 10 para cifras. Cada tecla va conectada a una línea eléctrica, que estará a nivel lógico “1” ó “0”, según la tecla correspondiente esté pulsada o no. Para que la información enviada por el teclado al computador se transmita, es inviable disponer de tantas líneas como teclas. Por ello se emplea un codificador que permite pasar del número de líneas igual al de teclas, a sólo 7 líneas, si se emplea, por ejemplo, código ASCII. Otro caso típico es el del teclado numérico, en el cual, mediante un codificador, se pasa de 10 líneas a 4 líneas. Vamos a ver como ejemplo este caso, suponiendo que el código de salida es BCD (Decimal Codificado en Binario). Como hay 10 símbolos diferentes serán necesarias 10 entradas y 4 salidas. La correspondencia entre entradas y salidas se representa en la tabla siguiente:

- 15. Implementando por “1”, las 4 funciones de las salida son: S3 = E8 + E9 S2 = E4 + E5 + E6 + E7 S1 = E2 + E3 + E6 + E7 S0 = E1 + E3 + E5 + E7 + E9 que pueden realizarse mediante puertas OR: Notemos que E0 no participa en la elaboración del código de salida. En el caso del teclado sería equivalente pulsar "0" que no pulsar nada. En estos casos se añade una salida adicional que indica cuando se ha pulsado alguna tecla.

- 16. Decodificadores Realizan la función inversa de los codificadores. Partiendo de una información codificada de n bits, obtiene la información de que se trata. El número m de informaciones que se pueden obtener (salidas) debe ser tal que m < 2n. Si la información codificada de n bits tiene combinaciones no usadas (indiferencias), el decodificador podría tener menos de 2n salidas. Decodificador de BCD a decimal

- 17. Implementando por "1“: S0 = E3' · E2' · E1' · E0' S1 = E3' · E2' · E1' · E0 S2 = E3' · E2' · E1 · E0' S3 = E3' · E2' · E1 · E0 S4 = E3' · E2 · E1' · E0' S5 = E3' · E2 · E1’ · E0 S6 = E3' · E2 · E1 · E0' S7 = E3' · E2 · E1 · E0 S8 = E3 · E2' · E1' · E0' S9 = E3 · E2' · E1' · E0

- 18. Si no simplificamos las funciones, utilizando inversores y puertas AND de 4 entradas podemos implementar el circuito del siguiente modo Este decodificador activa (pone a 1) una de sus salidas, cuando se presenta una combinación válida en la entrada. En cambio, si el código no es válido (por ejemplo, 1 1 1 1), no se activa ninguna salida. Por tanto, con este diseño se eliminan las combinaciones de entrada no válidas. Es posible diseñar un decodificador que no elimine las combinaciones no válidas, con la ventaja de que resulta un circuito más simple y económico.

- 19. Decodificador de BCD a segmentación en siete Los dispositivos de visualización de las calculadoras electrónicas y relojes digitales utilizan diodos emisores de luz (LEDs). Cada dígito del dispositivo se forma con siete segmentos, cada uno consistente en un LED que se ilumina mediante señales digitales. El decodificador que vamos a ver es un circuito combinacional que acepta un dígito decimal en BCD y genera las salidas adecuadas para la selección de los segmentos que representan el dígito decimal. Disposición de los segmentos en un display de 7 segmentos: Como vemos, cada segmento se utiliza para varios dígitos decimales,pero ninguno de ellos se emplea para representar todos los dígitos decimales.Por tanto, debemos determinar los segmentos que hay que activar para cada uno de los dígitos decimales

- 20. MULTIPLEXORES Y DEMULTIPLEXORES • Multiplexores Son circuitos combinacionales con una estructura de varias entradas y una única salida de datos. Permiten seleccionar una de las entradas para realizar la transmisión de datos desde dicha entrada a la salida, que es única. Los demultiplexores realizan la función inversa. Esquemáticamente:

- 21. Un multiplexor es un selector de datos equivalente a un conmutador de "m" entradas y una salida, por lo que también recibe el nombre de selector de datos o conmutador electrónico. La selección de la entrada se controla mediante unas entradas de selección o control. Cuando sólo tenemos una entrada de control (2 entradas), también se le llama entrada de habilitación (enable). La entrada seleccionada viene biunívocamente determinada por la combinación de "0" y "1" en las entradas de control. Por tanto, si tenemos "m“ entradas de datos, harán falta "n" entradas de control, siendo m < 2n . Un multiplexor de 4 entradas de datos (4 a 1)

- 22. en donde la x significa que el valor de dicha entrada no influye en la salida. Implementando por "1" tenemos: S = C1' · C0' · E0 + C1' · C0 · E1 + C1 · C0’ · E2 + C1 · C0 · E3 Esta función se puede simplificar más. La implementación con puertas lógicas es la siguiente:

- 23. NOTA: Podemos agrupar varios multiplexores para formar otros de mayor número de entradas. Por ejemplo, con 5 multiplexores de 4 entradas podemos formar 1 multiplexor de 16 entradas. Además será necesario alguna lógica en las líneas de control o selección, para habilitar sólo los multiplexores que nos interesen. Multiplexor de 4 entradas Partimos de la misma función lógica, ya expresada en términos canónicos: F(a,b,c) = a·b·c + a·b·c’ + a’·b·c + a·b’·c’ + a’·b’·c’

- 24. • Demultiplexores Un demultiplexor es un circuito combinacional que realiza la función inversa de un multiplexor, es decir, expande un circuito de una sola señal de entrada a varias señales de salida: 2n. La información se redirige a una sola salida. La selección de la salida específica es controlada por la combinación de bits de n líneas de selección o control. El diagrama de bloque es:

- 25. • Si examinamos el circuito veremos que el circuito demultiplexor es idéntico a un decodificador de 2 a 4 líneas con entrada de habilitación: • Para el decodificador: las entradas de datos son C0 y C1, y la habilitación es la entrada E. • Para el demultiplexor: la entrada E provee los datos, mientras que las entradas C0 y C1 son las entradas de control o selección.