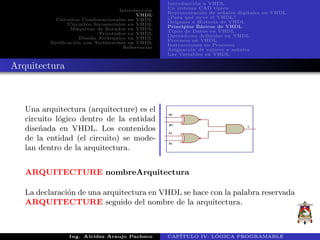

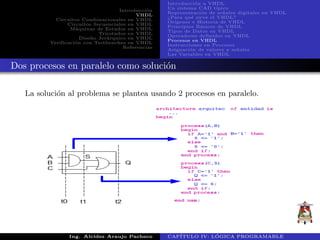

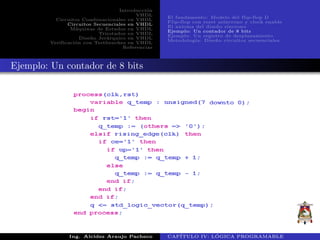

El documento describe los pasos principales en el diseño de circuitos lógicos utilizando herramientas CAD. Estos incluyen la entrada de diseño mediante captura esquemática o lenguajes de descripción de hardware como VHDL, la síntesis para generar implementaciones de circuitos a partir de las especificaciones, y la simulación funcional para verificar que los circuitos funcionan como se esperaba.