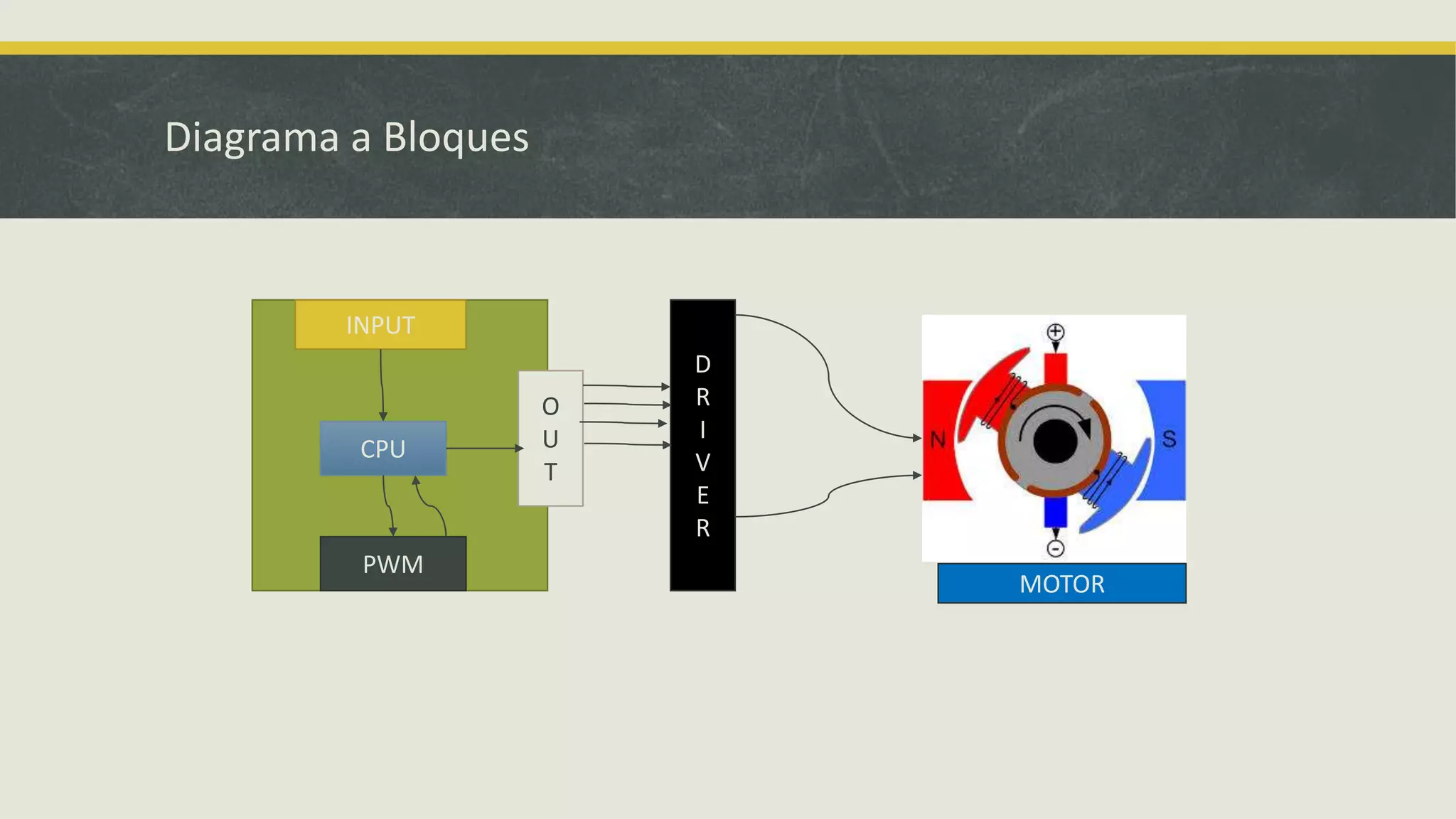

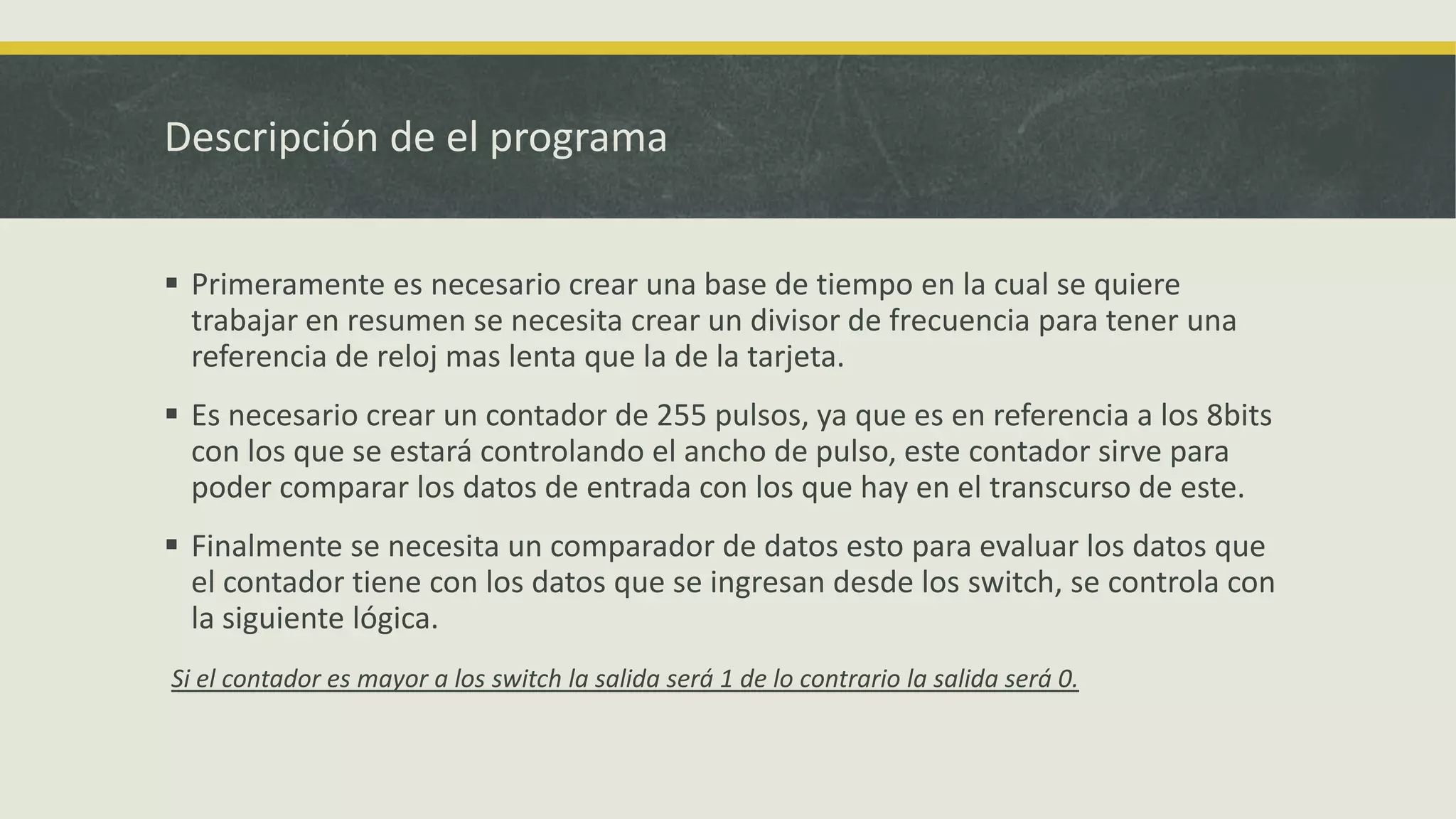

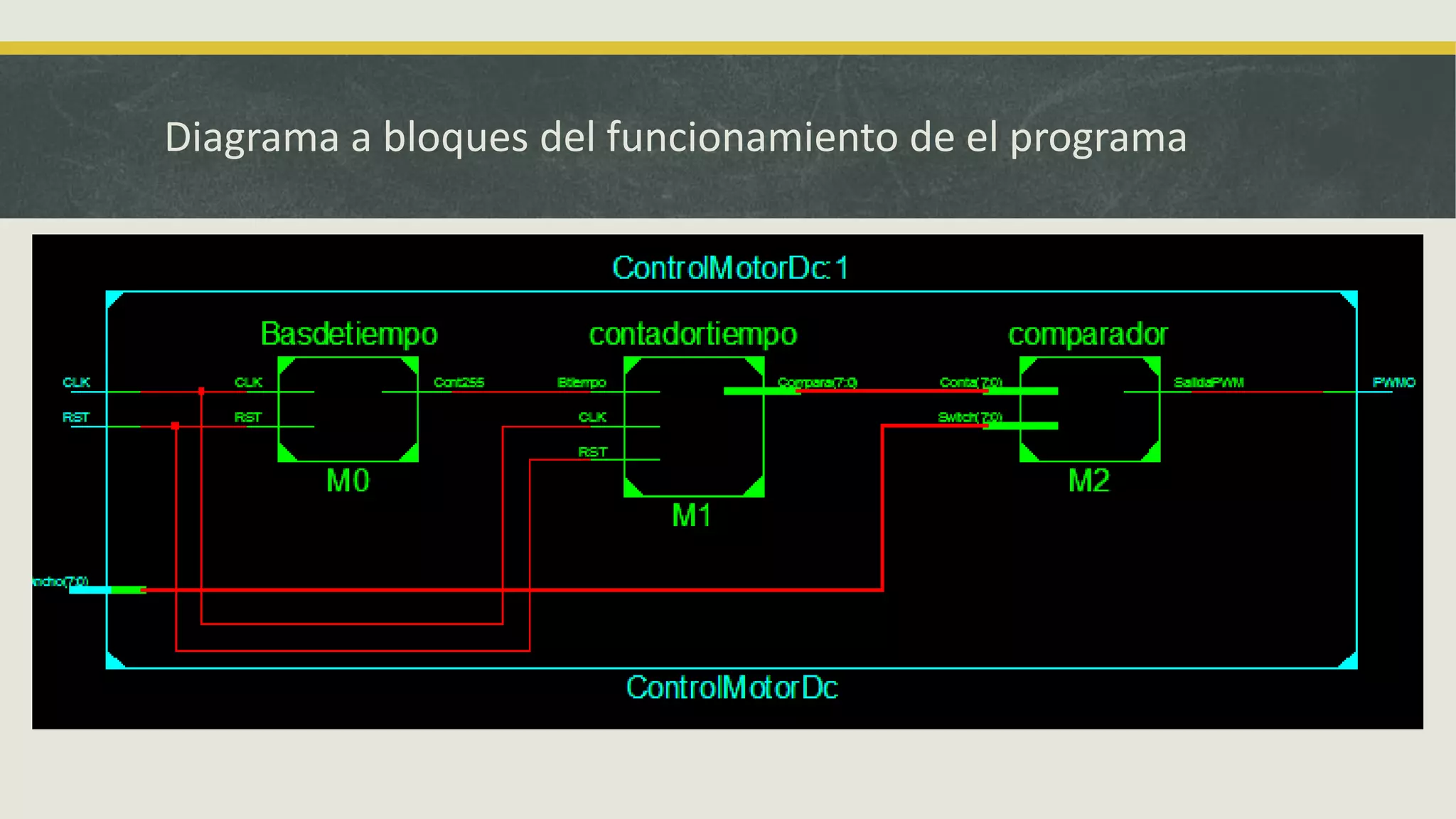

El documento detalla el desarrollo de un controlador de velocidad para un motor DC utilizando un FPGA y código VHDL, centrándose en la modulación por ancho de pulso (PWM). Se describen los problemas y soluciones involucrados en la programación y conexión del sistema, así como la optimización del tiempo de respuesta para mejorar el rendimiento. La conclusión resalta la complejidad del código VHDL y la importancia de los diagramas de bloques para el diseño del sistema.