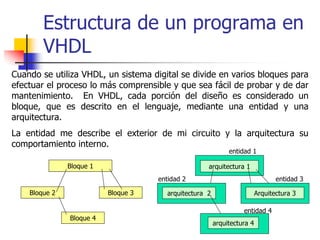

Este documento describe el lenguaje de descripción de hardware VHDL. Explica que VHDL permite describir circuitos digitales de una manera independiente de la tecnología para luego simularlos y fabricarlos. Describe las características principales de VHDL como su capacidad para trabajar de manera jerárquica y ser independiente de la implementación física. También explica la estructura básica de un programa VHDL que incluye la declaración de la entidad, la arquitectura y el uso de tipos de datos como BIT y BIT_

![Estructura de un programa

escrito en VHDL

En VHDL una arquitectura ARCHITECTURE nombre_arq OF nombre_ent IS

tiene dos partes: La

región de las declaraciones [Declaración de señales]

[Declaración de tipos]

y el cuerpo de la [Declaración de variables]

arquitectura. [Declaración de constantes]

[Declaración de componentes]

La región de declaraciones [Especificación de atributos]

precede la palabra clave

BEGIN. Puede ser usada BEGIN

para declarar señales, {Instanciación de componentes}

variables y constantes. {Enunciado concurrente}

{Enunciado secuencial [Proceso]}

También puede ser usada

para declarar componentes END nombre_arq;

y especificar atributos.](https://image.slidesharecdn.com/sd3-100428212433-phpapp01/85/Sd3-11-320.jpg)

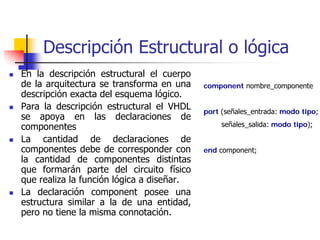

![Descripción Estructural o lógica

En la sección de declaraciones de la

arquitectura (región ubicada entre la ARCHITECTURE nombre_arq OF nombre_ent IS

palabra reservada architecture y la [Declaración de tipos]

palabra begin) puede existir la necesidad [Declaración de señales]

[Declaración de variables]

de realizar algunas declaraciones de [Declaración de constantes]

señales internas, las cuales intervienen [Declaración de componentes]

[Especificación de atributos]

en la descripción del circuito, pero que

no tienen acceso a los terminales BEGIN

externos del diseño (no están declaradas Instanciación de componentes

en la entidad.

...

Aparecen en mayúsculas las palabras

Instanciación de componentes

reservadas del lenguaje VHDL para

resaltarlas, pero no es necesario ya que END nombre_arq;

el VHDL no es sensible al tipo de letra](https://image.slidesharecdn.com/sd3-100428212433-phpapp01/85/Sd3-14-320.jpg)

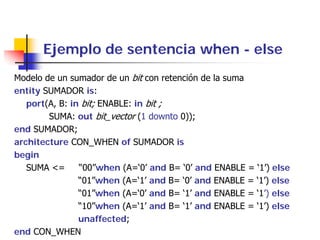

![Sentencia when - else

Permite realizar asignaciones condicionales de valores, expresiones u

objetos o señales. Su sintaxis de declaración es:

[etiqueta:] señal <= valor_1 when condición_1 else

valor_2 [when condición_2] [else

… ] [else

valor_n when condición_n] [else unaffected];

La señal recibe una asignación u otra (valor_1…valor_n) en función de

las condiciones que aparecen tras when. Para la opción de no

asignación puede (no cambio en la función) utilizarse la keyword

unaffected](https://image.slidesharecdn.com/sd3-100428212433-phpapp01/85/Sd3-47-320.jpg)

![Sentencia with-select

Su sintaxis es la siguiente:

[etiqueta:] with expresión select

señal <= valor_1 when resultado_1[,

valor_2 when resultado_2] [,

……..] [,

valor_n when resultado_n] [,

unaffected when others];

El valor asignado depende de la evaluación de la expresión que aparece

entre las palabras reservadas with y select. El resultado se compara con

los valores tras when y se ejecuta la asignación que resulta verdadera.](https://image.slidesharecdn.com/sd3-100428212433-phpapp01/85/Sd3-49-320.jpg)

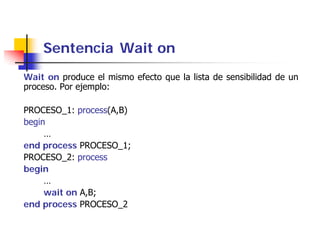

![Sentencia wait

Es una de las más utilizadas en el modelado de circuitos síncronos,

wait detiene la ejecución de un proceso o un procedimiento en

espera de que se satisfaga una determinada condición. Su sintaxis es

la siguiente:

[etiqueta:] wait [on señal_1, señal_2,…..]

[until condición]

[for expresión_temporal];

Por tanto puede haber tres tipos de argumentos de ellos, o bien

ninguno. En este último caso el proceso queda detenido hasta el final

de la simulación.](https://image.slidesharecdn.com/sd3-100428212433-phpapp01/85/Sd3-52-320.jpg)

![Case - when

La sentencia case-when permite seleccionar una entre varias

alternativas excluyentes entre sí de una expresión determinada, su

sintaxis general es la siguiente:

[etiqueta:] case expresión is

when caso_1[ caso_2 ……] => sentencias secuenciales

....

end case [etiqueta];

De este modo una arquitectura alternativa para el mismo sumador

anterior podría ser como se muestra a continuación.](https://image.slidesharecdn.com/sd3-100428212433-phpapp01/85/Sd3-54-320.jpg)

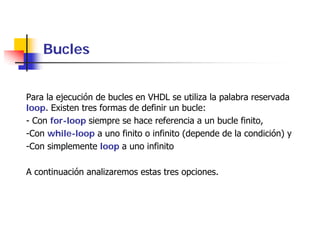

![For - Loop

Esta sentencia causa la ejecución de un bucle un numero fijo de veces,

su sintaxis es la siguiente:

[etiqueta:] for indice in rango loop

sentencias secuenciales

end loop [etiqueta];

Es necesaria las indicaciones de un índice y un rango. El índice es una

variable discreta, enumerada o entera, que no es preciso declarar y que

cambia su valor en una unidad por cada ejecución del bucle a lo largo

del rango especificado.](https://image.slidesharecdn.com/sd3-100428212433-phpapp01/85/Sd3-57-320.jpg)

![While - Loop

El siguiente tipo de bucle utiliza la palabra reservada while para

imponer la condición de repetición. Su sintaxis es la siguiente:

[etiqueta:] while condición loop

sentencias secuenciales

end loop [etiqueta];

El bucle se repite en tanto que la condición que aparece tras while sea

verdadera.](https://image.slidesharecdn.com/sd3-100428212433-phpapp01/85/Sd3-59-320.jpg)

![Loop

Ejecuta un bucle infinito y su sintaxis es así:

[etiqueta:] loop

sentencias secuenciales

end loop [etiqueta];](https://image.slidesharecdn.com/sd3-100428212433-phpapp01/85/Sd3-61-320.jpg)