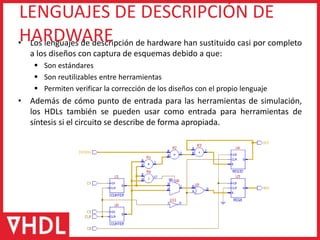

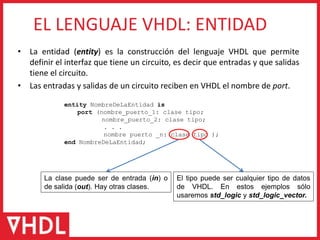

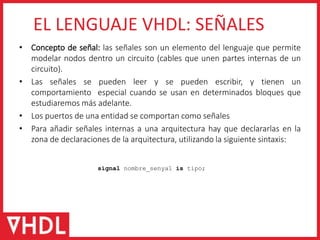

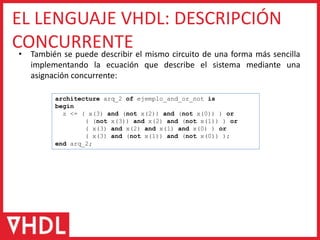

Este documento introduce el lenguaje VHDL para la descripción de hardware. Explica que VHDL permite describir circuitos digitales a diferentes niveles de abstracción de forma modular y jerárquica e independiente de la tecnología. Describe las características básicas de VHDL como librerías, entidades, arquitecturas, señales, asignaciones concurrentes y procesos, y muestra ejemplos de su uso para describir circuitos como multiplexores de forma estructural y concurrente.