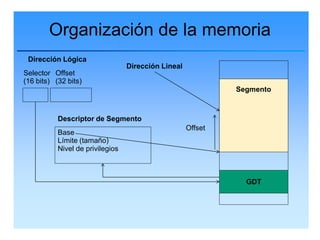

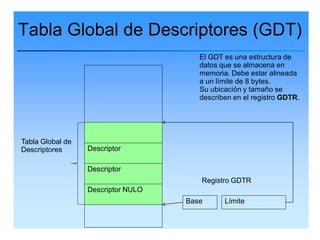

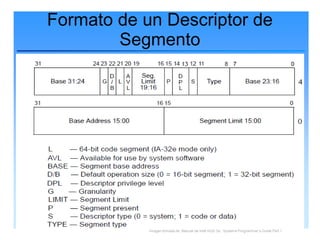

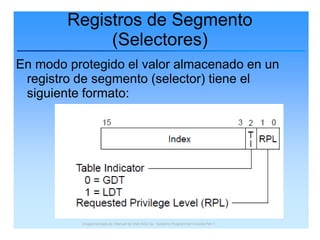

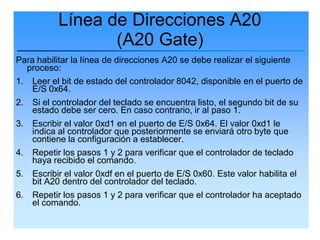

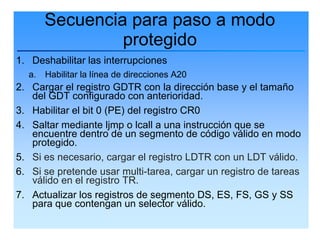

El documento describe el modo protegido de la arquitectura IA-32. El modo protegido permite acceso a todas las características del procesador e introduce protección de memoria, modo segmentado y espacio de direcciones de 32 bits. Para pasar al modo protegido se debe configurar la Tabla Global de Descriptores, habilitar la línea A20 y establecer el bit de protección en el registro CR0.