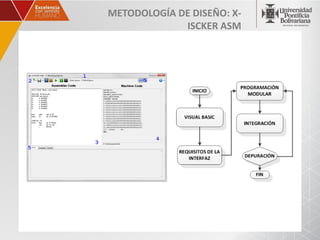

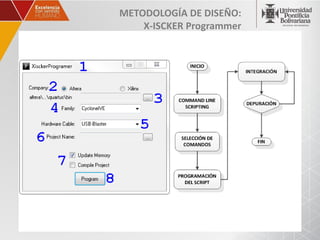

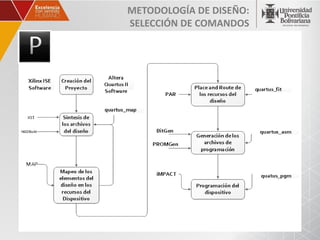

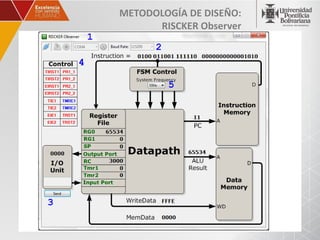

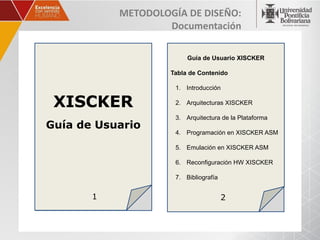

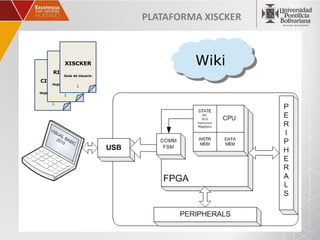

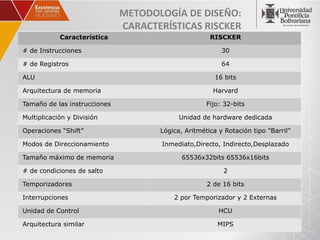

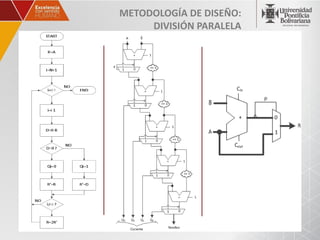

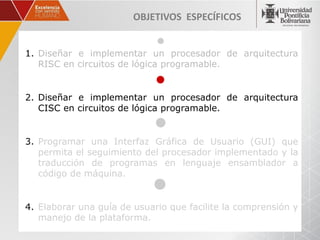

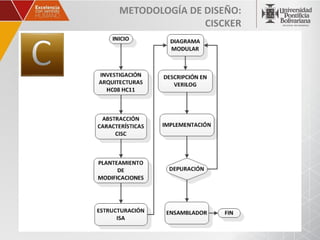

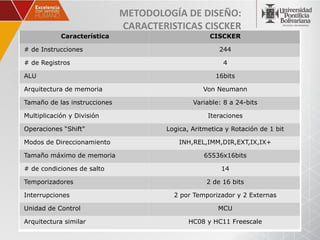

El documento presenta el diseño y desarrollo de una plataforma para emular y reconfigurar arquitecturas RISC y CISC utilizando Verilog para FPGA y una interfaz gráfica en Visual Basic. Se detallan objetivos específicos enfocados en la implementación de procesadores, desarrollo de una GUI, y elaboración de una guía de usuario para facilitar la comprensión y manejo de la plataforma. También se describen las metodologías de diseño y características técnicas de las arquitecturas propuestas.

![METODOLOGÍA DE DISEÑO:

ESTRUCTURACIÓN ISA

TIPO R

0000 Rd Rs Rt Function [ALU operation & Shift amount]

TIPO I

Opcode Rd Rs Inmediato

TIPO J

Opcode Inmediato

Opcode Rd Rs Inmediato

Opcode Rd Inmediato](https://image.slidesharecdn.com/sustentacinlibre-120809145030-phpapp02/85/Presentacion-Proyecto-de-Grado-X-ISCKER-8-320.jpg)

![METODOLOGÍA DE DISEÑO:

SINTAXIS ASSEMBLER

[Etiqueta] : [Operación] [Operandos] ; [Comentario]

[Etiqueta]:[Operación] [Rd],[Rs],[Rt],#[Imm/Dir];[Comentario]

beq rg1, rg0, #16 ;Salto condicional, si rg1 es igual a

;rg0 a la dirección 16

lw rg3, r0, #0

;Cargar el registro rg3 con el dato Memoria[r0+0]

inc op ;Incrementar el puerto de salida (op)](https://image.slidesharecdn.com/sustentacinlibre-120809145030-phpapp02/85/Presentacion-Proyecto-de-Grado-X-ISCKER-15-320.jpg)

![METODOLOGÍA DE DISEÑO:

SINTAXIS ASSEMBLER

[Etiqueta]: [Operación] [Operando], [MD] ;[Comentarios]

ADDA #10, IX ; Sumar ACCA con Memoria[IX+10]

INCA ; Incrementar ACCA](https://image.slidesharecdn.com/sustentacinlibre-120809145030-phpapp02/85/Presentacion-Proyecto-de-Grado-X-ISCKER-27-320.jpg)