Fgl029 guiano2arquitecturasvhdl (1)

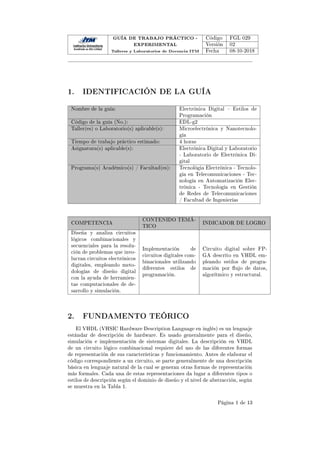

- 1. GUÍA DE TRABAJO PRÁCTICO - EXPERIMENTAL Talleres y Laboratorios de Docencia ITM Código FGL 029 Versión 02 Fecha 08-10-2018 1. IDENTIFICACIÓN DE LA GUÍA Nombre de la guía: Electrónica Digital Estilos de Programación Código de la guía (No.): EDL-g2 Taller(es) o Laboratorio(s) aplicable(s): Microelectrónica y Nanotecnolo- gía Tiempo de trabajo práctico estimado: 4 horas Asignatura(s) aplicable(s): Electrónica Digital y Laboratorio - Laboratorio de Electrónica Di- gital Programa(s) Académico(s) / Facultad(es): Tecnológia Electrónica - Tecnolo- gía en Telecomunicaciones - Tec- nología en Automatización Elec- trónica - Tecnología en Gestión de Redes de Telecomunicaciones / Facultad de Ingenierías COMPETENCIA CONTENIDO TEMÁ- TICO INDICADOR DE LOGRO Diseña y analiza circuitos lógicos combinacionales y secuenciales para la resolu- ción de problemas que invo- lucran circuitos electrónicos digitales, empleando meto- dologías de diseño digital con la ayuda de herramien- tas computacionales de de- sarrollo y simulación. Implementación de circuitos digitales com- binacionales utilizando diferentes estilos de programación. Circuito digital sobre FP- GA descrito en VHDL em- pleando estilos de progra- mación por ujo de datos, algorítmico y estructural. 2. FUNDAMENTO TEÓRICO El VHDL (VHSIC Hardware Description Language en inglés) es un lenguaje estándar de descripción de hardware. Es usado generalmente para el diseño, simulación e implementación de sistemas digitales. La descripción en VHDL de un circuito lógico combinacional requiere del uso de las diferentes formas de representación de sus características y funcionamiento. Antes de elaborar el código correspondiente a un circuito, se parte generalmente de una descripción básica en lenguaje natural de la cual se generan otras formas de representación más formales. Cada una de estas representaciones da lugar a diferentes tipos o estilos de descripción según el dominio de diseño y el nivel de abstracción, según se muestra en la Tabla 1. Página 1 de 13

- 2. GUÍA DE TRABAJO PRÁCTICO - EXPERIMENTAL Talleres y Laboratorios de Docencia ITM Código FGL 029 Versión 02 Fecha 08-10-2018 Tabla 1: Tipos de descripción de circuitos según el dominio de diseño y el nivel de abstracción. DOMINIO DE DISEÑO TIPO DE DESCRIPCIÓN APLICACIÓN Estructural Estructural: bloques Circuitos combinacionales Funcional Flujo de datos: tabla de ver- dad o función lógica Circuitos combinacionales Comportamental: algorítmico Circuitos combinacionales y secuenciales Un módulo hardware en VHDL tiene una estructura bien denida que lo describe de una manera clara y lógica. Las partes del módulo son: 1. La declaración de entidad: describe la interfaz del módulo permitiendo denir las entradas y salidas. 2. La declaración de la arquitectura: permite describir la funcionalidad in- terna u operación del módulo. La Figura 1 muestra un sumador completo de 1 bit. En el esquemático se pueden observar su interfaz, puertos de entrada y salida, y su estructura interna. y z ŝ Ž Figura 1: Diagrama esquemático del sumador completo de 1 bit. La declaración de entidad inicia con la palabra reservada entity y naliza con la palabra reservada end. Toda entidad debe incluir un nombre, que en este caso es eFullAdder, y la declaración de los puertos de entrada (in) X, Y y Ci, y de salidad (out) Z y Co. Además del nombre y la dirección de cada puerto se establece el tipo de dato de cada uno (STD_LOGIC ) (véase Código 2.1). STD_LOGIC es un tipo de dato denido en VHDL que se utiliza para representar la unidad básica de información, el bit, y con el cual se pueden indicar diferentes estados de un bit como el 1 lógico, el 0 lógico, valores no importa, y estado de alta impedancia, entre otros. El bloque de declaración de la arquitectura inicia con la palabra reservada architecture. El cuerpo de la arquitectura tiene un nombre, en este caso aFullAd- der, y se debe indicar cual entidad implementa, en este caso eFullAdder. Igual que la entidad, la arquitectura termina con la palabra reservada end, y en medio de ellas está la palabra reservada begin. Esta palabra divide la arquitectura en dos partes: la zona de declaraciones y la zona de sentencias de la descripción funcional. En la zona de declaraciones de la arquitectura, opcionalmente, se pue- den declarar los componentes, necesario para un diseño jerárquico, y declarar señales, necesarias para interconectar componentes dentro del código funcional. Página 2 de 13

- 3. GUÍA DE TRABAJO PRÁCTICO - EXPERIMENTAL Talleres y Laboratorios de Docencia ITM Código FGL 029 Versión 02 Fecha 08-10-2018 La descripción funcional de la arquitectura se puede realizar de varias formas, como se verá más adelante. -- Declaración de entidad entity eFullAdder is port ( X, Y, Ci : in STD_LOGIC; Z, Co : out STD_LOGIC ); end; -- Definición de la arquitectura architecture aFullAdder of eFullAdder is -- zona de declaraciones begin -- zona de descripción funcional end aFullAdder; Código 2.1: Declaración de entidad y cuerpo de la arquitectura del sumador completo de 1 bit. 2.1. Modelado por ujo de datos VHDL es un lenguaje naturalmente concurrente ya que se utiliza para des- cribir circuitos digitales. Esto quiere decir que las instrucciones no se ejecutan secuencialmente como lo hace una CPU, las instrucciones le sirven a la herra- mienta para implementar circuitos sobre una FPGA. Por lo tanto, la herramien- ta usa las instrucciones para sintetizar y diseñar el circuito. Esta característica, ejecución en paralelo de instrucciones, es la utilizada en el modelado por ujo de datos. Este modelado es utilizado para describir circuitos combinacionales1. La sintáxis del modelado por ujo de datos se muestra en (1). destSignal = expresion; (1) La señal destino (destSignal) puede ser de 1 o varios bits, y la expresión (expresion) puede constar de una o varios operadores. Nótese que = es el operador de asignación, el cual asigna a la señal de la izquierda el resulta de la operación de la derecha. En Código 2.2 pueden verse las expresiones para los puertos de salida Z y Co del sumador completo mostrado en la Figura 1. Las operaciones lógicas en VHDL se describen usando palabras en inglés: and y or son obvias, y xor es la operación lógica OR-Exclusive. El lenguaje no es sensible al caso, esto quiere decir que las instrucciones se pueden usar igualmente en minúsculas o mayúsculas. El sumador completo de 1 bit, con unas simples transformaciones, también se puede representar por medio de una tabla de verdad2 (véase Tabla 2). 1Circuitos sin memoria, esto es, la salida actual depende única y exclusivamente de las entradas actuales. 2Diagrama en forma de las y columnas que muestra el valor de las salidas de un circuito digital para todas las posibles combinaciones de las entradas. Página 3 de 13

- 4. GUÍA DE TRABAJO PRÁCTICO - EXPERIMENTAL Talleres y Laboratorios de Docencia ITM Código FGL 029 Versión 02 Fecha 08-10-2018 Esta representación también se puede utilizar para describir el circuito con VHDL usando el modelado por ujo de datos. La descripción mostrada en Có- digo 2.3 representa el circuito de acuerdo a la Tabla 2. -- Declaración de entidad entity eFullAdder is port ( X, Y, Ci : in STD_LOGIC; Z, Co : out STD_LOGIC ); end; -- Definición de la arquitectura architecture aFullAdder of eFullAdder is -- zona de declaraciones begin -- zona de descripción funcional Z = (X xor Y) xor Ci; Co = (X and Y) or ((X or Y) and Ci); end aFullAdder; Código 2.2: sentencias concurrentes en VHDL para el sumador completo de 1 bit. La descripción presentada en Código 2.3 utiliza la instrucción when-else. Esta instrucción es también concurrente y se emplea para asignar un valor a una señal cuando se cumple una condición (when), pero así mismo permite explorar otras posibilidades de la conndición (else). En este caso, la señal o puerto de salida Z tomará el valor de la señal o puerto de entrada Ci cuando las señales o puertos de entrada X y Y sean iguales. Si esta condición no se cumple, Z tomará en valor de Ci. De la misma manera se hace la descripción de la salida C0, la cual es 0 si tanto X como Y son 0, es 1 si ambas, X y Y, son 1, y en los demás casos Co será igual a Ci. Tabla 2: Tabla de verdad del sumador completo de 1 bit. X Y Z Co 0 0 Ci 0 0 1 Ci Ci 1 0 Ci Ci 1 1 Ci 1 2.2. Modelado algorítmico Se emplea para describir circuitos más complejos, como los circuitos secuen- ciales3, empleando sentencias que se ejecutan de manera secuencial. Para esto, 3Circuitos digitales con memoria. Página 4 de 13

- 5. GUÍA DE TRABAJO PRÁCTICO - EXPERIMENTAL Talleres y Laboratorios de Docencia ITM Código FGL 029 Versión 02 Fecha 08-10-2018 las sentencias deben estar dentro de un proceso o un subprograma, el cual a su vez se dene en el cuerpo de la arquitectura del circuito. Los subprogramas sirven para mantener el código más limpio, conciso y libre de duplicaciones, y se declaran, comúnmente, dentro de un paquetes, la arquitectura o un proceso. -- Declaración de entidad entity eFullAdder is port ( X, Y, Ci : in STD_LOGIC; Z, Co : out STD_LOGIC ); end; -- Definición de la arquitectura architecture aFullAdder of eFullAdder is -- zona de declaraciones begin -- zona de descripción funcional Z = Ci when (X = Y) else not(Ci); Co = '0' when (X = '0' and Y = '0') else '1' when (X = '1' and Y = '1') else Ci; end aFullAdder; Código 2.3: sentencias concurrentes en VHDL para el sumador completo de 1 bit. VHDL ofrece dos tipos de subprogramas: las funciones y los procedimientos. Las funciones siempre retornan un valor, los procedimientos no (pero pueden modicar sus parámetros). Ambos tipos de subprogramas pueden tener 0 o más parámetros. En esta guía no nos ocuparemos de los subprogramas. El modelado basado en sentencias secuenciales los realizaremos usando pro- cesos. Pero antes de pasar a los procesos vale aclarar que las sentencias secuen- ciales en VHDL son similares a las sentencias secuenciales de la mayoría de los lenguajes imperativos. Estamos hablando de estructuras de control como el condicional if, la estructura case, los lazos de control como loop, la estructura while, etc. La estructura general de un proceso, en este caso el que describe la tabla de verdad del sumador completo de 1 bit dado en la Tabla 2, puede verse en el Código 2.4. El proceso es una región de código secuencial delimitada por las sentencias process y end process;. Aunque las sentencias dentro del proceso son secuenciales, el proceso es una sentencia concurrente porque se ejecuta en paralelo con los demás procesos y sentencias concurrentes dentro de la arquitectura. En Código 2.4 se pueden observar las principales partes de un proceso, las cuales son: la etiqueta opcional, proSum1Bit, la cual le da el nombre al proceso y además es útil para documentar el software; la lista de sensibilidad X, Y y Ci, Página 5 de 13

- 6. GUÍA DE TRABAJO PRÁCTICO - EXPERIMENTAL Talleres y Laboratorios de Docencia ITM Código FGL 029 Versión 02 Fecha 08-10-2018 la cual es un conjunto de señales que son monitoreadas mientras el proceso está suspendido y que ante un cambio en una de ellas reactiva el proceso, igualmente esta lista es opcional; la palabra reservada is también es opcional y marca el inicio del proceso. -- Declaración de entidad entity eFullAdder is port ( X, Y, Ci : in STD_LOGIC; Z, Co : out STD_LOGIC ); end; -- Definición de la arquitectura architecture aFullAdder of eFullAdder is -- zona de declaraciones begin -- zona de descripción funcional proSum1Bit:process(X,Y,Ci) is begin if (X = '0' and Y = '0') then Z = Ci; Co = '0'; elsif (X = '1' and Y = '1') then Z = Ci; Co = '1'; else Z = not(Ci); Co = Ci; end if; end process; end aFullAdder; Código 2.4: descripción algorítmica utilizando un proceso. Al igual que en la arquitectura que describe una entidad, los procesos tiene una zona de declaraciones del proceso, después de la palabra process y antes de la palabra begin, y una zona de descripción de la funcionalidad, después de la palabra begin. En el proceso proSum1Bit se puede observar el uso de la reconocida sentencia condicional if, de uso corriente en lenguajes de programación de alto nivel y de propósito general, la cual asigna un valor a una o varias señales dependiendo del cumplimiento de unas condiciones. En la primera comparación asigna Ci a Z y 0 a Co cuando tanto X como Y son 0. Si esta condición no se cumple descarta la acción y hace una nueva comparación, para ello usa la sentencia elsif, en la cual si X y Y son ambas 1 a Z le asigna igualmente Ci, pero a Co le asignará 1. Finalmente, si esta condición tampoco se cumple la descarta y no hace más comparaciones, solo asigna Ci y Ci a Z y Co respectivamente. Página 6 de 13

- 7. GUÍA DE TRABAJO PRÁCTICO - EXPERIMENTAL Talleres y Laboratorios de Docencia ITM Código FGL 029 Versión 02 Fecha 08-10-2018 Finalmente, en un proceso no pueden declararse señales, en su lugar se uti- lizan variables, y si no existe lista de sensibilidad el proceso debe suspenderse con una sentencia wait. 2.3. Modelado estructural Describe circuitos interconectando componentes previamente instanciados. Los componentes se interconectan entre ellos por medio de señales declaradas en la arquitectura, y también pueden conectarse sus puertos con los puertos del sistema que los contiene. Vamos a implementar un sumador de 4 bits empleando sumadores completos de 1 bit (véase Figura 1), el cual se representado como una caja negra en la Figura 2. Podemos emplear cualquiera de las descripciones del sumador de 1 bit presentadas en esta guía, esto es, Código 2.2, 2.3 o 2.4, para su implementación. Ž ŝ z y ^ƵŵĂĚŽƌϭŝƚ Figura 2: Descripción de los puertos de entrada/salida de un sumador de 1 bit. En la Figura 3 se pueden ver la implementación de un sumador de 4 bit, Sum4Bit, usando sumadores de 1 bit. Nótese que en este caso se implementó una sola vez el sumador de 1 bit y se utiliza, léase se instancia, cuatro veces para construir el sumador de 4 bit. Esto demuestra lo poderosa que es la arquitectura estructural, basada en componentes, y la optimización que se obtiene en tiempo de desarrollo. En el sistema integrador, Sum4Bit, se deben denir los puertos de entrada- salida del sumador de 4 bit, esto es, dos vectores de entrada de 4 bis, X y Y, un vector de salida de 4 bit, Z, una señal de entrada de 1 bit, Ci, y una señal de salida de 1 bit, Co. La arquitectura de Sum4Bit está formada por la interconexión de cuatro subcircuitos, que en VHDL se describen como componentes (sum1Bit). Estos componentes se declaran en la zona de declaraciones de la arquitectura, iniciando con la palabra component y nalizando con end component;. En medio de estas dos palabras va la descripción de los puertos del componente, tal como se hace en la declaración de la entidad. Se asume que la descripción de la arquitectura del componente existe en un archivo aparte. Las señales que unen los componentes se deben igualmente declarar en la zona de declaraciones de la arquitectura, utilizando la palabra signal y el tipo de dato que soportan. No se debe indicar la dirección de la señal, ya que debido a que estas ni entran ni salen de Sum4Bit no se consideran ni de entrada ni de salida. Las señales dentro de sum4Bit que conectan las instancias de sum1Bit, dibujadas en color rojo, son Ci1, Ci2 y Ci3. Los cuatro componentes son utilizados en la implementación cuando se ins- tacian en la zona de la descripción funcional de la arquitectura. Los puertos de cada componente, sum1Bit, se relacionan con los del sistema integrador, Página 7 de 13

- 8. GUÍA DE TRABAJO PRÁCTICO - EXPERIMENTAL Talleres y Laboratorios de Docencia ITM Código FGL 029 Versión 02 Fecha 08-10-2018 Sum4Bit, o con una señal declarada allí usando el operador =. Antes del ope- rador = se pone el puerto del componente, y después del operador = se pone el puerto o la señal del componente integrador. Ž ŝ z y ^Ƶŵϭŝƚ Ž ŝ z y ^Ƶŵϭŝƚ Ž ŝ z y ^Ƶŵϭŝƚ Ž ŝ z y ^Ƶŵϭŝƚ y Ϯ z Ϯ y ϭ z ϭ y Ϭ z Ϭ y ϯ z ϯ Ž ŝ Ϯ ϯ Ϭ ϭ ŝϭ ŝϮ ŝϯ ^Ƶŵϰŝƚ Figura 3: Descripción de los puertos de entrada/salida y las señales de un su- mador de 4 bit. La instacia inicia con una etiqueta que le da un nombre, por ejemplo, para el caso del primer sumador de 1 bit el nombre de esta instancia es i0_sum1Bit. El nombre de la instacia se separa del nombre del componente usando :, luego del nombre del componente sigue la instrucción port map y en paréntesis la relación entre los puertos del componente y los puertos y señales denidas dentro del sistema integrador. Como todas las instrucciones en VHDL, la instancia naliza con ;. Por ejemplo, la relación X = X(0) signica que el puerto X del componente, i0_sum1Bit, es el bit 0 del puerto X, que es un vector de 4 bits, denido en el sistema integrador, sum4Bit; y la relación Co = Ci1 signica que el puerto Co del componente i0_sum1Bit es la misma señal Ci1 declarada en la arquitectura del sistema integrador, sum4Bit. De esta misma forma se puede hacer la relación entre los puertos de cada instancia del componente sum1Bit y los puertos y señales del sistema integrador Sum4Bit. El código 2.5 muestra la implementación estructural del sumador de 4 bits a partir de sumadores de 1 bit y de acuerdo a el diagrama de bloques mostrado en la Figura 3. Se puede utilizar esta misma losofía de diseño estructural para implementar, por ejemplo, un sumador de 16 bit. El diagrama de bloques es básicamente igual al de la Figura 3, solo que los componentes son sumadores de 4 bit, sum4Bit, y no de 1 bit, sum1Bit. Por lo tanto, se deben reemplazar cada puerto Xi, Yi y Zi por vectores de cuatro bit. Por ejemplo, en lugar de X0 deben ir los cuatro bits de menor peso del vector de 16 bit X, esto es, X(3 downto 0). De la misma manera, se puede implementar un sumador de 64 bits con componentes sumadores de 16 bits. Se alienta a los estudiantes a que intenten implementar un sumador de 64 bits a partir de componentes sumadores de 16 bits. Página 8 de 13

- 9. GUÍA DE TRABAJO PRÁCTICO - EXPERIMENTAL Talleres y Laboratorios de Docencia ITM Código FGL 029 Versión 02 Fecha 08-10-2018 library IEEE; use IEEE.STD_LOGIC_1164.ALL; entity sum4Bit is Port (X, Y : in STD_LOGIC_VECTOR (3 download 0); Ci : in STD_LOGIC; Z : out STD_LOGIC_VECTOR (3 download 0); Co : out STD_LOGIC); end sum4Bit; architecture structural of sum4Bit is component sum1Bit is Port (X, Y, Ci : in STD_LOGIC; Z, Co : out STD_LOGIC); end component sum1Bit; signal Ci1, Ci2, Ci3 : STD_LOGIC; begin i0_sum1Bit:sum1Bit port map(X = X(0), Y = Y(0), Ci = Ci, Z = Z(0), Co = Ci1); i1_sum1Bit:sum1Bit port map(X = X(1), Y = Y(1), Ci = Ci1, Z = Z(1), Co = Ci2); i2_sum1Bit:sum1Bit port map(X = X(2), Y = Y(2), Ci = Ci2, Z = Z(2), Co = Ci3); i3_sum1Bit:sum1Bit port map(X = X(3), Y = Y(3), Ci = Ci3, Z = Z(3), Co = Co); end structural; Código 2.5: Implementación estructural de sumador de 4 bit a partir de suma- dores de 1 bit.. 3. OBJETIVO(S) Implementar con arquitectura estructural una ALU de 4 bits usando VHDL sobre FPGA. 4. RECURSOS REQUERÍDOS Estación de trabajo. Vivado Design Suite. Nexys 4 o Nexys A7. Página 9 de 13

- 10. GUÍA DE TRABAJO PRÁCTICO - EXPERIMENTAL Talleres y Laboratorios de Docencia ITM Código FGL 029 Versión 02 Fecha 08-10-2018 5. PROCEDIMIENTO O METODOLOGÍA PA- RA EL DESARROLLO Una ALU (Aritmethic Logic Unit) es un circuito digital combinacional que realiza múltiples operaciones, algunas aritméticas y algunas lógicas. La Figura 4 muestra los puertos de entradasalida de una ALU de 4 bits. Este circuito realiza las operaciones aritméticas y lógicas descritas en la Tabla 3 sobre los operandos, de 4 bits, A y B de acuerdo a las líneas de selección, de 3 bits, S. El resultado se almacena en la señal F de 4 bits. Ci y Co son los acarreros de entrada y salida respectivamente utilizados en las operaciones aritméticas. hŶŝĚĂĚſŐŝĐŽƌŝƚŵĠƚŝĐĂ h ϯ… Ϭ ϯ… Ϭ ϯ… Ϭ ^Ϯ… ^Ϭ ŝ Ž Figura 4: ALU de 4 bits. Tabla 3: Funciones de la ALU de 4 bits. Selección Salida Función S2 S1 S0 Ci 0 0 0 0 F = A Tranferir A 0 0 0 1 F = A plus 1 Incrementar A 0 0 1 0 F = A plus B Suma 0 0 1 1 F = A plus B plus 1 Suma con acarreo 0 1 0 0 F = A minus B minus 1 Resta con préstamo 0 1 0 1 F = A minus B Resta 0 1 1 0 F = A minus 1 Decrementar 0 1 1 1 F = A Transferir A 1 0 0 X F = A + B OR 1 0 1 X F = A ⊕ B OR exclusiva 1 1 0 X F = A · B AND 1 1 1 X F = Ā Complementar A La ALU puede ser vista como la unión de dos etapas, un circuito aritmético y un circuito lógico (véase Figura 5), donde S2 selecciona si a la salida pasa el resultado de la etapa aritmética, Fx, o el de la etapa lógica, Fy. S1 y S0 seleccionan la operación interna que cada etapa debe realizar. Página 10 de 13

- 11. GUÍA DE TRABAJO PRÁCTICO - EXPERIMENTAL Talleres y Laboratorios de Docencia ITM Código FGL 029 Versión 02 Fecha 08-10-2018 ŝƌĐƵŝƚŽƌŝƚŵĠƚŝĐŽ ŝƌĐƵŝƚŽſŐŝĐŽ DƵdžϮĂϭ ϯ… Ϭ ϯ… Ϭ ^ϭ…^Ϭ džϯ… džϬ LJϯ… LJϬ ϯ…Ϭ Ž ŝ ^Ϯ Figura 5: Etapas de la ALU, circuito artitmético y lógico. 5.1. Diseño del circuito aritmético Este circuito puede ser implementado usando un sumador de 4 bits, como el presentado en esta guía (véase Código 2.5), y un multiplexor 4 a 1 de 4 bits. El multiplexor 2 a 1 de 1 bit presentado en la guía No 1 puede utilizarse como base para la implementación de este multiplexor de 4 bits. La Figura 6 muestra el diseño del circuito aritmético y la Tabla 4 las operaciones realizadas por este. ^ƵŵĂĚŽƌĚĞ ϰďŝƚƐ ϬϬϬϬ ϭϭϭϭ ϯ…Ϭ Ε;ϯ… ϬͿ ^ϭ… ^Ϭ ϯ… Ϭ ŝ Ž džϯ… džϬ yϯ… yϬ DƵdžϰĂϭ Figura 6: Circuito aritmético de la ALU. Tabla 4: Opearciones del circuito aritmético de la ALU de 4 bits. Selección Salida mux Salida Función S1 S0 Ci 0 0 0 X = 0000 Fx = A Tranferir A 0 0 1 X = 0000 Fx = A plus 1 Incrementar A 0 1 0 X = B Fx = A plus B Suma 0 1 1 X = B Fx = A plus B plus 1 Suma con acarreo 1 0 0 X = B̄ Fx = A plus B̄ Resta con préstamo 1 0 1 X = B̄ Fx = A plus B plus 1 Resta 1 1 0 X = 1111 Fx = A plus 1111 Decrementar A 1 1 1 X = 1111 Fx = A plus 1111 plus 1 Transferir A Página 11 de 13

- 12. GUÍA DE TRABAJO PRÁCTICO - EXPERIMENTAL Talleres y Laboratorios de Docencia ITM Código FGL 029 Versión 02 Fecha 08-10-2018 5.2. Diseño del circuito lógico El circuito lógico puede ser implementado de manera sencilla usando un multiplexor 4x1 de 4 bits como se ve en la Figura 7. Se puede utilizar el mismo multiplexor 4 a 1 implementado para el circuito aritmético. ^ϭ… ^Ϭ DƵdžϰĂϭ ϯ… Ϭ ϯ… Ϭ LJϯ… LJϬ Figura 7: Circuito lógico de la ALU. 6. PARÁMETROS PARA ELABORACIÓN DEL INFORME El docente facilitará una plantilla en Word para escribir el informe. Si los estudiantes lo desean pueden utilizar L ATEX empleando los mismos parámetros de la plantilla propuesta para el curso. 7. DISPOSICIÓN DE RESIDUOS Esta práctica no genera residuos. Referencias R. Jasinski, Eective Coding with VHDL: principles and best practice, The MIT Press, Cambridge, MA., 2016. S.K. Sarkar, A.K. De, S. Sarkar, Fundation of Digital Electronics and Logic Design, Pan Stanford Publishing, Singapore, 2014. R.L. Tokheim, Electrónica digital : principios y aplicaciones, McGraw-Hill Interamericana, México, 2008. J.I. Artigas Maestre, L.Á. Barragán Pérez, C. Orrite Uruñuela, I. Urriza Parroqué, Electrónica digital : aplicaciones y problemas con VHDL, Prentice Hall, Madrid, 2002. R. Reina Acedo, M. García Lorenz, J. Vázquez Martínez, Electrónica digital en la práctica, Alfaomega, México, 2011. V.A. Pedroni, Circuit design and simulation with VHDL, MIT Press, Cambridge, MA., 2010. Página 12 de 13

- 13. GUÍA DE TRABAJO PRÁCTICO - EXPERIMENTAL Talleres y Laboratorios de Docencia ITM Código FGL 029 Versión 02 Fecha 08-10-2018 C.H. Roth, L.L. Kinney, Fundamentals of logic design, Cengage Lear- ning, EEUU, 2010. Elaborado por: Sergio Ignacio Serna Garcés, Ph.D. Revisado por: Pendiente Versión: 1.0 Fecha: Septiembre 2021 Página 13 de 13