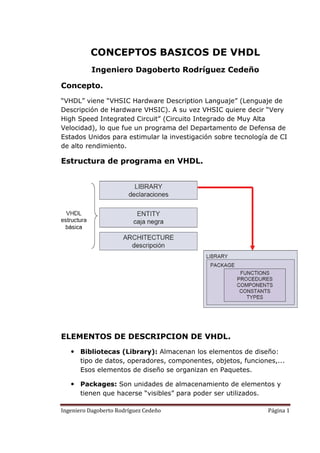

El documento presenta una introducción a los conceptos básicos de VHDL. Explica que VHDL es un lenguaje de descripción de hardware usado para modelar circuitos digitales. Describe los elementos clave de VHDL como bibliotecas, paquetes, entidades, arquitecturas, tipos de datos y operadores. También explica los diferentes tipos de diseño en VHDL como estructural, comportamental y por flujo de datos, así como herramientas de diseño asistido por ordenador para VHDL.