INTERRUPCIONES.ppt

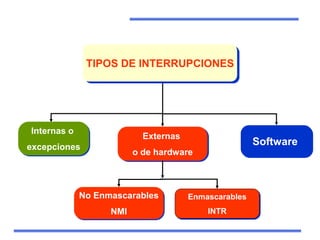

- 1. TIPOS DE INTERRUPCIONES Internas o excepciones Externas o de hardware Software No Enmascarables NMI Enmascarables INTR

- 2. La tabla de vectores de interrupción contiene las direcciones de las rutinas de servicio de las interrupciones que realizan las funciones asociadas con las interrupciones. Las rutinas del POST del BIOS inicializa la tabla de vectores, al momento de “bootear”, con las direcciones de las rutinas suministradas por el código en la ROM BIOS y después el DOS y nuestros programas de aplicación agregan sus respectivos vectores a los vectores de esta tabla, conforme son cargados.. TABLA DE VECTORES DE INTERRUPCIÓN

- 3. CSL CSH IPL IPh 0000 3FFF Tabla de vectores de interrupción Se ubica en 1024 localidades de RAM en la parte más baja de la memoria que permiten 256 vectores de interrupción de 4 bytes cada uno. Un vector de interrupción está formado por la dirección de inicio de la rutina de servicio de la interrupción ISR ( 2 bytes para CS y 2 bytes para IP) Vector 0 0001 0002 0003 LA TABLA DE VECTORES DE INTERRUPCIÓN

- 4. LA TABLA DE VECTORES DE INTERRUPCIÓN Cada vector: 4 bytes Dirección del vector: 0: INT x 4 La tabla ocupa 256x4 = 1024 bytes (1 Kbyte) Reservadas por INTEL (modo protegido) Error de división por 0 Ejecución paso a paso NMI (No enmascarable) Instrucción INT Desbordamiento (INTO) Utilizables por el usuario

- 5. Cuando una interrupción ocurre, independientemente de la fuente, el 80x86 realiza lo siguinte: 1) El CPU carga (push) el registro de banderas al STACK 2) La CPU carga al STACK la dirección de retorno lejano ( segmento:offset ) primero el valor del segmento. 3) La CPU determina la causa de la interrupción ( esto es, lee el número o tipo de la interrupción) y toma los 4 bytes del vector de interrupción de la dirección 0000:vector*4. 4) La CPU transfiere el control a la rutina especificada por la tabla de vectores de interrupción. Después de completados estos pasos,la rutina de servicio de la interrupción toma el control. Cuando la interrupción desea regresar el control , debe ejecutar una instrucción IRET ( Interrupt Return). El retorno de una interrupción recupera del STACK la dirección de retorno lejano y las banderas.

- 6. Operación de las instrucciones INT e IRET Int 16H 00 2E EB 04 00 15 09 0915:0002 0915:0003 0915:0004 F000:EB2E F000:E82F IRET 0000:0000 F0 0000:0058 0000:0059 0000:005A 0000:005B FLAGS PROGRAMA INVOCANTE STACK TABLA DE VECTOR DE INTERRUPCIONES RUTINA DE LA ROM BIOS 1 2 3 4 IRET produce un retorno de la rutina de interrupción al programa invocante, recuperando del STACK la dirección CS:IP de la instruccón que quedó pendiente INT 16h produce un FAR CALL a la dirección contenida en el vector de la interrupción 16h, la dirección de retorno se carga al STACK

- 7. Int. Num. Address in I.V.T. Description 0 00-03 CPU divide by zero 1 04-07 Debug single step 2 08-0B Non Maskable Interrupt (NMI input on processor) 3 0C-0F Debug breakpoints 4 10-13 Arithmetic overflow 5 14-17 BIOS provided Print Screen routine 6 18-1B Reserved 7 1C-1F Reserved 8 20-23 IRQ0, Time of day hardware services 9 24-27 IRQ1, Keyboard Interface A 28-2B IRQ2, ISA Bus cascade services for second 8259 B 2C-2F IRQ3, Com 2 hardware C 30-33 IRQ4, Com1 hardware DESCRIPCIÓN DE LA TABLA DE VECTORES DE INTERRUPCIÓN Y SU TIPO

- 8. Time of day services 68-6B 1A Bootstrap loader 64-67 19 Points to basic interpreter in a "real" IBM PC 60-63 18 Printer I/O routines 5C-5F 17 Keyboard I/O routines 58-5B 16 PC used for Cassette tape services 54-57 15 Serial port I/O routines 50-53 14 Floppy I/O routines 4C-4F 13 Memory size determination 48-4B 12 Equipment check 44-47 11 Video services, see note 1 40-43 10 IRQ7, LPT1, Parallel port hardware 3C-3F F IRQ6, Floppy Disk adaptor 38-3B E IRQ5, LPT2, Parallel port hardware (Hard Disk on XT) 34-37 D

- 9. Read logical sectors 94-97 25 Critical error handler 90-93 24 Ctrl-Break exit address 8C-8B 23 Terminate address 88-8B 22 All DOS services available through this Interrupt 84-87 21 Program termination (obsolete) 80-83 20 Video graphics 7C-7F 1F Disk parameters 78-7B 1E Video parameters 74-77 1D Timer tick (provides 18.2 ticks per second) 70-73 1C Services Ctrl-Break service 6C-6F 1B

- 10. Used for EMS functions 19C-19F 67 Reserved for User programs 180-183 to 198-19B 60 to 66 Reserved for BIOS 17C-17F 5F Reserved for BIOS 178-17B 5E Reserved for BIOS 174-177 5D Reserved for BIOS 16C-16F 5B Reserved for BIOS 168-16B 5A Reserved for BIOS 148-14B to 164-167 52 to 59 Mouse functions 144-147 51 Reserved for BIOS 140-143 50 Reserved for BIOS 100-103 to 13C-13F 40 to 4F Reserved for DOS A0-A3 to FC-FF 28 to 3F Terminate and stay resident routines (obsolete) 9C-9F 27 Write logical sectors 98-9B 26

- 11. Unused 3C4-3C7 to 3C4-3FF F1 to FF Used by basic 218-21B to 3C0-3C3 86 to F0 Reserved for basic 200-203 to 214-217 80 to 85 Unused 1E0-1E3 to 1FC-1FF 78 to 7F IRQ15, (available hardware interrupt) 1DC-1DF 77 IRQ14, ISA bus hard disk controller 1D8-1DB 76 IRQ13, maths co-processor 1D4-1D7 75 IRQ12 (available hardware interrupt) 1D0-1D3 74 IRQ11 (available hardware interrupt) 1CC-1CF 73 IRQ10 (available hardware interrupt) 1C8-1CB 72 IRQ9, takes the place of IRQ2 1C4-1C7 71 IRQ8, ISA bus Real time clock 1C0-1C3 70 Unused 1A0-1A3 to 1BC-1BF 68 to 6F

- 12. La familia de microprocesadores 8086 pueden reconocer 256 diferentes interrupciones, cada una con un código único de TIPO (número) con el que el microprocesador lo identifica. El procesador usa este código de TIPO ( un número entre 00 y FF en hexadecimal ) para apuntar a una localidad dentro de la tabla de vectores de interrupción. EN GENERAL:

- 13. Termina la instrucción en curso Interrupción interna Ejecuta la Siguiente instrucción NMI INTR TF IF Interrupción reconocida Lee código de tipo Push flags Let temp=TF Clear IF&TF Push CS&IP NMI TEMP Ejecuta ISR Pop IP&CS Pop flags Continua con el programa SI SI SI SI 1 1 1 0 0 Call ISR La CPU no puede dejar una instrucción a medio ejecutar, sensa las interrupciones en el último ciclo de máquina de la instrucción en curso y responde al finalizar la instrucción en curso

- 14. •INT 0: error de división, generada automáticamente cuando el cociente no cabe en el registro o el divisor es cero. Sólo puede ser generada mediante DIV o IDIV. •INT 1: paso a paso, se produce tras cada instrucción cuando el procesador está en modo traza (utilizada en depuración de programas). •INT 2: interrupción no enmascarable, tiene prioridad absoluta y se produce incluso aunque estén inhibidas las interrupciones (con CLI) para indicar un hecho muy urgente (fallo en la alimentación o error de paridad en la memoria). INTERRUPCIONES INTERNAS O EXCEPCIONES: Las genera la propia CPU cuando se produce una situación anormal o cuando llega el caso. Por desgracia, IBM se saltó olímpicamente la especificación de Intel que reserva las interrupciones 0-31 para el procesador.

- 15. •INT 3: utilizada para poner puntos de ruptura en la depuración de programas, debido a que es una instrucción de un solo byte muy cómoda de utilizar. •INT 4: desbordamiento, se dispara cuando se ejecuta un INTO y había desbordamiento. •INT 5: rango excedido en la instrucción BOUND (sólo 286 y superiores). Ha sido incorrectamente empleada por IBM para volcar la pantalla por impresora. •INT 6: código de operación inválido (sólo a partir del 286). Se produce al ejecutar una instrucción indefinida, en la pila se almacena el CS:IP de la instrucción ilegal. •INT 7: dispositivo no disponible (sólo a partir del 286). INTERRUPCIONES INTERNAS O EXCEPCIONES:

- 16. Producidas por el propio programa usando la instrucción INT para invocar ciertas subrutinas. La BIOS y el DOS utilizan algunas interrupciones a las que se puede llamar con determinados valores en los registros para que realicen ciertos servicios. INTERRUPCIONES DE SOFTWARE:

- 17. INTERRUPCIONES EXTERNAS O DE HARDWARE: • Son generadas por dispositivos periféricos externo a través de una señal eléctrica. • Se solicita la atención de la CPU aplicándole la señal a sus terminales INT y NMI • Las Enmascarables por INT : activa a nivel alto • Las No Enmacarables por NMI: activa en flanco de subida

- 18. La CPU genera dos impulsos de reconocimiento de interrupción INTR NMI INTA CPU INTERRUPCIONES EXTERNAS O DE HARDWARE:

- 19. INTERRUPCIONES EXTERNAS O DE HARDWARE: INTERRUPCIONES ENMASCARABLES SE HABILITAN O DESHABILITAN POR PROGRAMA: Con la instrucción SETI se habilitan las interrupciones y pone la bandera IF a 1 Con la instrucción CLI se inhiben todas las posibles interrupciones de este tipo y se pone la bandera IF a 0. LA CPU RESPONDE AL SER ACEPTADA LA INTERRUPCIÓN, CON UNA SEÑAL EN SU TERMINAL INTA ( INTERRUPT ACNOWLWDGE)

- 20. INTERRUPCIONES EXTERNAS O DE HARDWARE: son solicitadas por periféricos externos, a través de un Controlador de interrupciones programable ( Programmable Interrupts Controller : PIC) que se conecta a la terminal INT del mprocesador, La aceptación o no depende del status de la bandera de interrupciones IF INTERRUPCIONES ENMASCARABLES:

- 21. La IBM PC original usó el controlador de interrupciones 8259. Este permitía que se pudieran generen hasta 8 señales de interrupción ( numeradas de 0 a 7). Estas líneas de interrupción son llamadas líneas de “Interrupt Request” ( requerimiento de interrupción) o IRQ´s

- 22. A partir de la IBM AT se incluyen 2 controladores de interrupción, donde el segundo controlador (ESCLAVO) está conectado en cascada a la línea de interrupción 2 del primer controlador ( MAESTRO) . L a líneas de interrupción del segundo controlador están numeradas de 8 a 15. Debido a este “cascadeo”, la línea de interrupción 2 no está disponible. Sin embargo ; para compatibilidad con la PC original, la línea de interrrupción 2 es conectada a al línea 9 del segundo controlador ( tal que, si un dispositivo en la PC es configurado para la interrupción 2, en realidad éste usa la interrupción 9)

- 23. Interrupciones reservadas: IRQ0 Temporizador (Timer) IRQ1 Teclado IRQ8 Reloj de tiempo real IRQ13 Errores del coprocesador IRQ14 Controlador de disco duro IRQ3 Puerto serie COM1 IRQ4 Puerto serie COM2 IRQ6 Controlador de diskette IRQ7 Puerto paralelo PIC MAESTRO Dir E/S = 20h, 21h PIC ESCLAVO Dir E/S = A0h, A1h Al inicio del sistema se especifica: PIC MAESTRO INT = IRQ + 8 PIC ESCLAVO INT = IRQ + 70h

- 24. Entradas del controlador programable de interrupciones PIC 8259

- 25. El PIC 8259 (“Programmable Interrupt Controller”) ESQUEMA INTERNO DE BLOQUES

- 26. El PIC 8259 (“Programmable Interrupt Controller”) El registro de máscara Permite enmascarar individualmente cada entrada: 1 Prohibe interrupciones por esa línea 0 Permite interrupciones por esa línea

- 27. El PIC 8259 (“Programmable Interrupt Controller”) Proceso de una interrupción en el PIC 1. Un periférico solicita interrupción 2. El PIC solicita interrupción a la CPU (INT) 3. La CPU reconoce la petición con un primer pulso de INTA 4. Se activa el bit correspondiente de ISR y se desactiva en IRR

- 28. El PIC 8259 (“Programmable Interrupt Controller”) 5. La CPU envía el segundo pulso de INTA 6. El PIC coloca un puntero de 8 bits en el bus de datos •El valor del puntero es distinto para cada entrada IRQ •Es programable 7. A partir de entonces comienza a ejecutarse la rutina de atención Proceso de una interrupción en el PIC (continuación)

- 29. El PIC 8259 (“Programmable Interrupt Controller”) Fin de interrupción (EOI) Los bits activos de ISR bloquean futuras peticiones por esa línea

- 30. El PIC 8259 (“Programmable Interrupt Controller”) Deben ponerse a 0 al terminar la rutina de servicio: (EOI) Formas de poner a 0 el bit de ISR: 1. Programar el modo automático (AEOI) El bit se pone a 0 automáticamente al colocar el puntero en el bus de datos 2. Enviar al PIC el comando EOI: No específico : pone a 0 el de más prioridad Específico: pone a 0 el que se le indica Generalmente se envía el EOI justo antes del IRET Fin de interrupción (EOI)

- 31. El PIC 8259 (“Programmable Interrupt Controller”)

- 32. Los PICs se conectan al sistema a través de Los puertos de E/S 20h/A0h y 21h/A1h. La primera dirección es la dirección del PIC maestro (IRQ0-IRQ7), la segunda corresponde al PIC esclavo (IRQ8-IRQ15). La 20h/A0h es una localidad de lectura/escritura a la cual se escriben comandos al PIC y se lee su status, nos referiremos a éste como el registro de comandos o el registro de status. EL registro de comandos es de sólo escritura y el de status es de sólo lectura . Ellos solo comparten la misma localidad de E/S. Las líneas de READ/WRITE del PIC determina que registro va a accesar el CPU. EL puerto 21h/A1h es una localidad de lecto/escritura que contiene el registro máscara de interrupción. CONEXIÓN DE LOS CONTROLADORES PROGRAMABLES DE INTERRRUPCIÓN (PIC) 8259 A LA PC

- 33. Registro de máscara de Interrupción del PIC El registro de máscara del PIC es un registro de 8 bits que nos permite habilitar y deshabilitar individualmente las interrupciones de los dispositivos del sistema. Esto es similar a las acciones de las instrucciones CLI y STI, pero sobre un dispositivo Para deshabilitar la interrupción de algún dispositivo específico, escriba un uno al registro de máscara Para habilitar la interrupción de algún dispositivo específico, escriba un cero al registro de máscara

- 34. INTERRUPCIONES DEL BIOS SERVICIO A DISPOSITIVOS PERIFÉRICOS..............(6) STATUS DEL EQUIPO..................................................(2) HORA Y FECHA...........................................................(1) PRINT SCREEN...........................................................(1) SERVICIOS ESPECIALES............................................(2)

- 35. INTERRUPCIONES DEL BIOS SERVICIO A DISPOSITIVOS PERIFÉRICOS: INT 10H............................................SERVICIO DEL VIDEO INT 13H............................................SERVICIOS DE DISKETTE INT 14H............................................COMUNICACIONES INT 15H............................................SERVICIOS DEL SISTEMA INT 16H............................................SERVICIOS DEL TECLADO INT 17H............................................SERVICIOS DE IMPRESORA

- 36. INTERRUPCIONES DEL BIOS STATUS DEL EQUIPO: INT 11H............................................LISTADO DEL EQUIPO INT 12H............................................TAMAÑO DE MEMORIA HORA Y FECHA: INT 1AH............................................HORA Y FECHA PRINT SCREEN: INT 5H.............................................IMPRESIÓN DE PANTALLA INT 18H...........................................ACTIVAR LA BASIC-ROM SERVICOS ESPECIALES: INT 19H...........................................ACTIVAR RUTINA DE ARRANQUE CARGADO

- 37. Función 02 de la INT 10H del BIOS Colocación del cursor INT 10H DEL BIOS AH=02 BH=00 DH = renglón Colocación del cursor DL = columna 76 77 78 79 Ejemplo:Colocar al cursor en las posiciones (DL,DH)=(12,40) MOV AH,02H ;invocar a la función 2 de la INT 10h MOV BH,00 ;trabajar con la página 0 MOV DH,12 ;cargar el #de columna en DH MOV DL,40 ;cargar el # de renglón en DL INT 10H ;Invocar a la rutina del BIOS 0 1 2 22 23 24 0123 Renglón 0 Columna 0 Renglón 0 Columna 79 Renglón 24 Columna 79 Renglón 24 Columna 0 DH DL Renglón 12 Columna 40

- 38. Función 06 de la INT 10H del BIOS INT 10H DEL BIOS AH=06 AL=00 BH=# de atributo CX=renglón:columna(inicio) DX=renglón:columna ( final ) Limpiar la pantalla 00:00 18:4F Dx posición final Cx posición inicial Limpiar la pantalla BH=atributo de la pantalla ejemplo: 7=blanco 1=azul AL=00; Pantalla completa

- 39. Atributos de la pantalla Cada carácter de la pantalla monocromática tiene su propio atributo: parpadeante o no intensificado o no video normal o inverso. Cada posición de un carácter en la pantalla (25X80=2000 ) es representado por 2 bytes: El primero es el ASCII del caracter El segundo es el byte que contiene el atributo b7 b6 b5 b4 b3 b2 b1 b0 BH: Foreground 000=negro 001=azul 010=verde 011=cian 100=rojo 101=magenta 110=café 111=blanco Intensidad 0= normal 1=intensificado Background 000=negro 001=azul 010=verde 011=cian 100=rojo 101=magenta 110=café 111=blanco Parpadeo 0= normal 1=parpadeante El atributo se carga al registro BH

- 40. SERVICIOS DE LA INT 14H DEL BIOS MANEJO DEL PUERTO SERIAL Servicio Descripción __________________________________________ 00 Inicializa el puerto serial 01 Envía un carácter 02 Recibe un carácter 03 Lee el status del puerto serie 04 Inicializa el puerto serie extra 05 Control del puerto de comunc.

- 41. SERVICIO 00 DE LA INT 14H : INICIALIZACIÓN DEL PUERTO SERIAL ACTIVA LOS PARAMETROS SIGUIENTES: _________________________________________ EL BAUDAJE LA PARIDAD EL NÚMERO DE STOPS BITS EL TAMAÑO EN BITS DEL DATO

- 42. SERVICIOS DE LA INT 14H DEL BIOS SERVICIO 00h:INICIALIZACIÒN DEL PUERTO SERIAL b7 b6 b5 b4 b3 b2 b1 b0 Tamaño del dato # de stops bits Código de paridad Código de baudaje Baudaje _________ 765 bps _________ 000 110 001 150 010 300 011 600 100 1200 101 2400 110 4800 111 9600 Paridad ________________ 43 significado ________________ 00 ninguna 01 Paridad impar 10 ninguna 11 Paridad par Stop bits _____________ bit2 significado _____________ 0 1stop bit 1 2 stops bits Tamaño del dato ____________ 10 significado ____________ 00 No usado 01 No usado 10 7 bits 11 8 bits