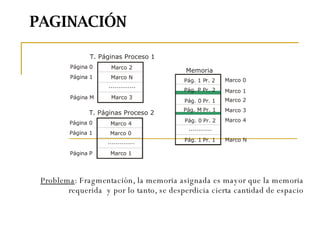

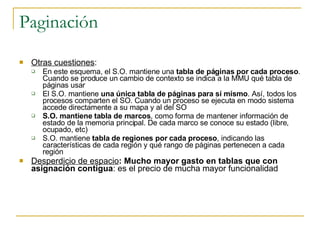

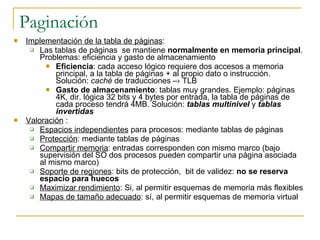

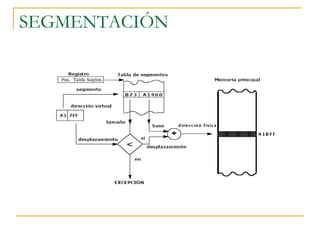

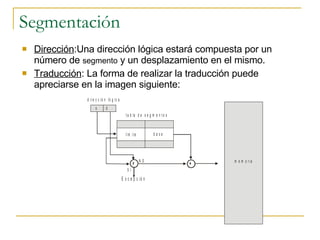

El documento describe diferentes métodos de asignación no continua de memoria, incluyendo paginación, segmentación y memoria virtual. Explica cómo funciona cada método a nivel de hardware mediante tablas, y cómo permiten protección, compartición de memoria y soporte de regiones. También analiza ventajas e inconvenientes de cada método con respecto a fragmentación, rendimiento y ajuste del tamaño de los mapas de memoria de los procesos.