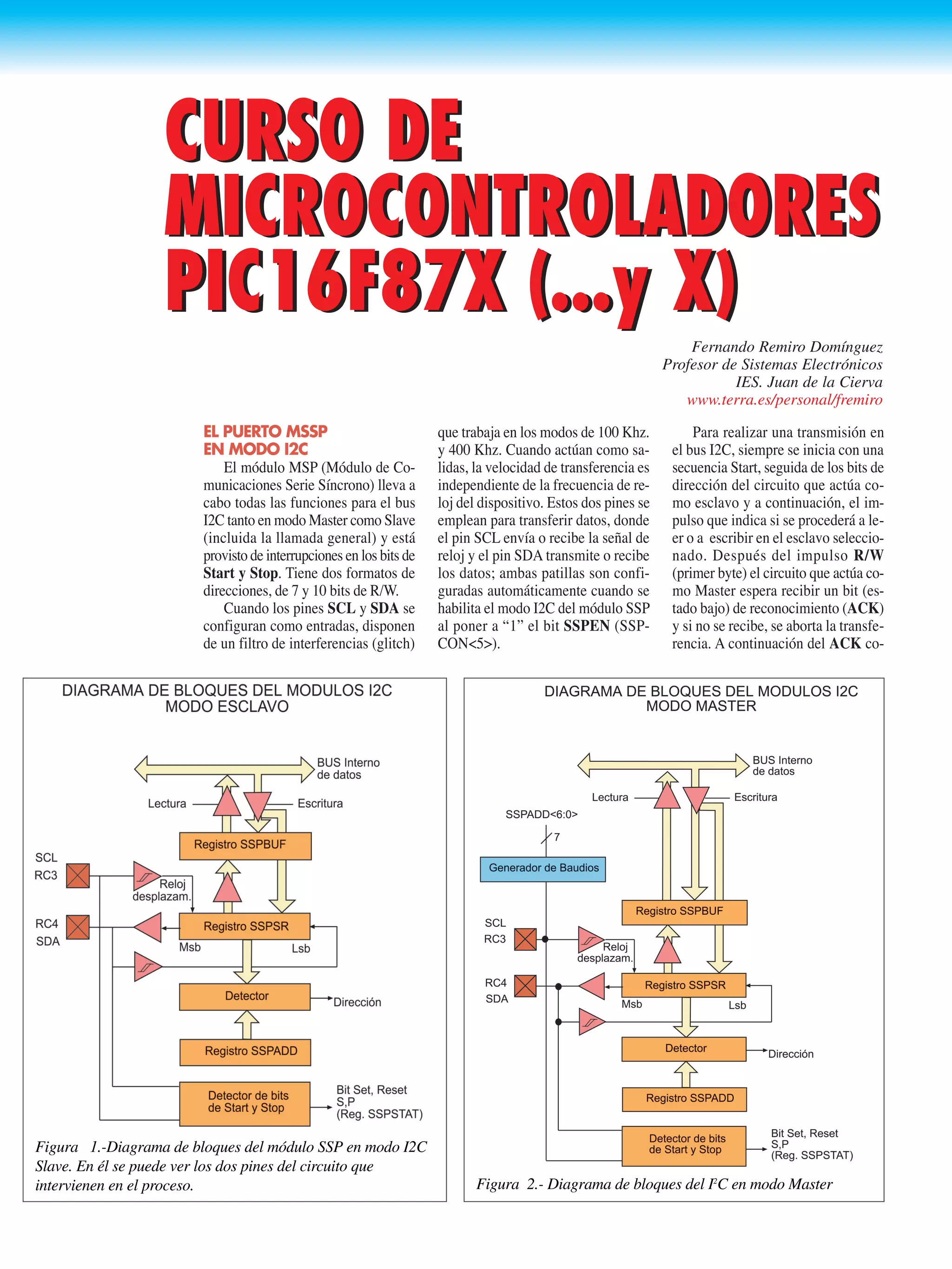

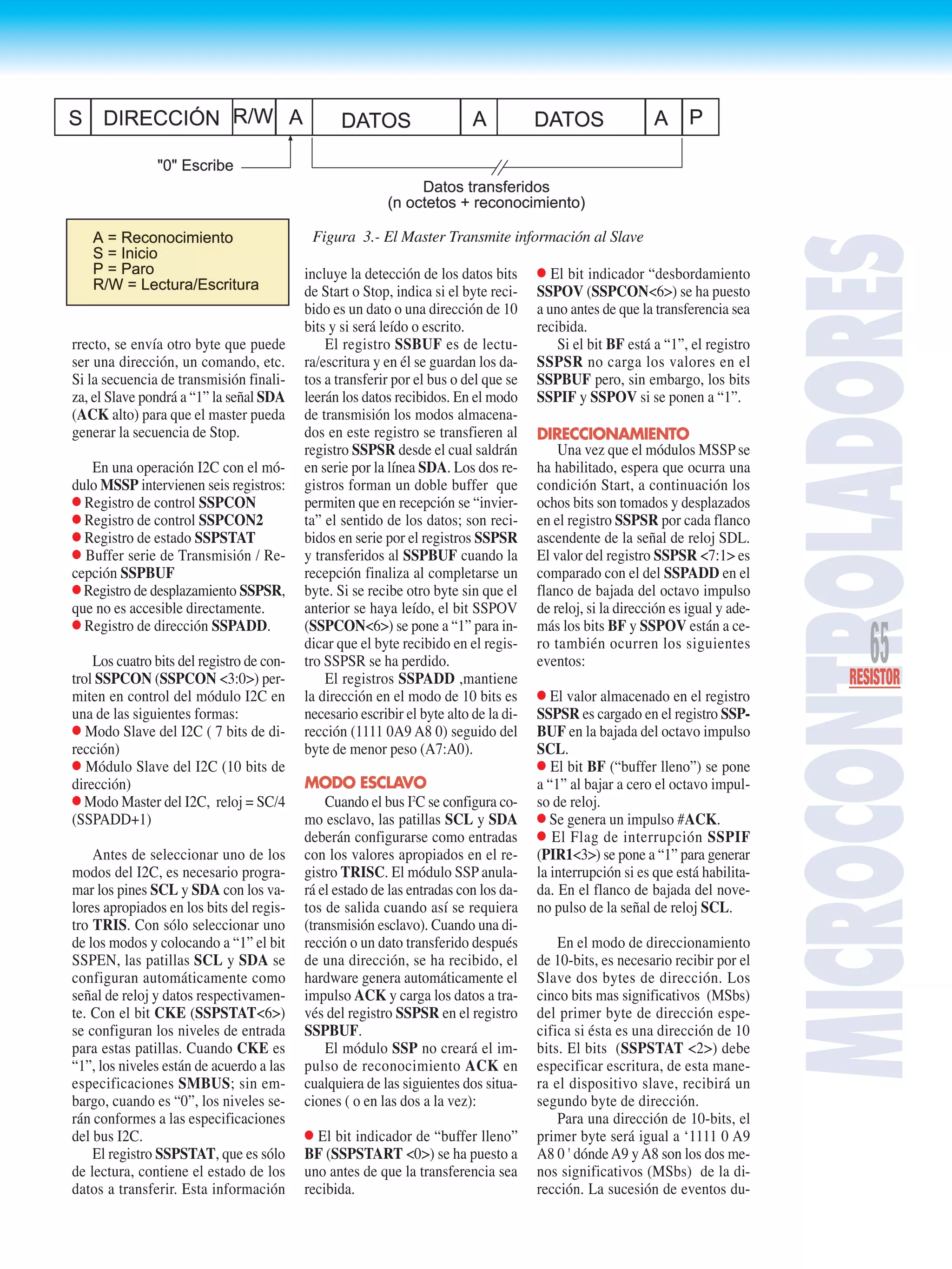

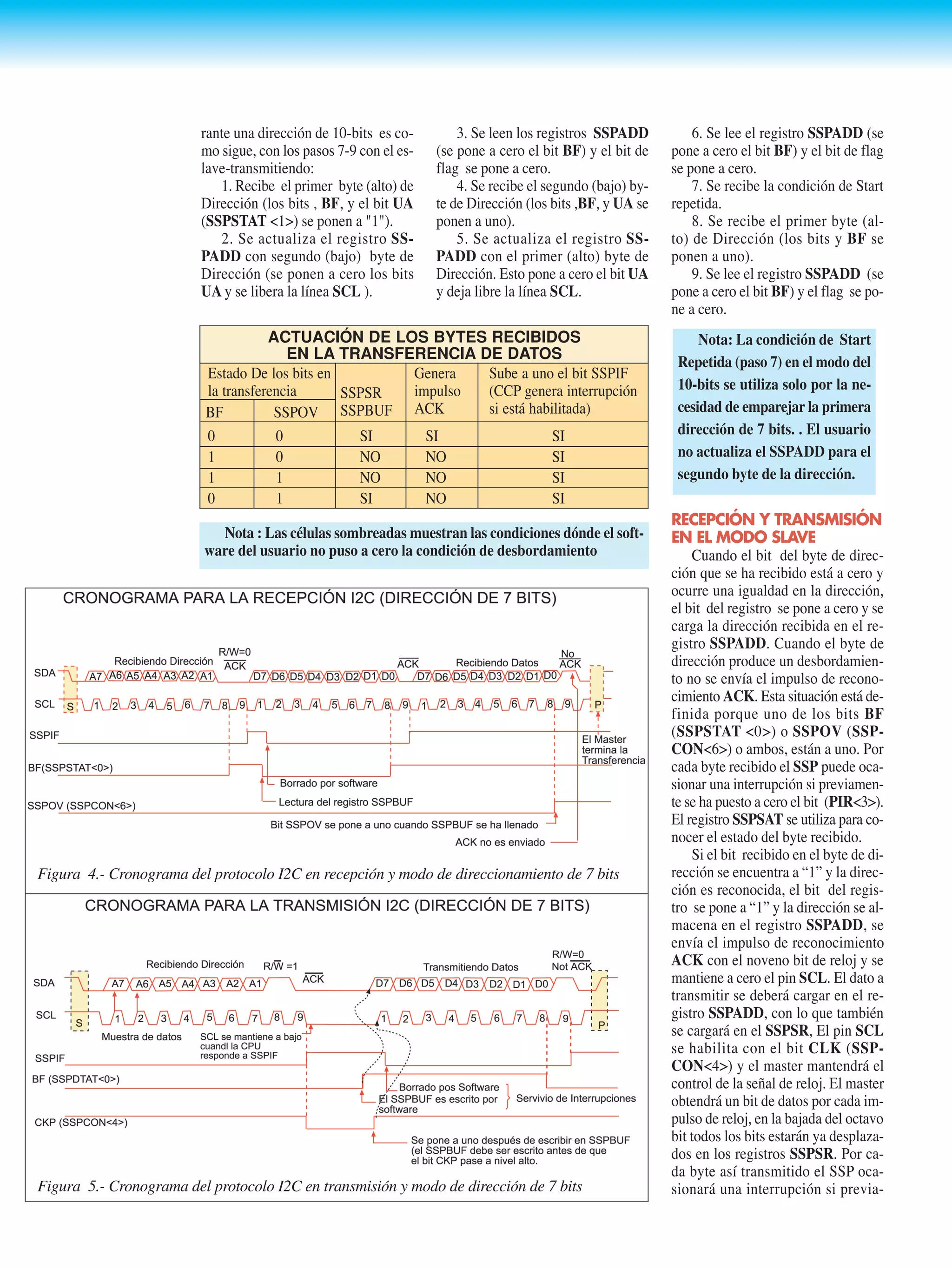

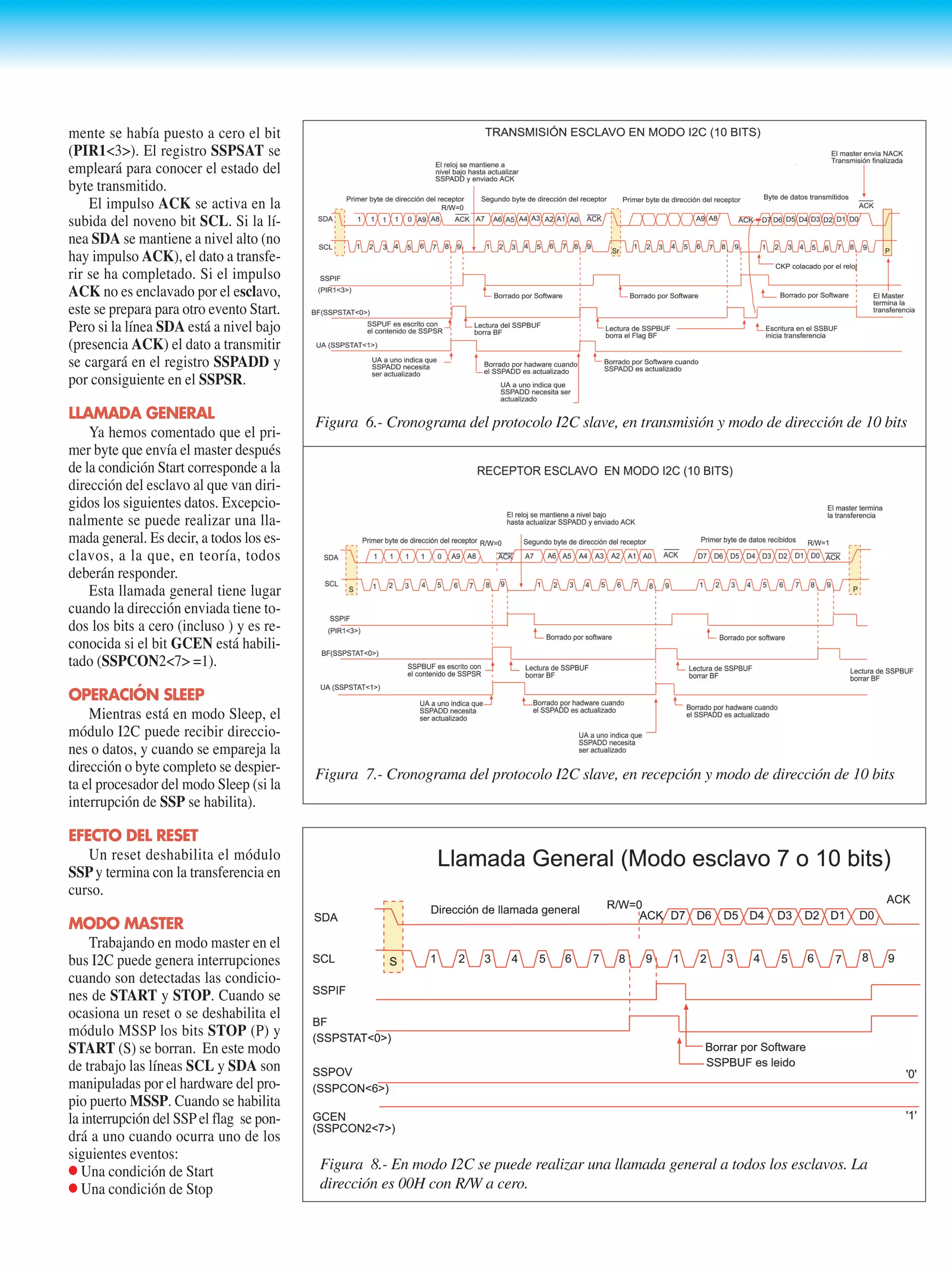

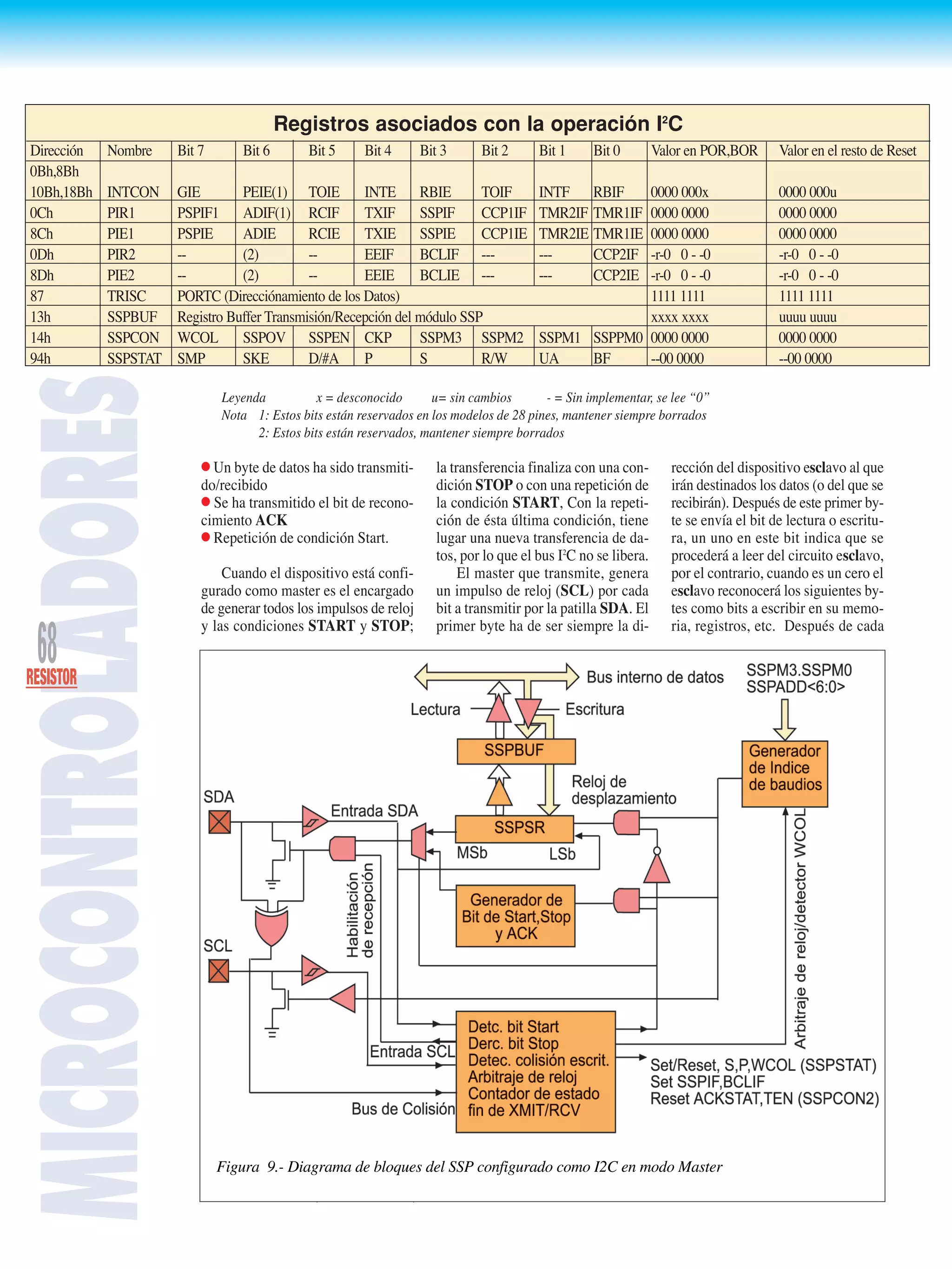

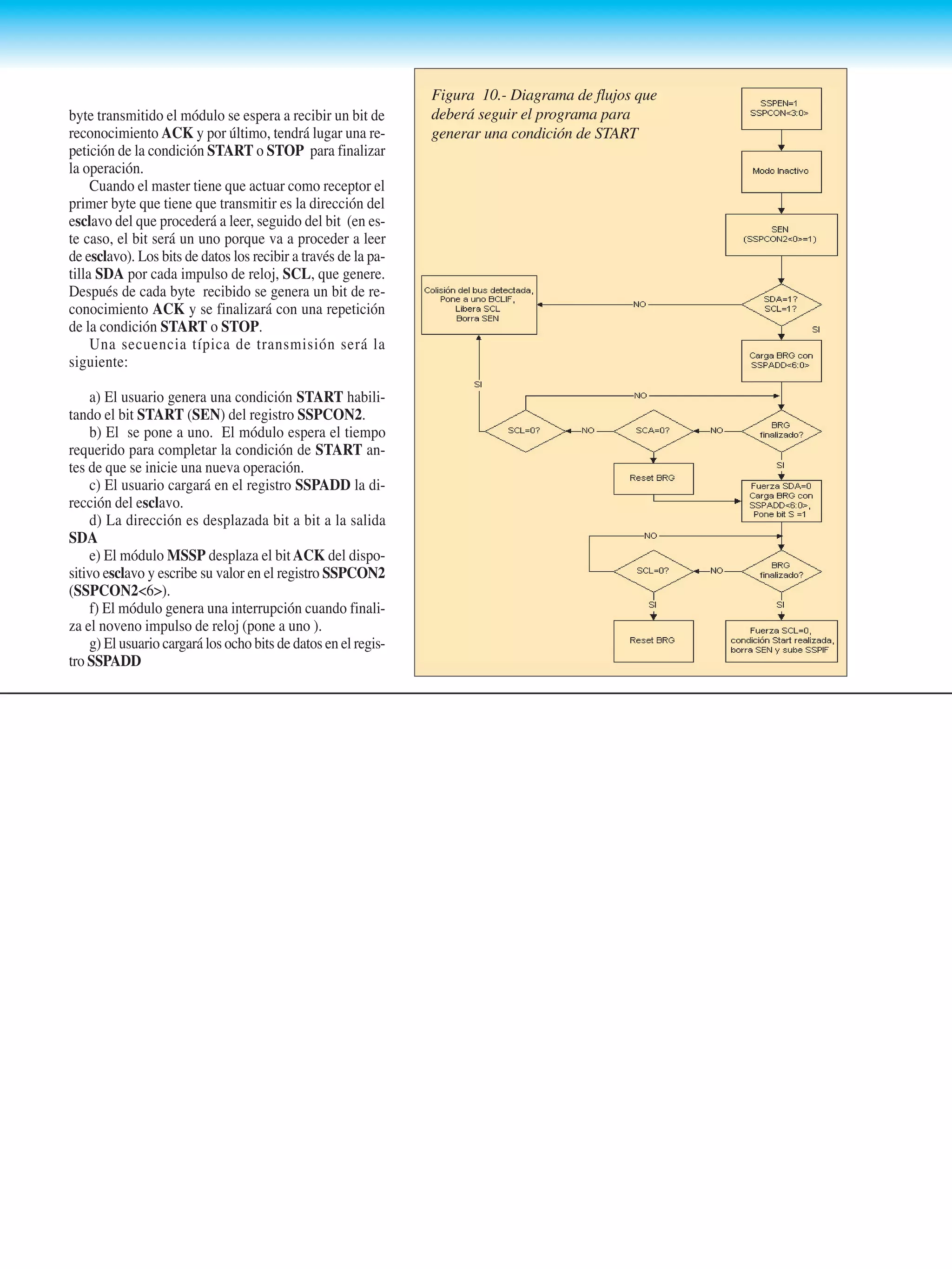

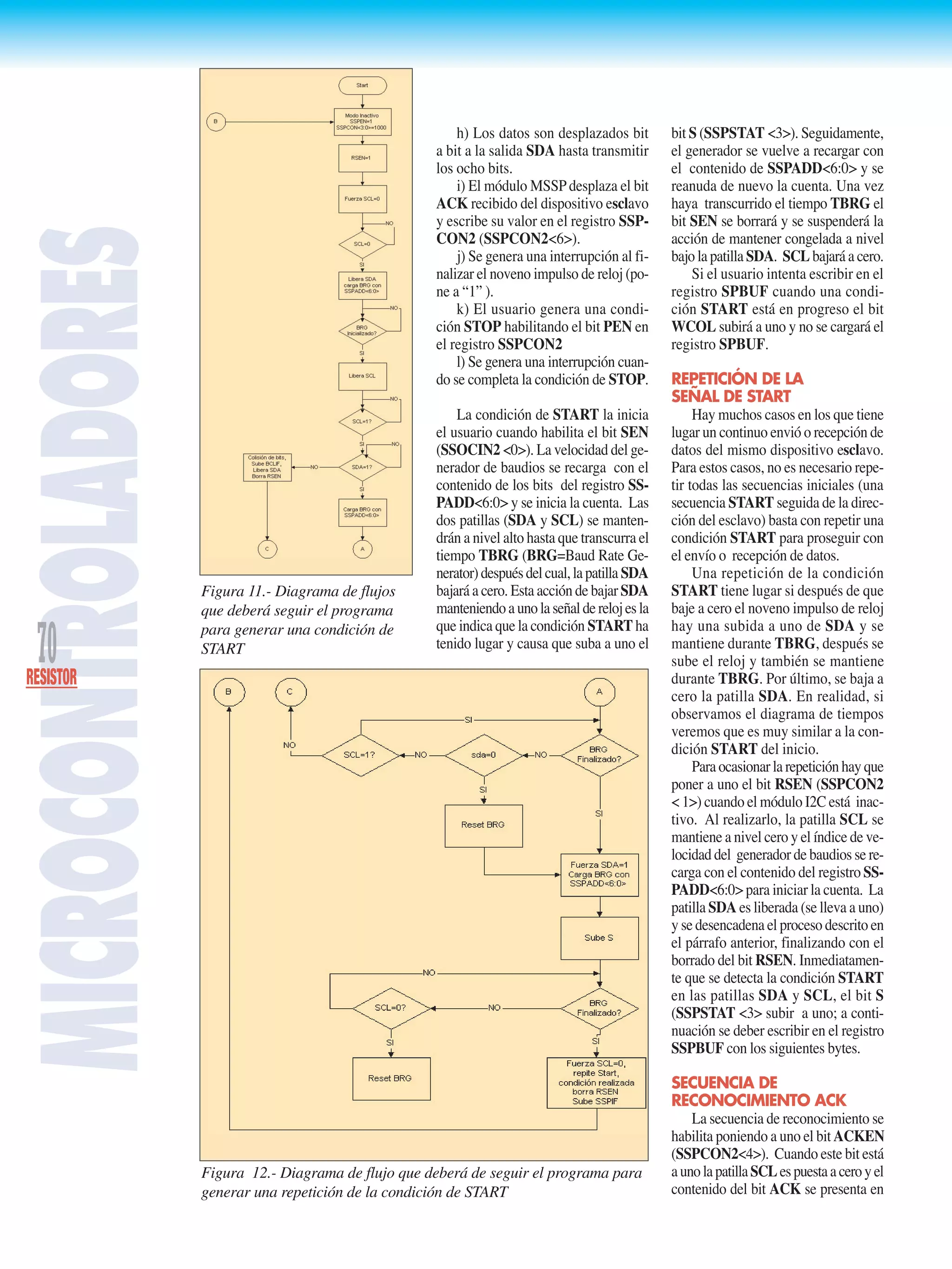

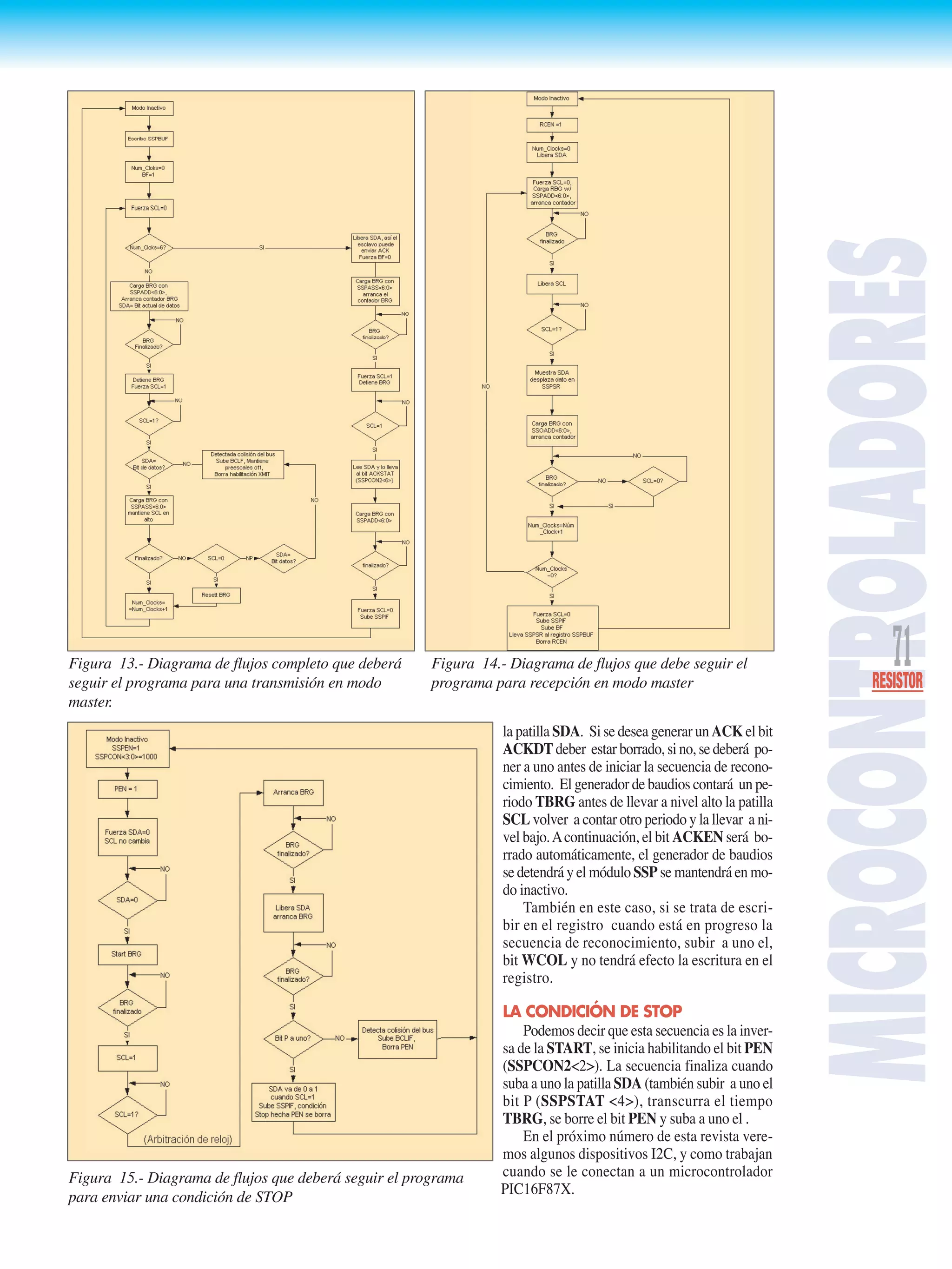

El documento describe el funcionamiento del puerto MSSP en modo I2C. El puerto MSSP puede funcionar como maestro o esclavo en el bus I2C, utilizando direcciones de 7 u 10 bits. En modo esclavo, recibe datos y direcciones del maestro y genera señales de acknowledgment, mientras que en modo maestro controla las líneas de datos y clock para comunicarse con los esclavos. El puerto utiliza varios registros para controlar la comunicación y almacenar datos de entrada y salida.