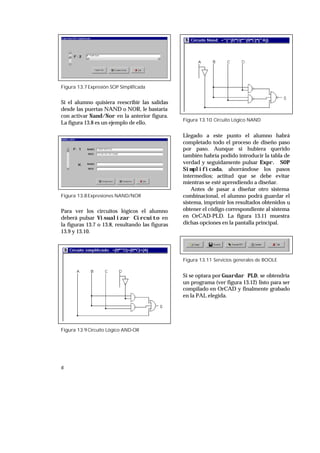

Este documento presenta el entorno BOOLE-DEUSTO para el análisis y diseño de sistemas digitales combinacionales y secuenciales a nivel de bit. Explica que BOOLE está orientado a las necesidades de estudiantes y profesores, especialmente para aprender los fundamentos. Luego compara BOOLE con entornos profesionales, señalando que BOOLE es más didáctico, fácil de usar y gratuito, mientras que los entornos profesionales son más complejos y costosos. Finalmente, presenta algunas característic