Este documento introduce los conceptos básicos de los microcontroladores. Explica que un microcontrolador es un sistema computacional integrado en un solo chip que contiene un procesador, memoria y periféricos. Describe las características típicas de un microcontrolador como la CPU, memoria, reloj, puertos E/S, perro guardián y otros módulos. Además, señala que los microcontroladores se utilizan en una amplia variedad de aplicaciones como electrodomésticos, automóviles y control industrial.

![Microcontroladores PIC de la Gama Media. 3. Juego de instrucciones de los PIC de la Gama Media.

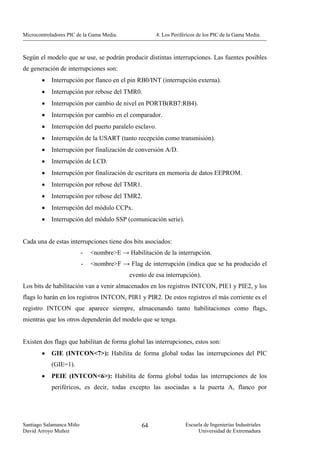

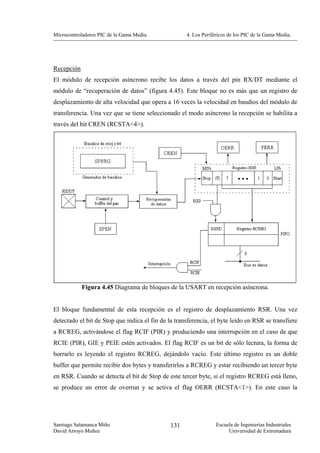

3.4 Juego de instrucciones.

Primero hay que hacer algunas consideraciones:

• Se puede usar cualquier registro especial como fuente o destino en una instrucción.

• Si usamos el registro de Estado como registro destino, los bits C, Z y DC

obtendrán los valores propios del resultado de la operación. Por ejemplo:

clrf STATUS ; después de su ejecución STATUS = 00001000

; correspondiendo ese 1 con el bit Z.

• Todas las instrucciones que manipulan bit son instrucciones de tipo lectura-

modificación-escritura, es decir, primero se lee el registro, luego se opera y por

último se escribe el resultado. Esto hay que tenerlo en cuenta fundamentalmente

cuando se trabaja sobre las puertas y en éstas se cambian los bits del TRIS

asociadas a ellas.

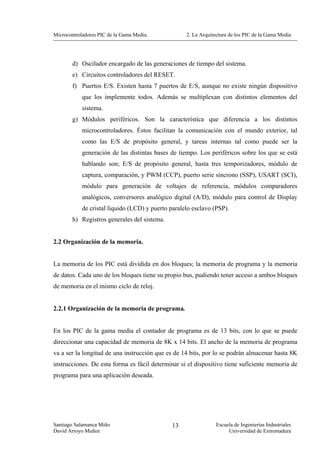

En la tabla 3.1 se especifica el significado de las distintas abreviaturas que van a ser utilizadas

posteriormente para la descripción detallada de cada una de las instrucciones de los PIC.

TABLA 3.1 Descripción de las abreviaturas utilizadas.

Campo Descripción

f Dirección del registro (0x00 a 0x7F)

w Registro de trabaja (acumulador)

b Posición de un bit de un registro (0 a 7)

k Literal, dato inmediato o dirección de una etiqueta.

x Valor indeterminado (0 ó 1)

Selección el destino;

d d = 0; el resultado se almacena en W.

d = 1; el resultado se almacena en el registro f.

dest Destino (registro W ó f)

TOS Nivel superior de la Pila.

PC Contador de Programa.

PCLATCH Parte alta del Contador de Programa

GIE Bit de activación global de interrupciones.

WDT Perro guardián (Watchdog).

TO Bit “Time Out” del Registro de Estado.

PD Bit “Power Down” del Registro de Estado

[ ] Opciones

( ) Contenido

→ Se asigna a

<> Campo de bits de un registro.

Santiago Salamanca Miño 43 Escuela de Ingenierías Industriales

David Arroyo Muñoz Universidad de Extremadura](https://image.slidesharecdn.com/pic-gama-media-120720161646-phpapp01/85/Pic-problemas-resueltos-49-320.jpg)

![Microcontroladores PIC de la Gama Media. 3. Juego de instrucciones de los PIC de la Gama Media.

3.4.1 Descripción detallada de las instrucciones por orden alfabético.

ADDLW Suma Literal con el W

Sintaxis: [etiqueta] ADDLW k

Operandos: 0 ≤ k ≤ 255

Operación: (W) + k → W

Flags afectados: C, DC, Z

Código OP: 11 111x kkkk kkkk

Descripción: El contenido del registro W se suma con los ocho bits del literal

“k”, almacenando el resultado en W.

Ejemplo ADDLW 0X15

Antes de la instrucción W = 0x10

Después de la instrucción W= 0x25

ADDWF Suma W y el registro f

Sintaxis: [etiqueta] ADDWF f, d

Operandos: 0 ≤ f ≤ 127

d є [0, 1]

Operación: (W) + (f) → dest

Flags afectados: C, DC, Z

Código OP: 00 0111 dfff ffff

Descripción: Suma el contenido del registro W y el registro “f”. Si “d” es 0,

el resultado se almacena en el registro W, mientras que si es 1

se almacena en el registro “f”.

Ejemplo: ADDWF FSR, 0

Antes de la instrucción W = 0x17

FSR = 0xC2

Después de la instrucción W = 0xD9

FSR = 0xC2

Santiago Salamanca Miño 45 Escuela de Ingenierías Industriales

David Arroyo Muñoz Universidad de Extremadura](https://image.slidesharecdn.com/pic-gama-media-120720161646-phpapp01/85/Pic-problemas-resueltos-51-320.jpg)

![Microcontroladores PIC de la Gama Media. 3. Juego de instrucciones de los PIC de la Gama Media.

ANDLW Y lógica entre Literal y W

Sintaxis: [etiqueta] ANDLW k

Operandos: 0 ≤ k ≤ 255

Operación: (W) AND (k) → W

Flags afectados: Z

Código OP: 11 1001 kkkk kkkk

Descripción: Realiza la operación lógica AND entre el registro W y los ocho

bits del literal “k”. El resultado se almacena en el registro W.

Ejemplo: ANDLW 0x5F

Antes de la instrucción W = 0xA3 ;0101 1111 (0x5F)

Después de la instrucción W = 0x03 ;1010 0011 (0xA3)

;0000 0011 (0x03)

ANDWF Y lógica entre W y f

Sintaxis: [etiqueta] ANDWF f, d

Operandos: 0 ≤ f ≤ 127

d є [0, 1]

Operación: (W) AND (f) → dest

Flags afectados: Z

Código OP: 00 0101 dfff ffff

Descripción: Realiza la operación lógica AND entre W y el registro “f”. Si

“d” es 0, el resultado se almacena en el registro W, mientras

que si es 1 se almacena en el registro “f”.

Ejemplo: ANDWF FSR, 1

Antes de la instrucción W = 0x17 ;0001 0111 (0x17)

FSR = 0xC2 ;1100 0010 (0xC2)

Después de la instrucción W = 0x17 ;0000 0010 (0x02)

FSR = 0x02

Santiago Salamanca Miño 46 Escuela de Ingenierías Industriales

David Arroyo Muñoz Universidad de Extremadura](https://image.slidesharecdn.com/pic-gama-media-120720161646-phpapp01/85/Pic-problemas-resueltos-52-320.jpg)

![Microcontroladores PIC de la Gama Media. 3. Juego de instrucciones de los PIC de la Gama Media.

BCF Borra un bit

Sintaxis: [etiqueta] BCF f, b

Operandos: 0 ≤ f ≤ 127

0≤b≤7

Operación: 0 → f<b>

Flags afectados: Ninguno

Código OP: 01 00bb bfff ffff

Descripción: Borra el bit “b” del registro “f”.

Ejemplo: BCF FLAG_REG, 7

Antes de la instrucción FLAG_REG = 0xC7 ;1100 0111

Después de la instrucción FLAG_REG = 0x47 ;0100 0111

BSF Pone a 1 un bit

Sintaxis: [etiqueta] BSF f, b

Operandos: 0 ≤ f ≤ 127

0≤b≤7

Operación: 1 → f<b>

Flags afectados: Ninguno

Código OP: 01 01bb bfff ffff

Descripción: Pone a 1 el bit “b” del registro “f”.

Ejemplo: BSF FLAG_REG, 7

Antes de la instrucción FLAG_REG = 0x0A ;0000 1010

Después de la instrucción FLAG_REG = 0x8A ;1000 1010

Santiago Salamanca Miño 47 Escuela de Ingenierías Industriales

David Arroyo Muñoz Universidad de Extremadura](https://image.slidesharecdn.com/pic-gama-media-120720161646-phpapp01/85/Pic-problemas-resueltos-53-320.jpg)

![Microcontroladores PIC de la Gama Media. 3. Juego de instrucciones de los PIC de la Gama Media.

BTFSC Testeo de bit y salto si es 0

Sintaxis: [etiqueta] BTFSC f, b

Operandos: 0 ≤ f ≤ 127

0≤b≤7

Operación: Salta si (f<b>) = 0

Flags afectados: Ninguno

Código OP: 01 10bb bfff ffff

Descripción: Si el bit “b” del registro “f” es 0, se salta una instrucción y se

continua con la ejecución.

Ejemplo: AQUÍ BTFSC FLAG, 4

FALSO GOTO REPETIR

VERDAD ..........

..................................

Antes de la instrucción PC = dirección de AQUÍ

Después de la instrucción Si FLAG, 4 =0

PC = dirección de VERDAD

Si FLAG, 4 = 1

PC = dirección de FALSO

BTFSS Testeo de bit y salto si es 1

Sintaxis: [etiqueta] BTFSS f, b

Operandos: 0 ≤ f ≤ 127

0≤b≤7

Operación: Salta si (f<b>) = 1

Flags afectados: Ninguno

Código OP: 01 11bb bfff ffff

Descripción: Si el bit “b” del registro “f” es 1, se salta una instrucción y se

continua con la ejecución.

Ejemplo: AQUÍ BTFSS FLAG, 4

FALSO GOTO REPETIR

VERDAD ..........

..................................

Antes de la instrucción PC = dirección de AQUÍ

Después de la instrucción Si FLAG, 4 =1

PC = dirección de VERDAD

Si FLAG, 4 = 0

PC = dirección de FALSO

Santiago Salamanca Miño 48 Escuela de Ingenierías Industriales

David Arroyo Muñoz Universidad de Extremadura](https://image.slidesharecdn.com/pic-gama-media-120720161646-phpapp01/85/Pic-problemas-resueltos-54-320.jpg)

![Microcontroladores PIC de la Gama Media. 3. Juego de instrucciones de los PIC de la Gama Media.

CALL Salto a subrutina

Sintaxis: [etiqueta] CALL k

Operandos: 0 ≤ k ≤ 2047

Operación: (PC) + 1 → TOS,

k → PC<10:0>,

(PCLATCH<4:3>) → PC<12:11>

Flags afectados: Ninguno

Código OP: 10 0kkk kkkk kkkk

Descripción: Salto a subrutina. Primero se guardan en la pila los 13 bits de

la dirección de retorno (PC + 1). Después se carga en el PC los

11 bits del inmediato “k”, los dos bits más significativos los

proporciona el PCLATCH<4:3>. CALL tarda dos ciclos de

instrucción en ejecutarse.

Ejemplo: PROGRAMA CALL SUBRUTINA

Antes de la instrucción PC =dirección de PROGRAMA

Después de la instrucción TOS = dirección de PROGRAMA + 1

PC = dirección de SUBRUTINA

CLRF Borra un registro f

Sintaxis: [etiqueta] CLRF f

Operandos: 0 ≤ f ≤ 127

Operación: 00h → f

1→Z

Flags afectados: Z

Código OP: 00 0001 1fff ffff

Descripción: Se borra el contenido del registro “f” y el flag Z de estado se

activa.

Ejemplo: CLRF FLAG_REG

Antes de la instrucción FLAG_REG = 0x5A

Después de la instrucción FLAG_REG = 0x00

Z=1

Santiago Salamanca Miño 49 Escuela de Ingenierías Industriales

David Arroyo Muñoz Universidad de Extremadura](https://image.slidesharecdn.com/pic-gama-media-120720161646-phpapp01/85/Pic-problemas-resueltos-55-320.jpg)

![Microcontroladores PIC de la Gama Media. 3. Juego de instrucciones de los PIC de la Gama Media.

CLRW Borra el registro W

Sintaxis: [etiqueta] CLRW

Operandos: Ninguno

Operación: 00h → W

1→Z

Flags afectados: Z

Código OP: 00 0001 1xxx xxxx

Descripción: Se borra el contenido del registro W y el flag Z de estado se

activa.

Ejemplo: CLRW

Antes de la instrucción W = 0x5A

Después de la instrucción W = 0x00

Z=1

CLRWDT Borra el “Watchdog”

Sintaxis: [etiqueta] CLRWDT

Operandos: Ninguno

Operación: 00h → WDT

0 → predivisor del WDT

1 → TO

1 → PD

Flags afectados: TO , PD

Código OP: 00 0000 0110 01000

Descripción: Se borra el contenido tanto del “Watchdog” como de su

predivisor. Los bits TO y PD del Registro de Estado se ponen

a 1.

Ejemplo: CLRWDT

Antes de la instrucción Temporizador WDT =x

Predivisor WDT = 1:128

Después de la instrucción Temporizador WDT = 0x00

Registro predivisor WDT =0

TO =1

PD =1

Predivisor WDT = 1:128

Santiago Salamanca Miño 50 Escuela de Ingenierías Industriales

David Arroyo Muñoz Universidad de Extremadura](https://image.slidesharecdn.com/pic-gama-media-120720161646-phpapp01/85/Pic-problemas-resueltos-56-320.jpg)

![Microcontroladores PIC de la Gama Media. 3. Juego de instrucciones de los PIC de la Gama Media.

COMF Complementa el registro f

Sintaxis: [etiqueta] COMF f, d

Operandos: 0 ≤ f ≤ 127

d є [0, 1]

Operación: ( f ) → dest

Flags afectados: Z

Código OP: 00 1001 dfff ffff

Descripción: Complementa el contenido del registro “f”. Si “d” es 0, el

resultado se almacena en el registro W, mientras que si es 1 se

almacena en el registro “f”.

Ejemplo: COMF REG1, 0

Antes de la instrucción REG1 = 0x13

Después de la instrucción REG1 = 0x13

W = 0xEC

DECF Decrementa el registro f

Sintaxis: [etiqueta] DECF f, d

Operandos: 0 ≤ f ≤ 127

d є [0, 1]

Operación: (f) - 1 → dest

Flags afectados: Z

Código OP: 00 0011 dfff ffff

Descripción: Decrementa el contenido del registro “f”. Si “d” es 0, el

resultado se almacena en el registro W, mientras que si es 1 se

almacena en el registro “f”.

Ejemplo: DECF CONT, 1

Antes de la instrucción CONT = 0x01

Z =0

Después de la instrucción CONT = 0x00

Z =1

Santiago Salamanca Miño 51 Escuela de Ingenierías Industriales

David Arroyo Muñoz Universidad de Extremadura](https://image.slidesharecdn.com/pic-gama-media-120720161646-phpapp01/85/Pic-problemas-resueltos-57-320.jpg)

![Microcontroladores PIC de la Gama Media. 3. Juego de instrucciones de los PIC de la Gama Media.

DECFSZ Decrementa el registro f y salta si es 0

Sintaxis: [etiqueta] DECFSC f, d

Operandos: 0 ≤ f ≤ 127

d є [0, 1]

Operación: (f) – 1 → dest; salta si el resultado es 0

Flags afectados: Ninguno

Código OP: 00 1011 dfff ffff

Descripción: Decrementa el contenido del registro “f”. Si “d” es 0, el

resultado se almacena en el registro W, mientras que si es 1 se

almacena en el registro “f”. Si el resultado es 0, se salta la

siguiente instrucción y se continua con la ejecución.

Ejemplo: RESTA DECFSZ CONT, 1

GOTO LAZO

CONTINUAR ...........

..............................................

Antes de la instrucción PC = dirección de RESTA

CONT = 0x01

Después de la instrucción CONT = 0x00

PC = dirección de CONTINUAR

GOTO Salto Incondicional

Sintaxis: [etiqueta] GOTO k

Operandos: 0 ≤ k ≤ 2047

Operación: k → PC<10:0>

PCLATCH<4:3> → PC<12:11>

Flags afectados: Ninguno

Código OP: 10 1kkk kkkk kkkk

Descripción: Salto incondicional. Se carga en el PC<10:0> los 11 bits del

inmediato “k”. Los dos bits restantes los proporciona el

PCLATCH<4:3>. GOTO tarda dos ciclos de instrucción en

ejecutarse.

Ejemplo: GOTO SALTO

Después de la instrucción PC = dirección SALTO

Santiago Salamanca Miño 52 Escuela de Ingenierías Industriales

David Arroyo Muñoz Universidad de Extremadura](https://image.slidesharecdn.com/pic-gama-media-120720161646-phpapp01/85/Pic-problemas-resueltos-58-320.jpg)

![Microcontroladores PIC de la Gama Media. 3. Juego de instrucciones de los PIC de la Gama Media.

INCF Incrementa el registro f

Sintaxis: [etiqueta] INCF f, d

Operandos: 0 ≤ f ≤ 127

d є [0, 1]

Operación: (f) + 1 → dest

Flags afectados: Z

Código OP: 00 1010 dfff ffff

Descripción: Incrementa el contenido del registro “f”. Si “d” es 0, el

resultado se almacena en el registro W, mientras que si es 1 se

almacena en el registro “f”.

Ejemplo: INCF CONT, 1

Antes de la instrucción CONT = 0xFF

Z =0

Después de la instrucción CONT = 0x00

Z =1

INCFSZ Incrementa el registro f y salta si es 0

Sintaxis: [etiqueta] INCFSC f, d

Operandos: 0 ≤ f ≤ 127

d є [0, 1]

Operación: (f) + 1 → dest; salta si el resultado es 0

Flags afectados: Ninguno

Código OP: 00 1111 dfff ffff

Descripción: Incrementa el contenido del registro “f”. Si “d” es 0, el

resultado se almacena en el registro W, mientras que si es 1 se

almacena en el registro “f”. Si el resultado es 0, se salta la

siguiente instrucción y se continua con la ejecución.

Ejemplo: SUMA INCFSZ CONT, 1

GOTO LAZO

CONTINUAR ...........

..............................................

Antes de la instrucción PC = dirección de RESTA

CONT = 0xFF

Después de la instrucción CONT = 0x00

PC = dirección de CONTINUAR

Santiago Salamanca Miño 53 Escuela de Ingenierías Industriales

David Arroyo Muñoz Universidad de Extremadura](https://image.slidesharecdn.com/pic-gama-media-120720161646-phpapp01/85/Pic-problemas-resueltos-59-320.jpg)

![Microcontroladores PIC de la Gama Media. 3. Juego de instrucciones de los PIC de la Gama Media.

IORLW O lógica entre Literal y W

Sintaxis: [etiqueta] IORLW k

Operandos: 0 ≤ k ≤ 255

Operación: (W) OR (k) → W

Flags afectados: Z

Código OP: 11 1000 kkkk kkkk

Descripción: Realiza la operación lógica OR entre el registro W y los ocho

bits del literal “k”. El resultado se almacena en el registro W.

Ejemplo: ANDLW 0x35

Antes de la instrucción W = 0x9A

Después de la instrucción W = 0xBF

Z =0

IORWF O lógica entre W y f

Sintaxis: [etiqueta] IORWF f, d

Operandos: 0 ≤ f ≤ 127

d є [0, 1]

Operación: (W) OR (f) → dest

Flags afectados: Z

Código OP: 00 0100 dfff ffff

Descripción: Realiza la operación lógica OR entre W y el registro “f”. Si

“d” es 0, el resultado se almacena en el registro W, mientras

que si es 1 se almacena en el registro “f”.

Ejemplo: IORWF REG, 0

Antes de la instrucción REG = 0x13

W = 0x91

Después de la instrucción REG = 0x13

W = 0x93

Z =0

Santiago Salamanca Miño 54 Escuela de Ingenierías Industriales

David Arroyo Muñoz Universidad de Extremadura](https://image.slidesharecdn.com/pic-gama-media-120720161646-phpapp01/85/Pic-problemas-resueltos-60-320.jpg)

![Microcontroladores PIC de la Gama Media. 3. Juego de instrucciones de los PIC de la Gama Media.

MOVLW Mueve un Literal a W

Sintaxis: [etiqueta] MOVLW k

Operandos: 0 ≤ k ≤ 255

Operación: k→W

Flags afectados: Ninguno

Código OP: 11 00xx kkkk kkkk

Descripción: El registro W se carga con el valor de los ocho bits del literal

“k”.

Ejemplo: MOVLW 0x5A

Después de la instrucción W = 0x5A

MOVF Mover a f

Sintaxis: [etiqueta] MOVF f, d

Operandos: 0 ≤ f ≤ 127

d є [0, 1]

Operación: (f) → dest

Flags afectados: Z

Código OP: 00 1000 dfff ffff

Descripción: El contenido del registro “f” se mueve al destino. Si “d” es 0,

el resultado se almacena en el registro W, mientras que si es 1

se almacena en el registro “f”.

Ejemplo: MOVF FSR, 0

Antes de la instrucción W = 0x00

FSR = 0xC2

Después de la instrucción W = 0xC2

Z =0

Santiago Salamanca Miño 55 Escuela de Ingenierías Industriales

David Arroyo Muñoz Universidad de Extremadura](https://image.slidesharecdn.com/pic-gama-media-120720161646-phpapp01/85/Pic-problemas-resueltos-61-320.jpg)

![Microcontroladores PIC de la Gama Media. 3. Juego de instrucciones de los PIC de la Gama Media.

MOVWF Mueve W al registro f

Sintaxis: [etiqueta] MOVWF f

Operandos: 0 ≤ f ≤ 127

Operación: (W) → f

Flags afectados: Ninguno

Código OP: 00 0000 1fff ffff

Descripción: Mueve el contenido del registro W al registro “f”.

Ejemplo: MOVWF OPTION_REG

Antes de la instrucción OPTION_REG = 0xFF

W = 0x4F

Después de la instrucción OPTION_REG = 0x4F

W = 0x4F

NOP No operar

Sintaxis: [etiqueta] NOP

Operandos: Ninguno

Operación: No realiza ninguna operación

Flags afectados: Ninguno

Código OP: 00 000 0xx0 0000

Descripción: No realiza ninguna operación.

Ejemplo: ETIQUETA NOP

Antes de la instrucción PC = dirección de ETIQUETA

Después de la instrucción PC = dirección de ETIQUETA + 1

Santiago Salamanca Miño 56 Escuela de Ingenierías Industriales

David Arroyo Muñoz Universidad de Extremadura](https://image.slidesharecdn.com/pic-gama-media-120720161646-phpapp01/85/Pic-problemas-resueltos-62-320.jpg)

![Microcontroladores PIC de la Gama Media. 3. Juego de instrucciones de los PIC de la Gama Media.

RETFIE Retorno de rutina de interrupción

Sintaxis: [etiqueta] RETFIE

Operandos: Ninguno

Operación: TOS → PC

1 → GIE

Flags afectados: Ninguno

Código OP: 00 0000 0000 1001

Descripción: Retorno de una rutina de interrupción. Los 13 bits de la

dirección de retorno los carga en el PC desde la pila. El bit

GIE (INTCON<7>) se pone automáticamente a 1, habilitando

nuevas interrupciones. Requiere dos ciclos de instrucción para

su ejecución.

Ejemplo: RETFIE

Después de la instrucción PC = TOS

GIE = 1

RETLW Retorno de subrutina con Literal en el W

Sintaxis: [etiqueta] RETLW k

Operandos: 0 ≤ k ≤ 255

Operación: k→W

TOS → PC

Flags afectados: Ninguno

Código OP: 11 01xx kkkk kkkk

Descripción: El registro W se carga con los ocho bits del literal “k”. El PC

toma los 13 bits de la dirección de retorno del nivel superior de

la pila. Requiere dos ciclos de instrucción para su ejecución.

Ejemplo: PROGRAMA CALL TABLA

.................

.................

TABLA ADDWF PC

RETLW k0

RETLW k1

...........................

RETLW kn

Antes de la instrucción W = 0x07

Después de la instrucción W = valor de k7

PC= TOS = dirección de PROGRAMA +1

Santiago Salamanca Miño 57 Escuela de Ingenierías Industriales

David Arroyo Muñoz Universidad de Extremadura](https://image.slidesharecdn.com/pic-gama-media-120720161646-phpapp01/85/Pic-problemas-resueltos-63-320.jpg)

![Microcontroladores PIC de la Gama Media. 3. Juego de instrucciones de los PIC de la Gama Media.

RETURN Retorno de subrutina

Sintaxis: [etiqueta] RETURN

Operandos: Ninguno

Operación: TOS → PC

Flags afectados: Ninguno

Código OP: 00 0000 0000 1000

Descripción: Retorno de una subrutina de interrupción. Los 13 bits de la

dirección de retorno los carga en el PC desde la pila. Requiere

dos ciclos de instrucción para su ejecución.

Ejemplo: FIN RETURN

Después de la instrucción PC = TOS

RLF Rota f a la izquierda a través del Carry

Sintaxis: [etiqueta] RLF f, d

Operandos: 0 ≤ f ≤ 127

d є [0, 1]

Operación: Rotación a la izquierda de f.

Flags afectados: C

Código OP: 00 1101 dfff ffff

Descripción: El contenido del registro “f” se rota una posición a la izquierda

a través del flag de carry. Si “d” es 0, el resultado se almacena

en el registro W, mientras que si es 1 se almacena en el

registro “f”.

C Registro f

Ejemplo: RLF REG1, 0

Antes de la instrucción REG1 = 1110 0110

C =0

Después de la instrucción REG1 = 1110 0110

W = 1100 1100

C =1

Santiago Salamanca Miño 58 Escuela de Ingenierías Industriales

David Arroyo Muñoz Universidad de Extremadura](https://image.slidesharecdn.com/pic-gama-media-120720161646-phpapp01/85/Pic-problemas-resueltos-64-320.jpg)

![Microcontroladores PIC de la Gama Media. 3. Juego de instrucciones de los PIC de la Gama Media.

RRF Rota f a la derecha a través del Carry

Sintaxis: [etiqueta] RRF f, d

Operandos: 0 ≤ f ≤ 127

d є [0, 1]

Operación: Rotación a la derecha de f.

Flags afectados: C

Código OP: 00 1100 dfff ffff

Descripción: El contenido del registro “f” se rota una posición a la derecha a

través del flag de carry. Si “d” es 0, el resultado se almacena

en el registro W, mientras que si es 1 se almacena en el

registro “f”.

C Registro f

Ejemplo: RLF REG1, 0

Antes de la instrucción REG1 = 1110 0110

C =0

Después de la instrucción REG1 = 1110 0110

W = 0111 0011

C =0

SLEEP Modo de reposo

Sintaxis: [etiqueta] SLEEP

Operandos: Ninguno

Operación: 00h → WDT

0 → predivisor del WDT

1 → TO

0 → PD

Flags afectados: TO , PD

Código OP: 00 0000 0110 0011

Descripción: El bit TO se pone a 1, y el bit PD del registro de Estado se

pone a 0. Además también se pone a cero el predivisor del

predivisor del WDT. El procesador entra en el modo SLEEP o

de reposo, dejando el oscilador principal de funcionar.

Ejemplo: SLEEP

Santiago Salamanca Miño 59 Escuela de Ingenierías Industriales

David Arroyo Muñoz Universidad de Extremadura](https://image.slidesharecdn.com/pic-gama-media-120720161646-phpapp01/85/Pic-problemas-resueltos-65-320.jpg)

![Microcontroladores PIC de la Gama Media. 3. Juego de instrucciones de los PIC de la Gama Media.

SUBLW Resta W de un Literal

Sintaxis: [etiqueta] SUBLW k

Operandos: 0 ≤ k ≤ 255

Operación: k – (W) → W

Flags afectados: C, DC, Z

Código OP: 11 110x kkkk kkkk

Descripción: El registro W se resta (mediante complemento a 2) de los ocho

bits del literal “k”. El resultado es almacenado en el registro

W.

Ejemplo: SUBLW 0x02

Antes de la instrucción W = 0x01

C =x

Z=x

Después de la instrucción W = 0x01

C=1 ;el resultado es positivo

Z=0

SUBWF Resta W del registro f

Sintaxis: [etiqueta] SUBWF f, d

Operandos: 0 ≤ f ≤ 127

d є [0, 1]

Operación: (f) - (W) → dest

Flags afectados: C, DC, Z

Código OP: 00 0010 dfff ffff

Descripción: El registro W se resta (mediante complemento a 2) del registro

“f”. Si “d” es 0, el resultado se almacena en el registro W,

mientras que si es 1 se almacena en el registro “f”.

Ejemplo: SUBWF REG1, 1

Antes de la instrucción REG1 =3

W =2

C =x

Z =x

Después de la instrucción REG1 =1

W =2

C =1 ;el resultado es positivo

Z =0

Santiago Salamanca Miño 60 Escuela de Ingenierías Industriales

David Arroyo Muñoz Universidad de Extremadura](https://image.slidesharecdn.com/pic-gama-media-120720161646-phpapp01/85/Pic-problemas-resueltos-66-320.jpg)

![Microcontroladores PIC de la Gama Media. 3. Juego de instrucciones de los PIC de la Gama Media.

SWAPF Intercambio de los Nibbles del registro f

Sintaxis: [etiqueta] SWAPF f, d

Operandos: 0 ≤ f ≤ 127

d є [0, 1]

Operación: (f<3:0>) → dest<7:4>

(f<7:4>) → dest<3:0>

Flags afectados: Ninguno

Código OP: 00 1110 dfff ffff

Descripción: Los cuatro bits más significativos y menos significativos del

registro “f”, son intercambiados entre si. Si “d” es 0, el

resultado se almacena en el registro W, mientras que si es 1 se

almacena en el registro “f”.

Ejemplo: SWAPF REG1, 0

Antes de la instrucción REG1 = 0xA5

Después de la instrucción REG1 = 0xA5

W = 0x5A

XORLW O exclusiva entre un Literal y W

Sintaxis: [etiqueta] XORLW k

Operandos: 0 ≤ k ≤ 255

Operación: (W) XOR (k) → W

Flags afectados: Z

Código OP: 11 1010 kkkk kkkk

Descripción: Realiza la operación lógica O exclusiva entre el registro W y

los ocho bits del literal “k”. El resultado es almacenado en el

registro W.

Ejemplo: XORLW 0xAF ;1010 1111 (0xAF)

Antes de la instrucción W = 0xB5 ;1011 1010 (0xB5)

Después de la instrucción W = 0x1A ;--------------- ---------

Z=0 ;0001 1010 (0x1A)

Santiago Salamanca Miño 61 Escuela de Ingenierías Industriales

David Arroyo Muñoz Universidad de Extremadura](https://image.slidesharecdn.com/pic-gama-media-120720161646-phpapp01/85/Pic-problemas-resueltos-67-320.jpg)

![Microcontroladores PIC de la Gama Media. 3. Juego de instrucciones de los PIC de la Gama Media.

XORWF O exclusiva entre W y el registro f

Sintaxis: [etiqueta] XORWF f, d

Operandos: 0 ≤ f ≤ 127

d є [0, 1]

Operación: (W) XOR (f) → dest

Flags afectados: Z

Código OP: 00 0110 dfff ffff

Descripción: Realiza la operación lógica O exclusiva entre el registro W y el

registro “f”. Si “d” es 0, el resultado se almacena en el registro

W, mientras que si es 1 se almacena en el registro “f”.

Ejemplo: XORWF REG, 1

Antes de la instrucción REG = 0xAF ;1010 1111 (0xAF)

W = 0xB5 ;1011 1010 (0xB5)

Después de la instrucción REG = 0x1A ;--------------- ---------

W = 0xB5 ;0001 1010 (0x1A)

Santiago Salamanca Miño 62 Escuela de Ingenierías Industriales

David Arroyo Muñoz Universidad de Extremadura](https://image.slidesharecdn.com/pic-gama-media-120720161646-phpapp01/85/Pic-problemas-resueltos-68-320.jpg)

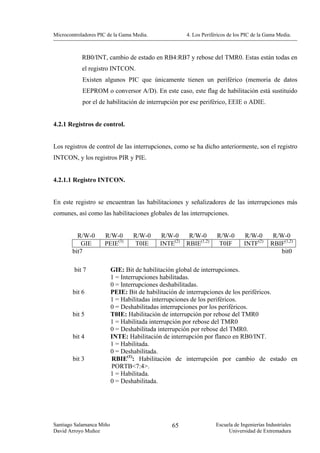

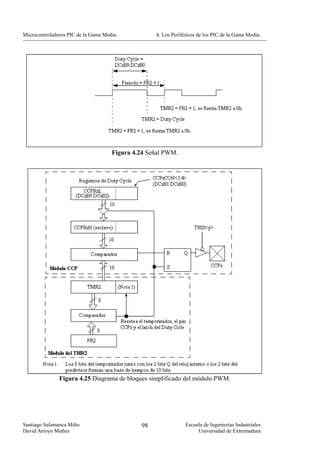

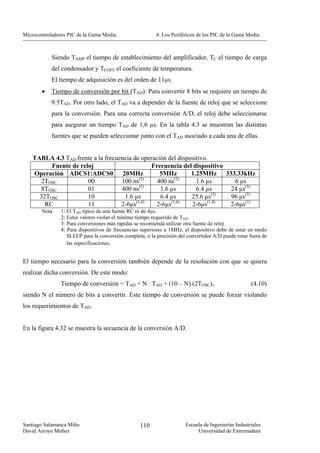

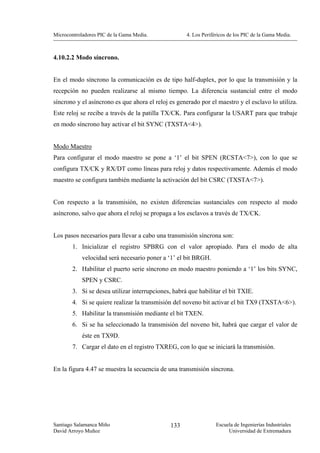

![Microcontroladores PIC de la Gama Media. 4. Los Periféricos de los PIC de la Gama Media.

Se desea un PWM con una frecuencia de 78.125 KHz, siendo FOSC= 20 MHz y el

predivisor del TMR2=1.

= [(PR 2) + 1]• 4 •

1 1

• •1 => PR2 = 63. (4.8)

78.125 KHz 20 • 10 6 s

(

log 20 • 10

6

)

78.125 • 10 3 = 8 bits

• Resolución Máxima = (4.9)

log(2 )

Para cualquier valor mayor de 255 se producirá un Duty Cycle del 100%.

Para terminar con este modo de operación se describen los pasos a seguir para configurar un

PWM.

Estos son:

1. Establecer el periodo PWM escribiendo el registro PR2.

2. Establecer el Duty Cycle escribiendo los bits DCxB9:DCxB0.

3. Configurar CCPx como salida.

4. Establecer el predivisor del TMR2 y habilitarlo escribiendo en T2CON.

5. Configurar el módulo CCP para la operación en modo PWM.

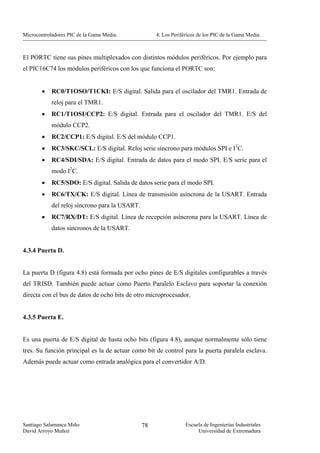

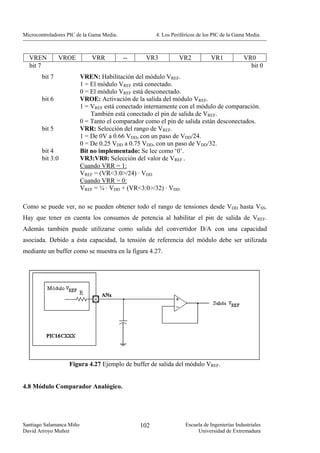

4.7 Módulo de Tensión de Referencia.

Este módulo proporciona una tensión seleccionable que se obtiene mediante el uso de 16

resistencias en serie. En la figura 4.26 se ve el hardware de este módulo.

Santiago Salamanca Miño 100 Escuela de Ingenierías Industriales

David Arroyo Muñoz Universidad de Extremadura](https://image.slidesharecdn.com/pic-gama-media-120720161646-phpapp01/85/Pic-problemas-resueltos-106-320.jpg)

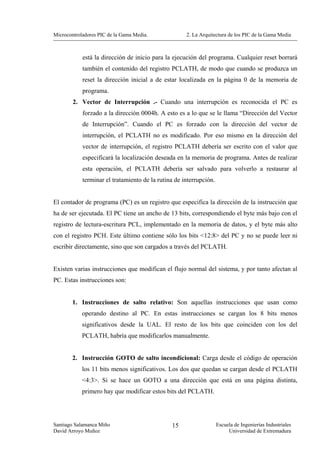

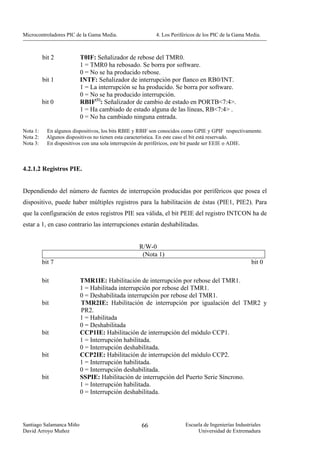

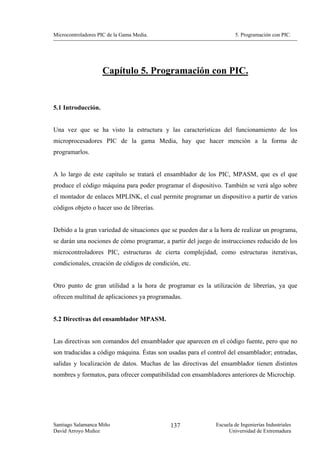

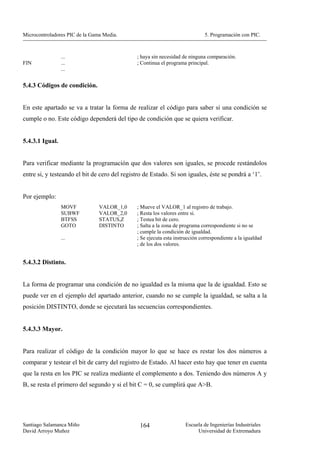

![Microcontroladores PIC de la Gama Media. 5. Programación con PIC.

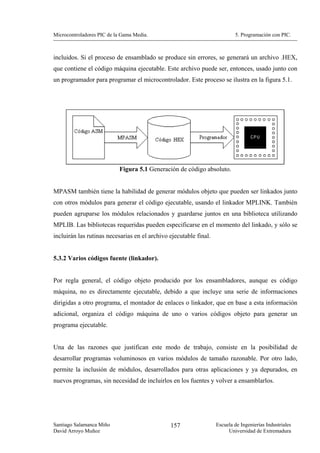

A continuación se muestra la tabla 5.1 con todas las directivas del ensamblador.

TABLA 5.1 Resumen de las directivas.

Directiva Descripción Sintaxis

Especifica las localizaciones inválidas de la

_ _BADRAM _ _badram <expr>

RAM.

Genera código para la selección del banco de

BANKISEL bankisel <etiqueta>

RAM para un direccionamiento indirecto.

BANKSEL Genera código para la selección de banco RAM. banksel <etiqueta>

CBLOCK Define un bloque de constantes. cblock [<expr>]

CODE Comienzo de sección de código ejecutable. [<etiqueta>] code [<dirección>]

_ _CONFIG Especifica los bits de configuración. _ _config <expr>

constant <etiqueta>[=<expr>,...

CONSTANT Declara símbolos constantes.

...,<etiqueta>[=<expr>]

[<etiqueta>]data<expr>[,<expr>,.., expr>]

DATA Crea datos numéricos y textos. [<etiqueta>]data“<cadena_de_texto>”

[,“<cadena_de_texto>”, ...]

[<etiqueta>] db<expr>[,<expr>,...,<expr>]

DB Declara datos de un byte.

[<etiqueta>] db“<texto>”[,“<texto>”,...]

[<etiqueta>] de<expr>[,<expr>,...,<expr>]

DE Define datos EEPROM.

[<etiqueta>] de“<texto>”[,“<texto>”,...]

define <nombre> [<valor>]

#DEFINE Define etiquetas.

define <nombre> [<arg>,...,<arg>]<valor>

[<etiqueta>] dt<expr>[,<expr>,...,<expr>]

DT Define una tabla.

[<etiqueta>] dt“<texto>”[,“<texto>”,...]

[<etiqueta>]dw<expr>[,<expr>,...,<expr>]

DW Declara datos de una palabra.

[<etiqueta>]dw“<texto>”[,“<texto>”,...]

ELSE Comienzo de bloque alternativo a IF. else

END Fin del bloque de programa. end

ENDC Fin de un bloque de definición de constantes. endc

ENDIF Fin de un bloque condicional. endif

ENDM Fin de la definición de una macro. endm

ENDW Fin de un lazo while endw

EQU Define y ensambla constantes. <etiqueta> equ <expr>

ERROR Emisión de un mensaje de error. error “<cadena_de_texto>”

ERRORLEVEL Fija niveles de error. errorlevel 0 | 1 | 2 <+ | -><nummsj>

EXITM Sale de una macro. exitm

EXPAND Expansión de macros. expand

EXTERN Declara una etiqueta externa. extern <etiqueta>[,<etiqueta>]

FILL Ocupa memoria. [<etiqueta>] fill <expr>, <cuenta>

GLOBAL Exporta una etiqueta definida. global <etiqueta> [, <etiqueta>]

IDATA Comienza una sección de datos inicializados. [<nombre>] idata [<dirección>]

_ _IDLOCS Especifica localizaciones ID. _ _idlocs <expr>

Comienza un bloque de ensamblado de código

IF if <expr>

condicional.

IFDEF Ejecuta si el símbolo ha sido definido. ifdef <etiqueta>

IFNDEF Ejecuta si el símbolo no ha sido definido. ifndef <etiqueta>

include <<archivo_include>> |

#INCLUDE Incluye archivos fuente adicionales.

“<archivo_include>”

LIST Listado de opciones. list [<opción_list>, ..., <opción_list>]

LOCAL Declara una variable local de una macro. local <etiqueta> [,<etiqueta>]

MACRO Define una macro. <etiqueta> macro [<arg>, ..., <arg>]

_ _MAXRAM Especifica la dirección máxima de RAM. _ _maxram <expr>

Santiago Salamanca Miño 138 Escuela de Ingenierías Industriales

David Arroyo Muñoz Universidad de Extremadura](https://image.slidesharecdn.com/pic-gama-media-120720161646-phpapp01/85/Pic-problemas-resueltos-144-320.jpg)

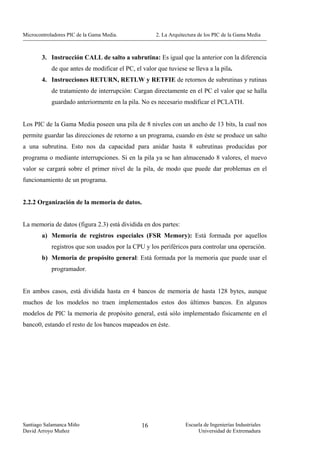

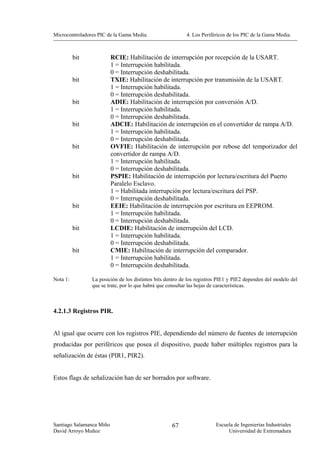

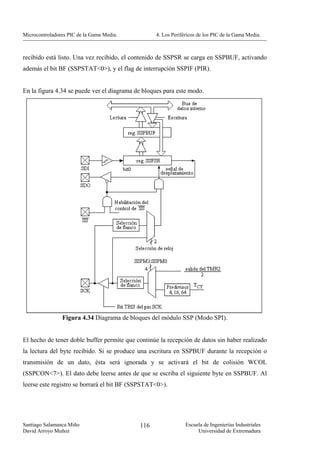

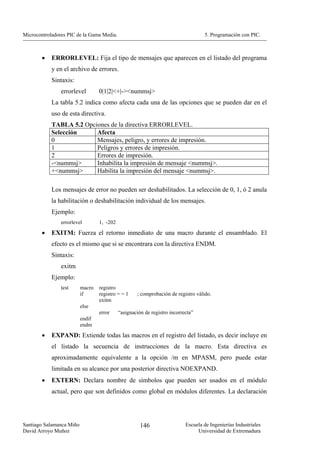

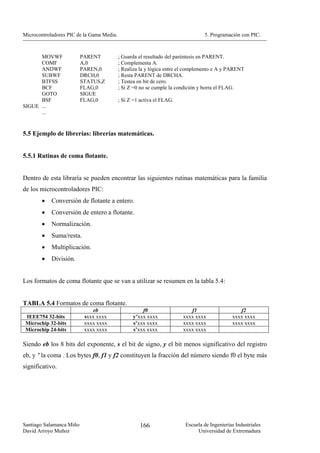

![Microcontroladores PIC de la Gama Media. 5. Programación con PIC.

Directiva Descripción Sintaxis

MESSG Crea mensaje definido por el usuario messg “<texto_del_mensaje>”

NOEXPAND Fin de la expansión de macros. noexpand

NOLIST Desactiva las opciones de salida. nolist

ORG Fija el origen del programa. <etiqueta> org <expr>

PAGE Inserta una salida de página. page

Genera el código para la selección de la página

PAGESEL pagesel <etiqueta>

de ROM.

PROCESSOR Indica tipo de procesador. processor <tipo_de_procesador>

RADIX Especifica la base de numeración por defecto. radix <radix_defecto>

RES Reserva memoria. [etiqueta>] res <unidades_de_memoria>

SET Define y ensambla variables. <etiqueta> set <expr>

SPACE Inserta líneas en blanco en el listado. space <expr>

SUBTITLE Especifica el subtítulo del programa. subtitle “<texto_de_subtítulo>”

TITLE Especifica el título del programa. title “<texto_de_título>”

UDATA Comienza una sección de datos no inicializados. [<nombre>] udata [<dirección>]

Comienza una sección de datos no inicializados

UDATA_OVR [<nombre>] udata_ovr [<dirección>]

reutilizables.

Comienza una sección de datos no inicializados

UDATA_SHR [<nombre>] udata_shr [<dirección>]

compartidos.

#UNDEFINE Borra una etiqueta de substitución. #undefine <etiqueta>

variable <etiqueta>[=<expr>, ...,

VARIABLE Declara un símbolo variable.

<etiqueta> [=<expr>]]

WHILE Ejecuta un lazo mientras la condición sea verdad while <expr>

A continuación se muestra una descripción detallada de cada una de ellas:

• _ _BADRAM y _ _MAXRAM1: Ambas directivas juntas marcan los registros que

no están implementados. _ _MAXRAM define la dirección máxima de RAM

válida, iniciando el mapa de RAM, validando todas las direcciones menores que

<expr>. El valor marcado por <expr> debe ser mayor o igual que la máxima

dirección de la página 0 de la memoria RAM y menor que 1000H. _ _BADRAM

define la localización de las direcciones de la RAM que no son válidas. Una

directiva _ _BADRAM debe estar precedida por una _ _MAXRAM. Cada <expr>

usada por _ _BADRAM debe ser menor o igual al valor especificado por la <expr>

de _ _MAXRAM.

_ _ MAXRAM puede ser usada más de una vez, redefiniendo la máxima dirección

válida de RAM y reseteando el mapa entero de RAM.

1

En las directivas que están precedidas por dos guiones bajos _ _, no hay ningún espacio entre ellos, pero en este

documento se incluyen, ya que si no, no se distinguen bien.

Santiago Salamanca Miño 139 Escuela de Ingenierías Industriales

David Arroyo Muñoz Universidad de Extremadura](https://image.slidesharecdn.com/pic-gama-media-120720161646-phpapp01/85/Pic-problemas-resueltos-145-320.jpg)

![Microcontroladores PIC de la Gama Media. 5. Programación con PIC.

• CBLOCK y ENDC: Sirve para definir una lista de constantes en la memoria de

datos.

La sintaxis es la siguiente:

cblock [<expr>]

<etiqueta>[:incremento][,<etiqueta>[:<incremento>]]

endc

[<expr>] indica la dirección inicial de la memoria de datos para la primera

etiqueta. En el caso de no ser especificada, se pueden dar dos situaciones:

a) Si anteriormente se ha utilizado esta misma directiva, entonces a la primera

etiqueta se le asigna la dirección inmediatamente superior a la de la última

etiqueta de la directiva CBLOK anterior.

b) En el caso de que sea la primera vez que se utilice, entonces se le asigna la

dirección 0x00.

Todas las etiquetas dentro de la definición de CBLOCK tendrán posiciones de

memoria consecutivas, a no ser que se haya definido [:<incremento>], en cuyo

caso se incrementará la dirección con el valor indicado.

La definición de etiquetas termina cuando el ensamblador se encuentre con la

directiva ENDC.

Ejemplo:

cblock 0x0C ; nombre_1 será

; asignada a la dirección 0x0C

nombre_1, nombre_2 ; nombre_2 a 0E, nombre_3 a 0F

nombre_3, nombre_4 ; y nombre_4 a 10.

endc

• CODE: Se utiliza en la generación de código objeto. Indica el principio de la

sección de un código de programa. Si no se especifica la <etiqueta>, la sección se

nombra como code. La dirección donde empieza la sección de programa es la

dirección especificada, siendo cero si no se indica.

La sintaxis es:

[<etiqueta>] code [<dirección de ROM>]

Ejemplo:

RESET code H’01FF’

goto INICIO

Santiago Salamanca Miño 141 Escuela de Ingenierías Industriales

David Arroyo Muñoz Universidad de Extremadura](https://image.slidesharecdn.com/pic-gama-media-120720161646-phpapp01/85/Pic-problemas-resueltos-147-320.jpg)

![Microcontroladores PIC de la Gama Media. 5. Programación con PIC.

• _ _CONFIG: Pone los bits de configuración del microprocesador al valor indicado

por <expr>. Hay que referirse a las hojas de características de los

microcontroladores PIC para la descripción de los bits de configuración de cada

procesador.

Antes del uso de esta directiva, el procesador debe de ser declarado a través de la

línea de comandos, con la directiva LIST o PROCESOR. Si estas directivas son

usadas con la familia PIC17CXX, el formato de salida del archivo hex debe estar

fijado a INHX32 mediante una directiva LIST.

La sintaxis de esta directiva es:

_ _config <expr>

Ejemplo:

list p=17c42, f=INHX32

_ _config H’FFFF’ ; Bits de configuración por defecto.

• CONSTANT y VARIABLE: Sirve para definir símbolos que pueden ser usados

en expresiones de MPASM. La diferencia entre usar una u otra, es que con

CONSTANT no se puede modificar su valor una vez asignado. Además al definir

variables no es necesario iniciarlas.

La sintaxis es la siguiente:

constant <etiqueta>=<expr>[,<etiqueta>=<expr>]

variable <etiqueta>[=<expr>][,<etiqueta>[=<expr>]]

Ejemplo:

variable RECLONG=64 ; Establece el valor por defecto de RECLONG.

constant BUFLONG=512 ; Inicializa BUFLONG.

constant MAXMEM=RECLONG+BUFLONG ; Calcula MAXMEM

• DATA: Inicializa con datos una o más palabras de la memoria de programa. Estos

datos pueden ser constantes, etiquetas o expresiones de alguna de las anteriores. El

dato puede consistir también en una cadena de caracteres en código ASCII,

<cadena_de_texto>, encerrado en comillas simples para un solo carácter o dobles

comillas para una cadena. Los elementos de un solo carácter se guardan en el byte

bajo de la palabra, mientras que las cadenas de caracteres son guardas de dos en

dos en cada palabra, con el primer carácter en el byte más significativo. Si el

Santiago Salamanca Miño 142 Escuela de Ingenierías Industriales

David Arroyo Muñoz Universidad de Extremadura](https://image.slidesharecdn.com/pic-gama-media-120720161646-phpapp01/85/Pic-problemas-resueltos-148-320.jpg)

![Microcontroladores PIC de la Gama Media. 5. Programación con PIC.

número de caracteres es impar, el último byte es cero. Cuando se genera el código

objeto, esta directiva también puede utilizarse para inicializar valores de datos.

La sintaxis de esta directiva es:

[<etiqueta>] data <expr>[,<expr>, ..., <expr>]

[<etiqueta>] data “<cadena_de_texto>”[, “<cadena_de_texto>”, ...]

Ejemplo:

data etiqueta_reubicablel+10 ; constantes

data 1,2,etiqueta_ext l ; constantes, externas

data “testeando 1,2,3” ; cadena de texto

data ‘N’ ; carácter simple

data inicio_de_programa ; etiqueta reubicable

• DB: Reserva palabras en la memoria de programa con valores de ocho bits. Para

expresiones múltiples se guardan en bytes consecutivos hasta el final de la

expresión. Si son un número impar de expresiones, el último byte será cero.

Cuando se genera el código objeto, esta directiva también se puede utilizar para

inicializar el valor de los datos.

Su sintaxis es:

[<etiqueta>] db <expr>[,<expr>, ..., <expr>]

Ejemplo:

db ‘t’, 0x0f, ‘e’, 0x0f, ‘s’, 0x0f, ‘t’, ‘n’

• DE: Reserva palabras en memoria con datos de ocho bits. Cada <expr> debe

evaluarse con un valor de ocho bits. Los bits altos de la palabra son ceros. Cada

carácter en una cadena de caracteres se guarda en una palabra distinta.

Aunque se diseñó originalmente para inicializar datos EEPROM en los PIC16C8X,

esta directiva puede utilizarse para cualquier localización y en cualquier

procesador.

Su sintaxis es:

[<etiqueta>] de <expr>[,<expr>, ..., <expr>]

Ejemplo:

org H’2100’ ; Inicializar datos EEPROM.

de “Mi Programa, v1.0”, 0

• #DEFINE: Esta directiva sustituye un nombre por un valor. Donde quiera que

aparezca <nombre> en el código ensamblador, será sustituido por <valor>.

Santiago Salamanca Miño 143 Escuela de Ingenierías Industriales

David Arroyo Muñoz Universidad de Extremadura](https://image.slidesharecdn.com/pic-gama-media-120720161646-phpapp01/85/Pic-problemas-resueltos-149-320.jpg)

![Microcontroladores PIC de la Gama Media. 5. Programación con PIC.

Si no se añade el valor al que sustituir simplemente se define un <nombre>,

pudiéndolo testear usando la directiva IFDEF.

Su sintaxis es:

#define <nombre> [<valor>]

Ejemplo:

#define longitud 20

#define control 0x19,7

#define posición (X,Y,Z) (Y-(2 * Z +X))

.

.

.

test dw posición (1, longitud, 512)

bsf control ; pone a ‘1’ el bit 7 en f19

• DT: Genera una serie de instrucciones RETLW, una por cada <expr>. Éstas deben

ser un valor de ocho bits. En una cadena de caracteres, cada uno se guarda en su

propia instrucción RETLW.

Su sintaxis es:

[<etiqueta>] dt <expr> [,<expr>, ..., <expr>]

Ejemplo:

dt “Mensaje”, 0

dt PrimerValor, SegundoValor, UltimoValor

• DW: Reserva palabras de la memoria de programa para datos, inicializando estos

espacios a valores específicos. Los datos son guardados en posiciones de memoria

consecutivas, incrementando el contador en uno. Las expresiones pueden ser

cadenas de literales y se guardan como se describe en la directiva DATA.

Sintaxis:

[<etiqueta>] dw <expr>[,<expr>, ..., <expr>]

Ejemplo:

dw 39, “diagnostico 39”, (d_list*2+d_offset)

dw diagbase-1

• ELSE: Se usa junto con la directiva IF para proporcionar un camino alternativo a

la ensamblación si se evalúa el IF como falso.

Sintaxis:

else

Santiago Salamanca Miño 144 Escuela de Ingenierías Industriales

David Arroyo Muñoz Universidad de Extremadura](https://image.slidesharecdn.com/pic-gama-media-120720161646-phpapp01/85/Pic-problemas-resueltos-150-320.jpg)

![Microcontroladores PIC de la Gama Media. 5. Programación con PIC.

EXTERN debe ser incluida antes de que la <etiqueta> sea usada. Al menos una

etiqueta debe ser especificada en la línea.

Sintaxis:

extern <etiqueta>[,<etiqueta>]

Ejemplo:

extern Funcion

...

call Funcion

• FILL: Genera <cuenta> ocurrencias de la palabra o byte de programa <expr>. Si

está limitada por paréntesis, <expr> puede ser una instrucción de ensamblador.

Sintaxis:

[<etiqueta>] fill <expr>, <cuenta>

Ejemplo:

fill 0x1009, 5 ; ocupa con una constante.

fill (GOTO VECTOR_RESET), SIGUIENTE_BLOQUE-$

• GLOBAL: Se usa en la generación de código objeto. Declara nombres de

símbolos que son definidos en el módulo actual, estando disponibles en otros

módulos. La declaración GLOBAL debe de ser después de que la <etiqueta> sea

definida. Al menos una etiqueta debe de ser especificada en la línea.

Sintaxis:

global <etiqueta> [, <etiqueta>]

Ejemplo:

udata

Var1 res 1

Var2 res 1

global Var1, Var2

code

SumaTres

global SumaTres

addlw 3

return

• IDATA: Se usa en la generación de código objeto. Declara el comienzo de una

sección de datos inicializados. Si no se especifica ninguna <etiqueta> la sección es

nombrada idata. La dirección de comienzo se inicializa con la dirección

especificada o cero si esta no se indica. En este segmento no puede generarse

ningún código.

Santiago Salamanca Miño 147 Escuela de Ingenierías Industriales

David Arroyo Muñoz Universidad de Extremadura](https://image.slidesharecdn.com/pic-gama-media-120720161646-phpapp01/85/Pic-problemas-resueltos-153-320.jpg)

![Microcontroladores PIC de la Gama Media. 5. Programación con PIC.

El linkador generará una tabla de consulta por cada byte especificado en la sección

idata. El usuario debe entonces linkar o incluir el apropiado código de

inicialización.

Sintaxis:

[<etiqueta>] idata [<dirección RAM>]

Ejemplo:

idata

LimiteV dw 0

LimiteH dw D’300’

Ganancia dw D’5’

Flags db 0

Cadena db ‘¡Hola allí!’

• _ _IDLOCS: Fija cuatro localizaciones ID a los valores de los dígitos en

hexadecimal de <expr>. Por ejemplo, si <expr> es 1AF, la primera localización ID

(dirección más baja) es cero, la segunda uno, la tercera diez, y la cuarta quince.

Antes de usar esta directiva, el tipo de procesador debe ser indicado mediante la

directiva LIST o PROCESSOR. Esta directiva no es válida para la familia de los

PIC17CXX.

Sintaxis:

_ _idlocs <expr>

Ejemplo:

_ _idlocs H’1234’

• IF: Empieza la ejecución de un bloque de ensamblado condicional. Si la

evaluación de <expr> es verdadera, el código que sigue a la directiva IF será

ensamblado. Si no, este código será saltado hasta encontrar una directiva ELSE o

ENDIF.

Una expresión que se evalúa como cero es considerada falsa, siendo verdadera

para cualquier otro valor.

Sintaxis:

if <expr>

Santiago Salamanca Miño 148 Escuela de Ingenierías Industriales

David Arroyo Muñoz Universidad de Extremadura](https://image.slidesharecdn.com/pic-gama-media-120720161646-phpapp01/85/Pic-problemas-resueltos-154-320.jpg)

![Microcontroladores PIC de la Gama Media. 5. Programación con PIC.

Sintaxis:

list [<opción_list>, ..., <opción_list>]

Ejemplo:

list p =17c42, f =INHX32, r =DEC

• LOCAL: Declara que los elementos de los datos especificados serán considerados

en el contexto local de la macro. La <etiqueta> puede ser idéntica a otra etiqueta

declarada fuera de la macro, sin haber ningún conflicto entre las dos.

Si la macro es llamada reiteradamente, cada llamada tendrá su propia copia local.

Sintaxis:

local <etiqueta> [, <etiqueta>]

Ejemplo:

<segmento de código principal>

.

.

.

longitud equ 10 ; versión global

tamaño equ 20 ; notar que es una variable local

test macro tamaño

local longitud, etiqueta ; local longitud y etiqueta

longitud set tamaño ; modifica local longitud

etiqueta res longitud

longitud set longitud-20

endm ; fin de la macro

• MACRO: Una macro es una secuencia de instrucciones que puede ser insertada en

el código fuente del ensamblador usando una simple llamada a la macro. La macro

debe de ser definida previamente. Una macro puede a su vez llamar a otra, o a si

misma.

Sintaxis:

<etiqueta> macro [<arg>,..., <arg>]

Ejemplo:

Leer macro dispositivo, buffer, contador

movlw dispositivo

movwf ram_20

movlw buffer ; dirección de buffer.

movwf ram_21

movlw contador ; byte del contador.

call sis_21 ; leer fila call.

• MESSG: Provoca la impresión de un mensaje de información en el archivo del

listado. El texto del mensaje puede ser de hasta 80 caracteres.

Santiago Salamanca Miño 151 Escuela de Ingenierías Industriales

David Arroyo Muñoz Universidad de Extremadura](https://image.slidesharecdn.com/pic-gama-media-120720161646-phpapp01/85/Pic-problemas-resueltos-157-320.jpg)

![Microcontroladores PIC de la Gama Media. 5. Programación con PIC.

Sintaxis:

messg “<texto_de_mensaje>”

Ejemplo:

mssg_macro macro

messg “mssg_macro no tiene argumentos”

endm

• NOEXPAND: Final de la expansión de la macro en el archivo del listado.

• NOLIST: Desactiva las opciones fijadas por la directiva LIST.

• ORG: Establece el origen a partir del cual debe cargarse el programa. Si la

<etiqueta> es especificada, a esta se le dará el valor <expr>. Si no se especifica la

ORG, el código comenzará en la dirección cero.

La sintaxis es la siguiente:

[<etiqueta>] org <expr>

Ejemplo:

entero_1 org 0x20

. ; El código del vector 20 irá aquí.

entero_2 org entero_1+ 0x10

. ; El código del vector 30 irá aquí.

• PAGE: Inserta un salto de página dentro del archivo del listado.

• PAGESEL: Es una instrucción del linkador para generar código de selección de

página, fijando los bits de selección de página, a la página que contiene la

designada <etiqueta>. Sólo se puede especificar una <etiqueta>, la cual debe estar

previamente definida.

Sintaxis:

pagesel <etiqueta>

Ejemplo:

pagesel IrDestino

...

pagesel CallDestino

call CallDestino.

• PROCESSOR: Indica el tipo de procesador.

La sintaxis es:

processor <tipo_de_procesador>

Ejemplo:

processor 16C54

Santiago Salamanca Miño 152 Escuela de Ingenierías Industriales

David Arroyo Muñoz Universidad de Extremadura](https://image.slidesharecdn.com/pic-gama-media-120720161646-phpapp01/85/Pic-problemas-resueltos-158-320.jpg)

![Microcontroladores PIC de la Gama Media. 5. Programación con PIC.

• RADIX: Fija la base de numeración por defecto de las expresiones de datos. Los

valores válidos para radix son: hex, dec, ó oct.

Sintaxis:

radix <radix_defecto>

Ejemplo:

radix dec

• RES: Produce que el contador de programa avance desde la actual localización

tantas posiciones como se especifican en <unidades_memoria>. La <etiqueta> se

inicializará como una dirección.

Sintaxis:

[<etiqueta>] res <unidades_memoria>

Ejemplo:

buffer res 64 ; reserva 64 palabras de almacenaje.

• SPACE: Inserta <expr> números de líneas en blanco en el archivo de listado.

Sintaxis:

space <expr>

Ejemplo:

space 3 ; Inserta tres líneas en blanco.

• TITLE y SUBTITLE: <texto_de_título> y <texto_subtítulo> son cadenas

imprimibles de caracteres ASCII encerradas por un doble entrecomillado. Éstas

deben ser de 60 caracteres como máximo. Estas directivas imprimen en la cabecera

de cada página del archivo de listado el texto del título y subtítulo, siendo este

último en la segunda línea.

Sintaxis:

title “<texto_de_título>”

subtitle “<texto_subtítulo>”

Ejemplo:

title “Código operacional, rev 5.0”

subtitle “sección de diagnóstico”

Santiago Salamanca Miño 153 Escuela de Ingenierías Industriales

David Arroyo Muñoz Universidad de Extremadura](https://image.slidesharecdn.com/pic-gama-media-120720161646-phpapp01/85/Pic-problemas-resueltos-159-320.jpg)

![Microcontroladores PIC de la Gama Media. 5. Programación con PIC.

• UDATA: Se utiliza en la generación de código objeto. Indica el comienzo de una

sección de datos no inicializados. Si <etiqueta> no se especifica, a la sección se la

nombrará udata. Si no se indica la dirección, ésta se inicializará a cero. En este

segmento no se puede producir código.

Sintaxis:

[<etiqueta>] udata [<dirección RAM>]

Ejemplo:

udata

Var1 res 1

Doble res 2

• UDATA_OVR: Se utiliza en la generación de código objeto. Indica el inicio de

una sección de datos no inicializados reutilizables. Si <etiqueta> no se especifica, a

la sección se la nombrará udata_ovr. Si no se indica la dirección, ésta se

inicializará a cero. El espacio ocupado por esta sección puede ser cubierto por otra

sección udata_ovr del mismo nombre. Esto es una buena forma de crear variables

temporales, permitiendo declarar múltiples variables en la misma localización de

memoria. En este segmento no se puede producir código.

Sintaxis:

[<etiqueta>] udata_ovr [<dirección RAM>]

Ejemplo:

Temps udata_ovr

Temp1 res 1

Temp2 res 1

Temp3 res 1

Temps udata_ovr

LargoTemp1 res 2

LargoTemp2 res 2

• UDATA_SHR: Se utiliza en la generación de código objeto. Indica el inicio de

una sección de datos no inicializados compartidos. Si <etiqueta> no se especifica,

a la sección se la nombrará udata_shr. Si no se indica la dirección, ésta se

inicializará a cero. Esta directiva se usa para declarar variables que están situadas

en RAM que está compartida por todos los bancos. En este segmento no se puede

producir código.

Sintaxis:

[<etiqueta>] udata_shr [<dirección RAM>]

Santiago Salamanca Miño 154 Escuela de Ingenierías Industriales

David Arroyo Muñoz Universidad de Extremadura](https://image.slidesharecdn.com/pic-gama-media-120720161646-phpapp01/85/Pic-problemas-resueltos-160-320.jpg)

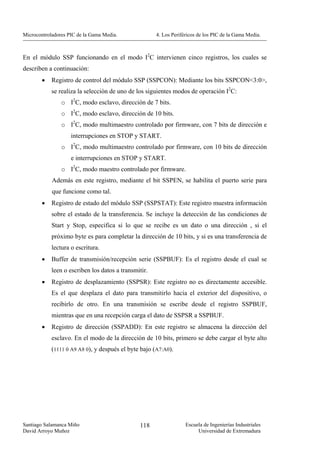

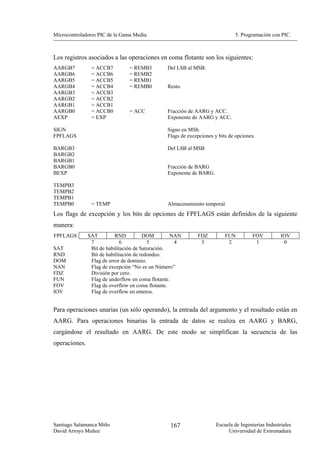

![Microcontroladores PIC de la Gama Media. 5. Programación con PIC.

Las rutinas para las familias PIC16CXXX y PIC17CXXX están en un formato modificado de

IEEE 754 de 32 bits junto con versiones en un formato reducido de 24 bits.

Para operaciones unarias, el dato de entrada y el resultado están en AARG, excepto las rutinas

sin cos, en las cuales el coseno se almacena en AARG y el seno en BARG. La función

potencia requiere entrada de datos en AARG y BARG, obteniendo el resultado en AARG.

Aunque las rutinas de comparación lógica también requieren entrada de datos en AARG y

BARG, el resultado se obtiene en el registro W.

5.5.3.1 Función raíz cuadrada.

El dominio natural de la función raíz cuadrada es todos los números positivos, siendo el

dominio efectivo [0, MAXNUM], entendiendo por MAXNUM el mayor número que se puede

representar en formato de coma flotante. Todas las rutinas empiezan por un testeo del dato

para ver si está dentro del dominio, produciendo un error de dominio en caso de que esté fuera

del intervalo.

En los PIC17CXXX utilizan el multiplicador hardware para resolver la raíz cuadrada

mediante el método iterativo por aproximaciones sucesivas de Newton – Raphson. Siendo

x = f · 2 e , donde 1 ≤ f < 2, al calcular su raíz se utilizan las siguientes expresiones:

e

2

x = f ·2 ,si e es par (5.13)

e

2

x = f· 2 ·2 , si e es impar (5.14)

La aproximación para f se calcula mediante el método de Newton – Raphson, partiendo de

un valor tabulado.

⎛ f ⎞

y = ⎜ y0 +

⎜ ⎟/2 (5.15)

⎝ y0 ⎟

⎠

Debido a que la memoria de los PIC16CXXX es más pequeña, se han de buscar métodos

alternativos para resolver esta función. En este caso, para el formato de 24 bits, la

Santiago Salamanca Miño 174 Escuela de Ingenierías Industriales

David Arroyo Muñoz Universidad de Extremadura](https://image.slidesharecdn.com/pic-gama-media-120720161646-phpapp01/85/Pic-problemas-resueltos-180-320.jpg)

![Microcontroladores PIC de la Gama Media. 5. Programación con PIC.

aproximación f se obtiene por la segmentación en polinomios de cuarto grado, mediante el

método de la aproximación mínima2 (minimax approximation) en los intervalos [1, 1.5] y

[1.5, 2]. En el formato de 32 bits, la función f = 1 + z en el intervalo [0, 1] de z, se obtiene

la aproximación de la forma

p(z)

1 + z = 1+ z , donde z ≡ f + 1. (5.16)

q(z)

5.5.3.2 Funciones exponenciales.

Mientras que el dominio de las funciones exponenciales abarca todos los números reales, la

representación de los números en coma flotante limita el dominio al intervalo [MINLOG,

MAXLOG], siendo:

MINLOG = ln(2-126) (5.17)

MAXLOG = ln(2128) (5.18)

Todas las rutinas empiezan por un testeo del dato para ver si está dentro del dominio,

produciendo un error de dominio en caso de que esté fuera del intervalo.

Para el formato reducido de 24 bits, la función exponencial es evaluada utilizando la siguiente

identidad:

x

ex = 2 ln 2

= 2 n + z = 2 n ·2 z , (5.19)

donde n es un número entero y 0 ≤ z < 1. La función exponencial de base dos, se aproxima

mediante el polinomio mínimo de tercer grado en una representación segmentada en los

subintervalos [0, 0.25], [0.25, 0.5], [0.5, 0.75] y [0.75, 1], con una exactitud de 0.5uld

(unidades de la última posición) a lo largo de todo el dominio [MINLOG, MAXLOG].

2

La teoría conocida como aproximación mínima, consiste en la aproximación de una función mediante un

polinomio de grado n, que cumple que el error máximo es el mínimo posible y debe darse al menos en n+2

puntos, alternando el signo del intervalo de aproximación.

Santiago Salamanca Miño 175 Escuela de Ingenierías Industriales

David Arroyo Muñoz Universidad de Extremadura](https://image.slidesharecdn.com/pic-gama-media-120720161646-phpapp01/85/Pic-problemas-resueltos-181-320.jpg)

![Microcontroladores PIC de la Gama Media. 5. Programación con PIC.

Para el formato de 32 bits, la falta de rutinas de precisión extendida, hace que se requieran

algoritmos más complejos para aproximarse a los 0.5 ulp, y llegando en el peor de los casos a

obtener un error de 1 ulp.

La función exponencial en este caso está basada en una expansión

e x = e z + n ln2 = 2 n · e z , (5.20)

donde n es un entero y –0.5 ln2 ≤ z < 0.5 ln2, evaluando la función exponencial mediante la

aproximación del polinomio mínimo de quinto grado en los subintervalos [-0.5 ln2, 0] y [0,

0.5 ln2].

El argumento z es obtenido de la expresión z = x – n · ln 2. El mayor error producido por este

método viene dado por la realización de esta diferencia., por eso se han desarrollado métodos

de precisión pseudo extendida, donde ln 2 se descompone en dos números, siendo:

ln 2 = c1 – c2 , (5.21)

donde c1 = 0.693359375 y c2 = 0.00021219444005469, haciendo entonces la evaluación de z

de la forma

z = (x – n · c1) + n · c2, (5.22)

donde el término encerrado en el paréntesis se calcula exacto, produciéndose sólo errores de

redondeo en el segundo término.

Las rutinas de la exponencial de base 10 para los formatos de 24 y 32 bits, son completamente

análogas a las rutinas exponenciales vistas anteriormente, sustituyendo la base e por 10 en

cada caso. Estas rutinas son comunes para las familias de los PIC16CXXX y PIC17CXXX.

5.5.3.3 Funciones logarítmicas.

El dominio efectivo de los logaritmos es (0, MAXNUM], donde MAXNUM es el mayor

número que se pueda representar en coma flotante. Todas las rutinas empiezan con un testeo

del argumento para ver si se encuentra dentro del dominio, en caso contrario devuelven un

error de dominio.

Santiago Salamanca Miño 176 Escuela de Ingenierías Industriales

David Arroyo Muñoz Universidad de Extremadura](https://image.slidesharecdn.com/pic-gama-media-120720161646-phpapp01/85/Pic-problemas-resueltos-182-320.jpg)

![Microcontroladores PIC de la Gama Media. 5. Programación con PIC.

Para el formato reducido de 24 bits, dado la disponibilidad de las rutinas de precisión

extendida, la función log se evalúa usando la siguiente identidad:

ln x = ln 2 · log 2 x = ln 2 · (n + log 2 f ) , (5.23)

donde n es un número entero y 0.5 ≤ f <1. El valor de log 2 f = log 2 (1 + z) se obtiene de la

1

representación de la función en los subintervalos de z [ − 1 , 0] y [0, 2 − 1 ], usando la

2

aproximación racional del mínimo de la forma

p(z)

log 2 (1 + z) ≈ z , (5.24)

q(z)

donde p(z) es una función lineal y q(z) cuadrática.

Para un formato de 32 bits, la forma de hacer el logaritmo es mediante la expansión

ln x = ln f + ln 2 n = ln f + n · ln 2, (5.25)

donde n es un número entero y 0.5 ≤ f <1. El valor de ln f = ln(1 + z) se obtiene de la

1

representación de la función en los subintervalos de z [ − 1 , 0] y [0, 2 − 1 ], usando la

2

aproximación racional del mínimo de la forma

⎛ p(z) ⎞

ln(1 + z) ≈ z − 0.5 · z 2 + z ⎜ z 2 ·

⎜ ⎟ , (5.26)

⎝ q(z) ⎟

⎠

donde p(z) es una función lineal y q(z) cuadrática. Esta parte racional da un resultado exacto,

estando el error en el segundo término. Para reducir este error se utiliza para la evaluación, un

método de precisión pseudo extendida que tiene la siguiente aritmética:

ln f + n · ln 2 = (ln f – n · c2) + n · c1 , (5.27)

donde la descomposición de ln 2 es la misma que la utilizada en la función exponencial.

La rutina para el cálculo del logaritmo decimal con el formato de 24 bits es completamente

análogo al del cálculo del logaritmo neperiano cambiando la base e por 10 en todos los casos.

Santiago Salamanca Miño 177 Escuela de Ingenierías Industriales

David Arroyo Muñoz Universidad de Extremadura](https://image.slidesharecdn.com/pic-gama-media-120720161646-phpapp01/85/Pic-problemas-resueltos-183-320.jpg)

![Microcontroladores PIC de la Gama Media. 5. Programación con PIC.

Para el caso del formato de 32 bits, el logaritmo decimal se obtiene mediante la conversión

del logaritmo neperiano, es decir, haciendo la multiplicación en coma fija del logaritmo

decimal de e por el resultado del logaritmo neperiano.

log x = log e · ln x (5.28)

5.5.3.4 Funciones Trigonométricas.

En la evaluación de las funciones seno y coseno, el dominio es infinito, por lo que se

requieren técnicas de reducción de los argumentos.

Susceptibles de errores de redondeo y cancelación, estos procesos siempre fallarán para

argumentos mayores de cierto valor, llevando a la perdida de precisión. El tamaño de este

valor (LOOSTHR), a partir del cual se producen errores, depende del algoritmo utilizado para

la reducción y la precisión deseada, dando un valor de;

π 24 2

LOOSTHR = · 2 = 1024 · π (5.29)

4

para esta implementación usando un método con pseudo precisión extendida y corrientemente

disponible en coma fija y en precisión simple para rutinas en coma flotante. Cuando se sobre

pasa este valor se informa mediante un error de dominio.

Teniendo el argumento x en el intervalo [-LOSSTHR, LOSSTHR], se calcula el argumento z

⎡ π π⎤

comprendido en el intervalo ⎢− , ⎥ , mediante la siguiente definición:

⎣ 4 4⎦

π

z = x mod , (5.30)

4

produciendo la primera evaluación de las relaciones ‘y’ y ‘j’.

x y

y= , j=8· ,

π4 8

donde j indica el octante donde se encuentra el ángulo. Para el uso apropiado de las rutinas de

seno o coseno se introduce una lógica adicional sobre j para obtener el correcto valor del

Santiago Salamanca Miño 178 Escuela de Ingenierías Industriales

David Arroyo Muñoz Universidad de Extremadura](https://image.slidesharecdn.com/pic-gama-media-120720161646-phpapp01/85/Pic-problemas-resueltos-184-320.jpg)

![Microcontroladores PIC de la Gama Media. 5. Programación con PIC.

fracciones impares tal como 1/3 para la raíz cúbica, no pueden ser representadas exactamente

con un número binario en coma flotante, por eso se plantean problemas en la definición y el

reconocimiento de tales casos. Por tanto, ya que un dato de tipo entero no es soportado en esta

función, el dominio de la función potencia queda restringido al intervalo [0, MAXNUM] para

‘x’ y [-MAXNUM, MAXNUM] para ‘y’, que sujeto a los requerimientos el rango es también

[0, MAXNUM].

Además los siguientes casos especiales serán resueltos de la forma:

x 0 ≡ 1, x≥0

0 y ≡ MAXNUM, y < 0,

donde MAXNUM se puede devolver a través de overflow y saturación si estuviese habilitada.

Cuando las rutinas de precisión extendida están habilitadas, el cálculo de la función potencia

xy es normalmente realizada usando la identidad

xy = exp(y · ln x), (5.40)

contando con la precisión extendida de la evaluación de la función log y de la exponencial

para el control del error de propagación. La implementación para el formato reducido de 24

bits utiliza las funciones log y exponencial de 32 bits obteniendo un error relativo de 0.5 ulp.

La carencia de rutinas de precisión extendida para el formato de 32 bits requiere mayor

esfuerzo y más sofisticados métodos de precisión pseudo extendida para controlar el error de

propagación. Ya que el error relativo ene una función exponencial es proporcional al error

absoluto del argumento, hay que tener especial cuidado con los algoritmos basados en una

identidad exponencial. Estos métodos generalmente tratan de obtener como resultado una

potencia entera de dos, seguida por los cálculos requeridos por las aproximaciones, sobre un

intervalo relativamente pequeño. Para esto, la representación del argumento x viene dada por:

x = f · 2 e , donde 0.5 ≤ f < 1. (5.41)

La función potencia se puede expresar de la forma:

x y = 2 y · log 2 x , (5.42)

Santiago Salamanca Miño 180 Escuela de Ingenierías Industriales

David Arroyo Muñoz Universidad de Extremadura](https://image.slidesharecdn.com/pic-gama-media-120720161646-phpapp01/85/Pic-problemas-resueltos-186-320.jpg)

![Microcontroladores PIC de la Gama Media. 5. Programación con PIC.

La forma final del producto es un número entero más un número de dieciseisavo más un

número del intervalo [-0.0625,0], siendo el resultado final:

x y = 2 y · log 2 x = 2 i · 2 -n/16 · 2 h , (5.49)

donde 2h es evaluada por la aproximación mínima de la forma

2 h − 1 ≈ h + h · p(h) , (5.50)

siendo p un polinomio de segundo grado.

Normalmente esta función sólo es soportada por los PIC17CXXX.

5.5.3.6 Función parte entera por defecto.

Otra función de las librerías matemáticas es la operación floor(x) ≡ ⌊x⌋, la cual encuentra el

mayor entero no superior a x, y lo expresa en coma flotante. La implementación usada aquí

encuentra la localización del punto binario implícito en el exponente, determinando de este

modo el bit por debajo del cual hay que poner todo a cero.

Dos ejemplos de esta función son:

FLOOR24 (123.45) = FLOOR24 (0x8576E6) =0x857600 = 123.0 (5.51)

FLOOR24 (-123.45) = FLOOR24 (0x85F6E6) =0x857800 = -124.0 (5.52)

5.5.3.7 Comparación lógica en coma flotante.

En los cálculos frecuentemente se requiere relacionar números mediante los operadores <

(menor), <= (menor o igual), > (mayor), >= (mayor o igual), ═ ═ (igual), != (distinto). Estas

comparaciones se realizan llamando a las rutinas TALTBxx (A<B), TALEBxx (A<=B),

TAGTBxx (A>B), TAGEBxx (A>=B), TAEQBxx (A=B), y TANEBxx (A!=B).

Las comparaciones necesarias se hacen empezando por el exponente, seguidas si es necesario

por los bytes que forman la mantisa empezando por los de mayor peso, hasta completar todos

los bits. Los argumentos son testeados en los registros AARG y BARG, devolviendo como

resultado un entero en W, que será un uno en caso de que la condición se dé y un cero si no es

cierta.

Santiago Salamanca Miño 182 Escuela de Ingenierías Industriales

David Arroyo Muñoz Universidad de Extremadura](https://image.slidesharecdn.com/pic-gama-media-120720161646-phpapp01/85/Pic-problemas-resueltos-188-320.jpg)