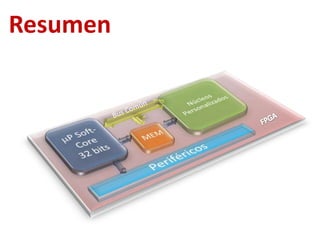

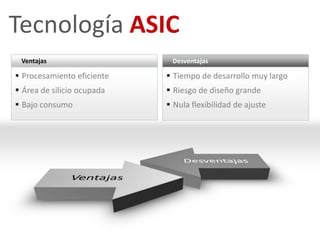

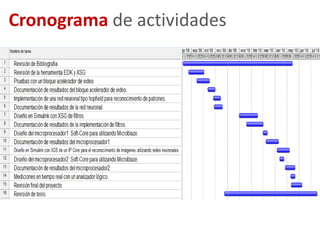

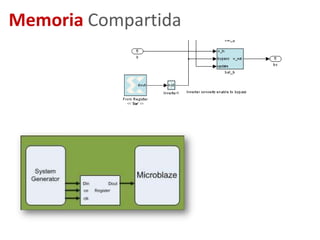

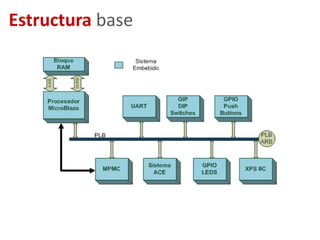

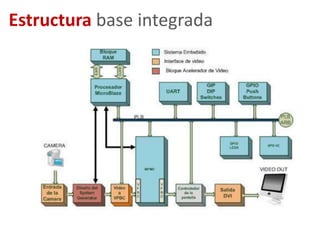

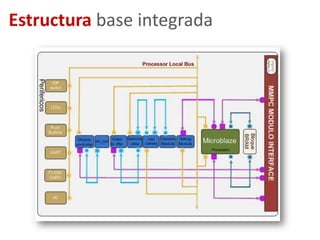

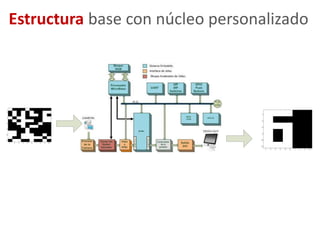

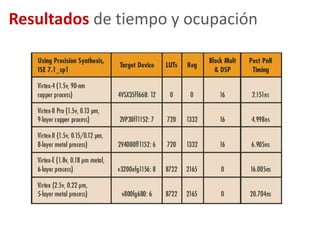

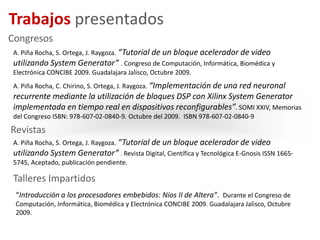

El documento presenta un protocolo y los avances de una tesis sobre el diseño de un sistema embebido que utiliza un microprocesador soft-core y dispositivos reconfigurables. Se abordan aspectos como la justificación, objetivos, metodología y avances en técnicas de procesamiento para aplicaciones específicas en tratamiento de imágenes y video. Además, se discuten las ventajas y desventajas de diferentes tecnologías, así como los resultados de trabajos presentados en congresos y publicaciones relacionadas.