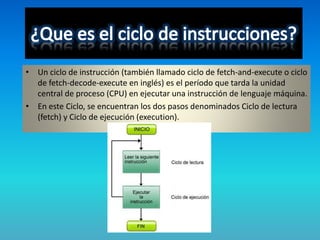

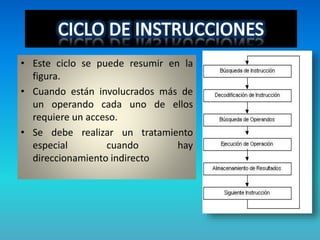

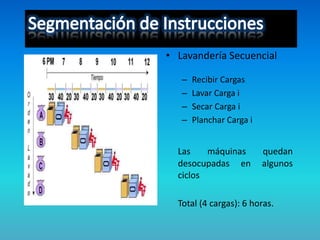

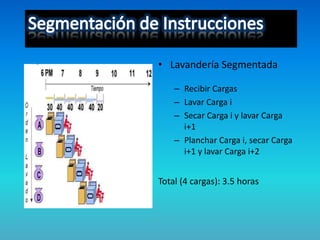

El documento describe las etapas del ciclo de instrucción de una CPU, incluyendo la búsqueda (IF), decodificación (ID), ejecución (EX) y escritura (WB). Explica que el ciclo de instrucción involucra la obtención de instrucciones de la memoria principal, su decodificación e implementación antes de buscar la siguiente instrucción. También menciona que la segmentación del ciclo de instrucción permite la ejecución simultánea de múltiples instrucciones para mejorar el rendimiento.