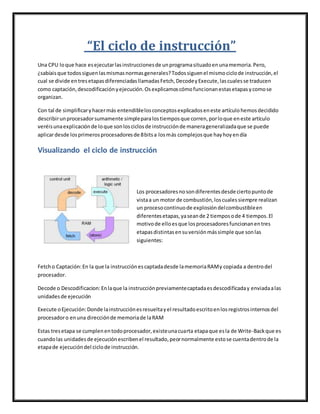

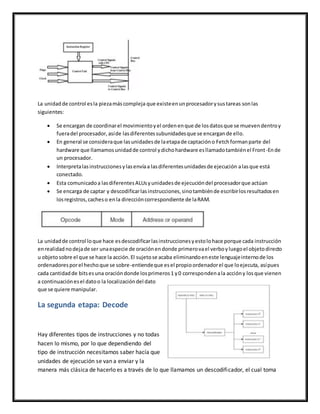

Este ensayo aborda el ciclo de instrucción en las arquitecturas de computadoras, detallando las etapas de fetch, decode y execute, así como la segmentación de instrucciones y su impacto en el rendimiento del procesador. Se explican los componentes involucrados en cada etapa y las características de los conjuntos de instrucciones, destacando las diferencias entre CISC y RISC. Finalmente, se discuten los modos de direccionamiento y los formatos de instrucción que afectan cómo se procesan los datos en la CPU.