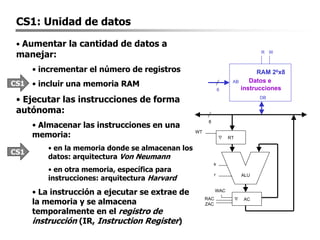

Este documento describe la arquitectura de una unidad de datos (CS1) que incluye registros, una ALU y una memoria RAM. Explica cómo la CS1 ejecuta instrucciones de forma autónoma al almacenarlas en memoria e ir cargando sucesivamente las instrucciones en un registro de instrucción. Detalla las fases de búsqueda y ejecución de instrucciones, usando como ejemplo la instrucción ADD. Finalmente, muestra un pequeño programa de ejemplo y su representación en memoria RAM.

![CS1: Unidad de datos (2)

• En el CS1, las instrucciones

incluyen un campo de dirección de

operando (CD) donde se indica la

dirección de la RAM donde se

encuentra el operando

Cada instrucción tiene dos partes:

• Código de operación (CO): tipo de

operación a realizar

• Operandos: datos con los que la

instrucción va a trabajar:

• A veces la instrucción no necesita

operandos; otras veces, los

operandos están implícitos y no hay

que incluirlos en la instrucción

CS1

R W

AB

DB

RAM 26x8

6

OpCD

CONTROLXs

CO

IR

TB

2

6[8]

8

CS1 • |IR|=8bits; |CD|=6bits ⇒

|CO|=2bits ⇒ 4 tipos de instrucciones](https://image.slidesharecdn.com/etc20304cs1-150515214901-lva1-app6891/85/PDF-ing-sumoso-2015-Etc2-0304-cs1-2-320.jpg)

![CS1: Unidad de datos (4)

ALU

RT

AC

AB

DB

RAM 26x8

CONTROL

IR[8]

CO CD

2

6

TB

MAR

TIR

TPC

PC

6

IPC

CLPC PC

6

CD

6

El bus de

direcciones de la

RAM debe ser

accedido por:

R W

6

• El campo CD

del registro IR:

para poder

acceder al

operando en

memoria

8

WT

• El registro PC:

para poder

indicar la

dirección de la

siguiente

instrucción

s

r

Xs

WAC

ZAC

RAC

• Se incluye el registro de direcciones de memoria (MAR, Memory

Address Register) para almacenar temporalmente la dirección de la

instrucción (TPC) o del dato (TIR)](https://image.slidesharecdn.com/etc20304cs1-150515214901-lva1-app6891/85/PDF-ing-sumoso-2015-Etc2-0304-cs1-4-320.jpg)

![CS1: Instrucciones. Fase de búsqueda (1)

En el CS1, para

cargar la

siguiente

instrucción en IR,

necesitamos dos

ciclos de reloj:

6

AB

DB

RAM 26x8

MAR

TIR

TPC

PC

6

IPC

CLPC

Dir_Instr (dirección de la instrucción)

R W

ALU

RT

AC

CONTROL

CO CD

2

IR[8]

1. MAR ← PC

6

8

TB

WT

2. IR ← RAM;

PC ← PC + 1

s

r

Xs

WAC

ZAC

RAC](https://image.slidesharecdn.com/etc20304cs1-150515214901-lva1-app6891/85/PDF-ing-sumoso-2015-Etc2-0304-cs1-6-320.jpg)

![CS1: Instrucciones. Fase de búsqueda (2)

6

AB

DB

RAM 26x8

MAR

TIR

TPC

PC

6

IPC

CLPC

Dir_Instr

Dir_Instr

Dir_Instr

R W

Dir_Instr Instrucción

ALU

RT

AC

8

CONTROL

CO CD

2

Instrucción

IR[8]

1. MAR ← PC

6

TB

WT

2. IR ← RAM;

PC ← PC + 1

s

r

Xs

WAC

ZAC

RAC](https://image.slidesharecdn.com/etc20304cs1-150515214901-lva1-app6891/85/PDF-ing-sumoso-2015-Etc2-0304-cs1-7-320.jpg)

![CS1: Instrucciones. Fase de búsqueda (fin)

Tras la fase de

búsqueda:

• la instrucción

a ejecutar está

almacenada en

IR

• PC contiene la

dirección de la

siguiente

instrucción

6

AB

DB

RAM 26x8

MAR

TIR

TPC

PC

6

IPC

CLPC

Dir_Instr

Dir_Instr

Dir_Instr +1

R W

ALU

RT

AC

CONTROL

IR[8]

CO CD

2

6

Instrucción

8

TB

WT

s

r

Xs

WAC

ZAC

RAC](https://image.slidesharecdn.com/etc20304cs1-150515214901-lva1-app6891/85/PDF-ing-sumoso-2015-Etc2-0304-cs1-8-320.jpg)

![CS1: Instrucciones. Fase de ejecución [ADD] (1)

RT

AC

ALU

8

6

AB

DB

RAM 26x8

CONTROL

IR[8]

Dir_dato

2

6

TB

MAR

TIR

TPC

PC

6

IPC

CLPC

01

(ADD)

La fase de

ejecución

comienza donde

terminó la fase de

búsqueda.

ADD:

AC ← AC + RAM(Dir_dato)

1º Extraer el dato

(2 clk):

AC0

Dir_Instr +1

Dir_Instr

Dir_Instr

R W

WT

1. MAR ← IR s

2. RT ← RAM

r

Xs

2º Realizar la suma

(1 clk):

WAC

ZAC

RAC

3. AC ← AC + RT

Nota: antes de comenzar, AC = AC0](https://image.slidesharecdn.com/etc20304cs1-150515214901-lva1-app6891/85/PDF-ing-sumoso-2015-Etc2-0304-cs1-9-320.jpg)

![CS1: Instrucciones. Fase de ejecución (2)

6

AB

DB

RAM 26x8

MAR

TIR

TPC

PC

6

IPC

CLPC

Dir_dato

Dir_dato

Dir_Instr +1

R W

Dir_dato Dato

LU

RT

WT

AC AC0

WAC

ZAC

RAC

s

r A

8

CONTROL

IR[8]

Dir_dato

2

6

01

(ADD)

Xs

TB

ADD:

AC ← AC + RAM(Dir_dato)

1º Extraer el dato

(2 clk):

Dato

1. MAR ← IR

2. RT ← RAM

2º Realizar la suma

(1 clk):

3. AC ← AC + RT](https://image.slidesharecdn.com/etc20304cs1-150515214901-lva1-app6891/85/PDF-ing-sumoso-2015-Etc2-0304-cs1-10-320.jpg)

![CS1: Instrucciones. Fase de ejecución (3)

6

AB

DB

RAM 26x8

MAR

TIR

TPC

PC

6

IPC

CLPC

Dir_dato

Dir_dato

Dir_Instr +1

R W

AC

LU

AC0

AC+Dato

RT

Dato

WT

WAC

ZAC

RAC

s

r A

8

CONTROL

IR[8]

Dir_dato

2

6

01

(ADD)TB

ADD:

AC ← AC + RAM(Dir_dato)

1º Extraer el dato

(2 clk):

1. MAR ← IR

2. RT ← RAM Xs

2º Realizar la suma

(1 clk):

3. AC ← AC + RT](https://image.slidesharecdn.com/etc20304cs1-150515214901-lva1-app6891/85/PDF-ing-sumoso-2015-Etc2-0304-cs1-11-320.jpg)

![CS1: Instrucciones. Fase de ejecución (fin)

Al terminar la

fase de

ejecución de

ADD, el registro

AC queda

actualizado con

el resultado de

la suma.

El sistema está

listo para buscar

y ejecutar la

siguiente

instrucción

(apuntada por

PC).

6

AB

DB

RAM 26x8

MAR

TIR

TPC

PC

6

IPC

CLPC

Dir_dato

Dir_dato

Dir_Instr +1

R W

LU

RT

Dato

WT

AC

WAC

ZAC

RAC

AC0+Dato

s

r A

CONTROL

IR[8]

Dir_dato

2

6

01

(ADD)

8

TB

Xs](https://image.slidesharecdn.com/etc20304cs1-150515214901-lva1-app6891/85/PDF-ing-sumoso-2015-Etc2-0304-cs1-12-320.jpg)