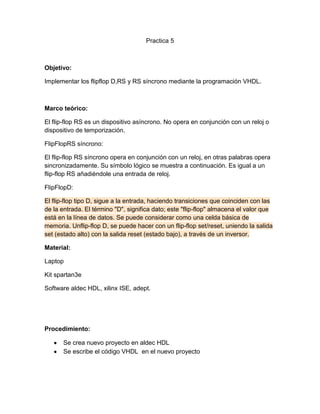

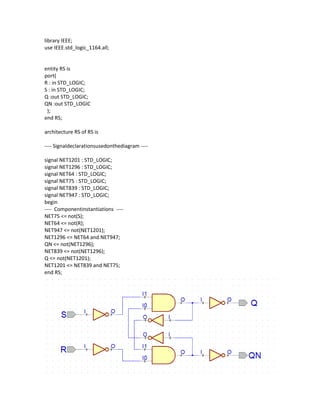

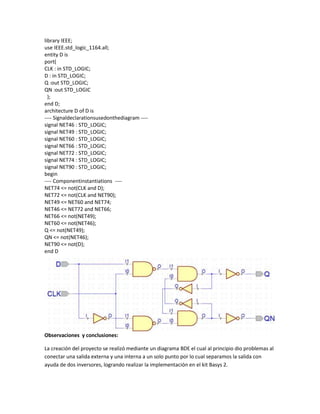

Este documento describe la implementación de flip-flops D, RS y RS síncrono mediante código VHDL. Se creó un proyecto en Aldec HDL y se escribió el código VHDL para cada tipo de flip-flop. El código fue probado en un kit Spartan3E y se logró implementar con éxito los flip-flops en un kit Basys 2, aunque inicialmente hubo problemas al conectar una salida externa e interna que se resolvieron separando la salida con dos inversores.