Incrustar presentación

Descargar para leer sin conexión

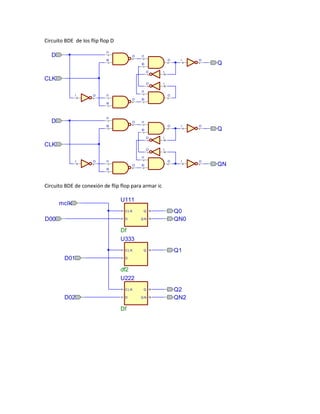

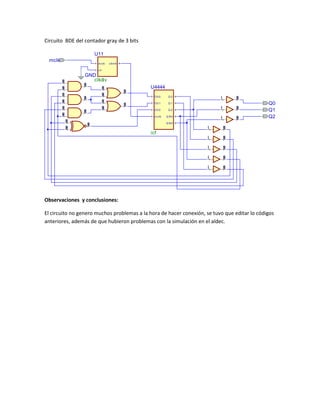

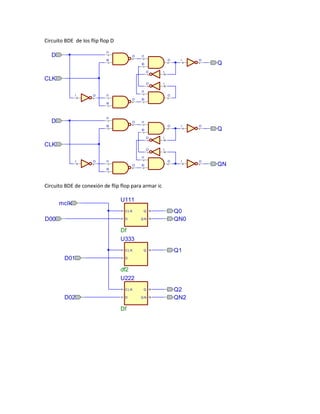

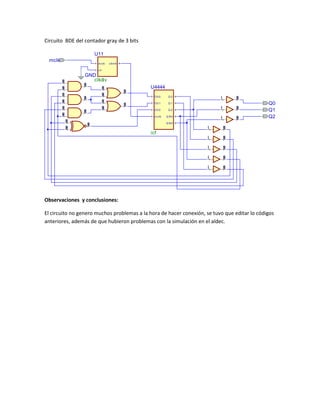

Este documento describe el diseño de un contador Gray de 3 bits implementado con VHDL. Se creó un nuevo proyecto en Aldec HDL donde se escribió el código VHDL para el contador. El circuito utiliza flip-flops D para almacenar cada bit y se conectan según el código Gray para cambiar solo un bit cada vez. Se simuló el diseño pero hubo problemas que requirieron editar el código. El objetivo de implementar un contador Gray en VHDL se logró.