⭐⭐⭐⭐⭐ SOLUCIÓN EVALUACIÓN SISTEMAS DIGITALES 1, 2do Parcial (2020 PAO 2)

•

0 recomendaciones•13,009 vistas

El documento presenta 5 problemas relacionados con la conversión de diferentes tipos de flip-flops (FF-SD, FF-JK, FF-YZ, FF-XY) a FF-XY. Cada problema contiene una descripción del funcionamiento de un tipo de flip-flop, opciones de expresiones booleanas y un espacio para la resolución. El objetivo es determinar las expresiones correctas para las señales J y K de un FF-JK para realizar la conversión a cada uno de los tipos de flip-flops presentados.

Denunciar

Compartir

Denunciar

Compartir

Descargar para leer sin conexión

Recomendados

Recomendados

Más contenido relacionado

La actualidad más candente

La actualidad más candente (11)

⭐⭐⭐⭐⭐ SOLUCIÓN LECCIÓN FUNDAMENTOS DE ELECTRICIDAD Y SISTEMAS DIGITALES, 2do ...

⭐⭐⭐⭐⭐ SOLUCIÓN LECCIÓN FUNDAMENTOS DE ELECTRICIDAD Y SISTEMAS DIGITALES, 2do ...

Electrónica digital: sistemas secuenciales maquina de estado

Electrónica digital: sistemas secuenciales maquina de estado

Similar a ⭐⭐⭐⭐⭐ SOLUCIÓN EVALUACIÓN SISTEMAS DIGITALES 1, 2do Parcial (2020 PAO 2)

Similar a ⭐⭐⭐⭐⭐ SOLUCIÓN EVALUACIÓN SISTEMAS DIGITALES 1, 2do Parcial (2020 PAO 2) (11)

⭐⭐⭐⭐⭐ FUNDAMENTOS DEL DISEÑO DIGITAL, EXAMEN RESUELTO 2do PARCIAL (2018 2do T...

⭐⭐⭐⭐⭐ FUNDAMENTOS DEL DISEÑO DIGITAL, EXAMEN RESUELTO 2do PARCIAL (2018 2do T...

Diferentes tipos de flip flops (jk, sr, d, t) sus tablas de verdad,

Diferentes tipos de flip flops (jk, sr, d, t) sus tablas de verdad,

⭐⭐⭐⭐⭐ SISTEMAS DIGITALES 1, LECCION RESUELTA 2do PARCIAL (2018 1er Término)

⭐⭐⭐⭐⭐ SISTEMAS DIGITALES 1, LECCION RESUELTA 2do PARCIAL (2018 1er Término)

Diseño de un contador sincrónico con flip-Flop JK, haciendo uso de mapas de k...

Diseño de un contador sincrónico con flip-Flop JK, haciendo uso de mapas de k...

Más de Victor Asanza

Más de Victor Asanza (20)

⭐⭐⭐⭐⭐ Device Free Indoor Localization in the 28 GHz band based on machine lea...

⭐⭐⭐⭐⭐ Device Free Indoor Localization in the 28 GHz band based on machine lea...

⭐⭐⭐⭐⭐ SOLUCIÓN EXAMEN SISTEMAS DIGITALES 2, 1er Parcial (2022PAO2)

⭐⭐⭐⭐⭐ SOLUCIÓN EXAMEN SISTEMAS DIGITALES 2, 1er Parcial (2022PAO2)

⭐⭐⭐⭐⭐ Trilateration-based Indoor Location using Supervised Learning Algorithms

⭐⭐⭐⭐⭐ Trilateration-based Indoor Location using Supervised Learning Algorithms

⭐⭐⭐⭐⭐ Learning-based Energy Consumption Prediction

⭐⭐⭐⭐⭐ Learning-based Energy Consumption Prediction

⭐⭐⭐⭐⭐ Raspberry Pi-based IoT for Shrimp Farms Real-time Remote Monitoring wit...

⭐⭐⭐⭐⭐ Raspberry Pi-based IoT for Shrimp Farms Real-time Remote Monitoring wit...

⭐⭐⭐⭐⭐Classification of Subjects with Parkinson's Disease using Finger Tapping...

⭐⭐⭐⭐⭐Classification of Subjects with Parkinson's Disease using Finger Tapping...

⭐⭐⭐⭐⭐ SOLUCIÓN EVALUACIÓN SISTEMAS EMBEBIDOS, 1er Parcial (2022 PAO1)

⭐⭐⭐⭐⭐ SOLUCIÓN EVALUACIÓN SISTEMAS EMBEBIDOS, 1er Parcial (2022 PAO1)

⭐⭐⭐⭐⭐ CHARLA #PUCESE Arduino Week: Hardware de Código Abierto TSC-LAB

⭐⭐⭐⭐⭐ CHARLA #PUCESE Arduino Week: Hardware de Código Abierto TSC-LAB

⭐⭐⭐⭐⭐ #BCI System using a Novel Processing Technique Based on Electrodes Sele...

⭐⭐⭐⭐⭐ #BCI System using a Novel Processing Technique Based on Electrodes Sele...

⭐⭐⭐⭐⭐ SOLUCIÓN LECCIÓN SISTEMAS DIGITALES 2, 2do Parcial (2021PAO2) C6

⭐⭐⭐⭐⭐ SOLUCIÓN LECCIÓN SISTEMAS DIGITALES 2, 2do Parcial (2021PAO2) C6

⭐⭐⭐⭐⭐ Performance Comparison of Database Server based on #SoC #FPGA and #ARM ...

⭐⭐⭐⭐⭐ Performance Comparison of Database Server based on #SoC #FPGA and #ARM ...

⭐⭐⭐⭐⭐ SOLUCIÓN EXAMEN SISTEMAS DIGITALES 2, 1er Parcial (2021PAO2)

⭐⭐⭐⭐⭐ SOLUCIÓN EXAMEN SISTEMAS DIGITALES 2, 1er Parcial (2021PAO2)

⭐⭐⭐⭐⭐ Charla FIEC: #SSVEP_EEG Signal Classification based on #Emotiv EPOC #BC...

⭐⭐⭐⭐⭐ Charla FIEC: #SSVEP_EEG Signal Classification based on #Emotiv EPOC #BC...

⭐⭐⭐⭐⭐ #FPGA Based Meteorological Monitoring Station

⭐⭐⭐⭐⭐ #FPGA Based Meteorological Monitoring Station

⭐⭐⭐⭐⭐ SSVEP-EEG Signal Classification based on Emotiv EPOC BCI and Raspberry Pi

⭐⭐⭐⭐⭐ SSVEP-EEG Signal Classification based on Emotiv EPOC BCI and Raspberry Pi

⭐⭐⭐⭐⭐ SOLUCIÓN EVALUACIÓN SISTEMAS DIGITALES 1, 1er Parcial (2021 PAO1)

⭐⭐⭐⭐⭐ SOLUCIÓN EVALUACIÓN SISTEMAS DIGITALES 1, 1er Parcial (2021 PAO1)

⭐⭐⭐⭐⭐ SISTEMAS DIGITALES 2, PROYECTOS PROPUESTOS (2021 PAO1)

⭐⭐⭐⭐⭐ SISTEMAS DIGITALES 2, PROYECTOS PROPUESTOS (2021 PAO1)

⭐⭐⭐⭐⭐ SISTEMAS DIGITALES 1, PROYECTOS PROPUESTOS (2021 PAE)

⭐⭐⭐⭐⭐ SISTEMAS DIGITALES 1, PROYECTOS PROPUESTOS (2021 PAE)

⭐⭐⭐⭐⭐ Localización en ambiente de interiores basado en Machine Learning con r...

⭐⭐⭐⭐⭐ Localización en ambiente de interiores basado en Machine Learning con r...

Último

Último (20)

La Sostenibilidad Corporativa. Administración Ambiental

La Sostenibilidad Corporativa. Administración Ambiental

2 REGLAMENTO RM 0912-2024 DE MODALIDADES DE GRADUACIÓN_.pptx

2 REGLAMENTO RM 0912-2024 DE MODALIDADES DE GRADUACIÓN_.pptx

Lecciones 05 Esc. Sabática. Fe contra todo pronóstico.

Lecciones 05 Esc. Sabática. Fe contra todo pronóstico.

Tema 19. Inmunología y el sistema inmunitario 2024

Tema 19. Inmunología y el sistema inmunitario 2024

Los avatares para el juego dramático en entornos virtuales

Los avatares para el juego dramático en entornos virtuales

Concepto y definición de tipos de Datos Abstractos en c++.pptx

Concepto y definición de tipos de Datos Abstractos en c++.pptx

⭐⭐⭐⭐⭐ SOLUCIÓN EVALUACIÓN SISTEMAS DIGITALES 1, 2do Parcial (2020 PAO 2)

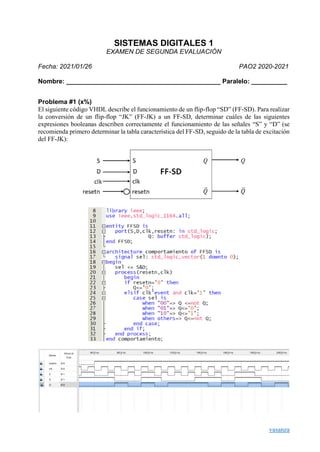

- 1. vasanza SISTEMAS DIGITALES 1 EXAMEN DE SEGUNDA EVALUACIÓN Fecha: 2021/01/26 PAO2 2020-2021 Nombre: ___________________________________________ Paralelo: __________ Problema #1 (x%) El siguiente código VHDL describe el funcionamiento de un flip-flop “SD” (FF-SD). Para realizar la conversión de un flip-flop “JK” (FF-JK) a un FF-SD, determinar cuáles de las siguientes expresiones booleanas describen correctamente el funcionamiento de las señales “S” y “D” (se recomienda primero determinar la tabla característica del FF-SD, seguido de la tabla de excitación del FF-JK):

- 2. vasanza Las opciones son las siguientes: a) J <= not(S) or not (D) b) K <= not(S) or not (D) c) J <= not(S) or D d) K <= not(S) or D e) J <= S or not (D) f) K <= S or not (D) g) J <= S or D h) K <= S or D Resolución:

- 3. vasanza MÁS PREGUNTAS RELACIONADAS Problema #1 (x%) El siguiente código VHDL describe el funcionamiento de un flip-flop “YZ” (FF-YZ). Para realizar la conversión de un flip-flop “JK” (FF-JK) a un FF-YZ, determinar cuál de las siguientes expresiones booleanas describe correctamente el funcionamiento de las señales “J” y “K” (se recomienda primero determinar la tabla característica del FF-YZ, seguido de la tabla de excitación del FF-JK): Las opciones son las siguientes: a) J <= not(Y) or not (Z); K <= not(Y) or Z b) J <= not(Y) or Z; K <= Y or not(Z) c) J <= Y or not(Z); K <= Y or Z d) J <= Y or Z; K <= not(Y) or not (Z).

- 4. vasanza Resolución: Problema #2 (x%) El siguiente código VHDL describe el funcionamiento de un flip-flop “XY” (FF-XY). Para realizar una conversión de un flip-flop “JK” (FF-JK) a un FF-XY, determinar cuáles de las siguientes expresiones booleanas describen correctamente el funcionamiento de las señales “J” y “K” (se recomienda primero determinar la tabla característica del FF-XY, seguido de la tabla de excitación del FF-JK):

- 5. vasanza Las opciones son las siguientes: a) j <= not(x) or not (y); b) j <= not(x) or y; c) j <= x or not(y); d) j <= x or y; e) k <= not(x) or not (y); f) k <= not(x) or y; g) k <= x or not(y); h) k <= x or y; Resolución: Problema #3 (x%) El siguiente código VHDL describe el funcionamiento de un flip-flop “XY” (FF-XY). Para realizar una conversión de un flip-flop “JK” (FF-JK) a un FF-XY, determinar cuáles de las siguientes expresiones booleanas describen correctamente el funcionamiento de las señales “J” y “K” (se recomienda primero determinar la tabla característica del FF-XY, seguido de la tabla de excitación del FF-JK):

- 6. vasanza Las opciones son las siguientes: a) j <= not(x) or not (y); b) j <= not(x) or y; c) j <= x or not(y); d) j <= x or y; e) k <= not(x) or not (y); f) k <= not(x) or y; g) k <= x or not(y); h) k <= x or y; Resolución:

- 7. vasanza Problema #4 (x%) El siguiente código VHDL describe el funcionamiento de un flip-flop “XY” (FF-XY). Para realizar una conversión de un flip-flop “JK” (FF-JK) a un FF-XY, determinar cuáles de las siguientes expresiones booleanas describen correctamente el funcionamiento de las señales “J” y “K” (se recomienda primero determinar la tabla característica del FF-XY, seguido de la tabla de excitación del FF-JK): Las opciones son las siguientes: a) j <= not(x) or not (y); b) j <= not(x) or y; c) j <= x or not(y); d) j <= x or y; e) k <= not(x) or not (y); f) k <= not(x) or y; g) k <= x or not(y); h) k <= x or y;

- 8. vasanza Resolución: Problema #5 (x%) El siguiente código VHDL describe el funcionamiento de un flip-flop “XY” (FF-XY). Para realizar una conversión de un flip-flop “JK” (FF-JK) a un FF-XY, determinar cuáles de las siguientes expresiones booleanas describen correctamente el funcionamiento de las señales “J” y “K” (se recomienda primero determinar la tabla característica del FF-XY, seguido de la tabla de excitación del FF-JK):

- 9. vasanza Las opciones son las siguientes: a) j <= not(x) or not (y); b) j <= not(x) or y; c) j <= x or not(y); d) j <= x or y; e) k <= not(x) or not (y); f) k <= not(x) or y; g) k <= x or not(y); h) k <= x or y; Resolución: