Curso a Integradores.pdf

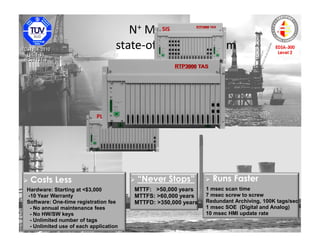

- 1. 5 msec scan time 12 msec screw to screw Redundant Archiving, 100K tags/sec 1 msec SOE (Digital and Analog) 10 msec HMI update rate Runs Faster Runs Faster 1 msec scan time 7 msec screw to screw Redundant Archiving, 100K tags/sec 1 msec SOE (Digital and Analog) 10 msec HMI update rate Runs Faster Runs Faster MTTF: >50,000 years MTTFS: >60,000 years MTTFD: >350,000 years “Never Stops” “Never Stops” N+ Multiprocessor state-of-the-art System PLC DCS SIS Hardware: Starting at <$3,000 -10 Year Warranty Software: One-time registration fee - No annual maintenance fees - No HW/SW keys - Unlimited number of tags - Unlimited use of each application Costs Less Costs Less

- 7. One-time registration fee - Project License $5,000 - Limited Version $2,500 No annual maintenance fees No HW/SW keys Unlimited number of tags Unlimited use of each application Costs Less Software (NetSuite): ISA Secure EDSA-300 Level 2 AES Encryption Algorithm - Block Size 128 bits - Key Length 256 bits Cyber Security Cyber Security Intel Atom @1.33GHz 512 Mbyte SDRAM 64bits wide 12 msec screw to screw 1 msec SOE (Digital and Analog) Stores up to 300,000 events Redundant Archiving, 100K tags/sec Runs Faster Never Stops * Numbers provided by TUV MTTF:* >50,000 Years MTTFS:* >60,000 Years MTTFD:* >350,000 Years Redundant I/O Network Redundant I/O Network Node Processor: Intel® Atom™ • 5 msec scan rate • Solves Logic 3 times per scan • Engineering unit conversion • Input validation and voting • Encrypt host communications • Communications validation • Peer to peer communications • Alarm and HMI communications Chassis Processor: RISCore 32300 • Chassis I/O scanning • 1 msec SOE (Digital and Analog) • 1 msec Alarm time stamping • Results validation and voting • Bus validation • I/O integrity checks • Field device checking • Field wire checking Redundant I/O Network Redundant I/O Network Single Chassis, P.S., & Processor <$3K All Analog/Digital inputs SOE enabled Proof Test - Not required for SIL-3 Unlimited online downloads CPUs physically separated 10 year Warranty MTTF >50,000 (Cost of an outage?) Hardware: 3000 TAS:

- 8. •1 msec scan rate •Solves Logic N times per scan • Engineering unit conversion • Input validation and voting • Encrypt host communications • Communications validation • Peer to peer communications • Alarm and HMI communications • Chassis I/O scanning • 1 msec SOE (Digital and Analog) • 1 msec Alarm time stamping • Results validation and voting • Bus validation • I/O integrity checks • Field device checking • Field wire checking Node/Chassis Processor: Intel® Atom™ Node/Chassis Processor: Intel® Atom™ One-time registration fee - Project License $5,000 - Limited Version $2,500 No annual maintenance fees No HW/SW keys Unlimited number of tags Unlimited use of each application Costs Less Software (NetSuite): “Never Stops” * Numbers provided by TUV MTTF:* >50,000 Years MTTFS:* >60,000 Years MTTFD:* >350,000 Years ISA Secure EDSA-300 Level 2 AES Encryption Algorithm - Block Size 128 bits - Key Length 256 bits Cyber Security Cyber Security Intel Atom @1.33GHz 512 Mbyte SDRAM 64bits wide 7 msec screw to screw 1 msec SOE (Digital and Analog) Stores up to 300,000 events Redundant Archiving, 100K tags/sec I/O Domain Network (Up to 14 Nodes/Domain) Hardware: 3200 N+ Single Chassis, P.S., & Processor <$3K All Analog/Digital inputs SOE enabled DI $8/point, DO $10/point AI $16/$19 (HART Enabled) per point AO $37/$41 (HART Enabled) per point 10 Year Warranty MTTF >50,000 (Cost of an outage?)

- 9. Diferenciadores de RTP 1. Costos Competitivos: • Ahorros en Software • Un solo cargo por registro para la Suite Completa • Licencia de Proyecto $5,000.00 • Versión limitada $2,500.00 • Política de Software “Precios razonables” • Uso ilimitado en numero de Tags • Uso ilimitado para cada aplicación • Upgrades incluidos • Sin cargos por mantenimientos Anuales • No llaves físicas o lógicas • Reduce inversión en capacitación. Costs less Costs less

- 10. Diferenciadores de RTP 1. Costos Competitivos: • Ahorros en Hardware • Inversión Inicial de Bajo Costo. Single chassis PS & Processor <$3,000.00 Dll • Garantía de 10 años contra defectos de Fabricación • Un solo sistema para SIS, DCS y PLC. “Seamless Integration” • Reducción de costos por partes de repuesto al utilizar un mismo sistema. • Elimina costos por obsolescencia “política de no obsolescencia” Costs less Costs less

- 11. Tiempo de Respuesta de 12 mseg (ciclo cerrado) Procesador Central • Ejecuta lógica • Conversión de Unid. Ingen. • Validación de Entradas y Voteo • Comunicación de las Alarmas • Comunicación de los Históricos • Comunicaciones con HMI y externas • Comunicaciones Peer-to-Peer • Validación de las comunicaciones • Encriptación de Datos Procesadores de Chasis • Escaneo de E/S • 1 ms SOE digital • 1 ms SOE analógico • Validación de Resultados • Validación del Bus • Chequeo Integridad de E/S • Chequeo de Instrumentación • Chequeo de Cableado Rendimiento Superior Fault Tolerant Run Faster Run Faster

- 12. El Mejor Rendimiento Fault Tolerant 7 msec response time (screw to screw)

- 14. Diferenciadores de RTP Run Faster Run Faster En aplicaciones de seguridad, una falla debe ser eliminada lo más rápido posible, esto puede significar menos daño o ningún daño al equipo, personal, y el medio ambiente

- 15. Diferenciadores de RTP Run Faster Run Faster Así que la velocidad de procesamiento en aplicaciones de seguridad significa menos daños o menos paros en falso. En otras palabras, menos coste para el usuario final.

- 16. Never Stop Alto MTTFs - Disminución de paros en Falso. MTTFs>6,000 Años Diagnósticos Exhaustivos – No necesitas parar para determinar el problema. Cada Componente es Hot Swappable – no necesitas para para reparar el sistema. Modificaciones ilimitadas en línea - no necesitas parar para implementar cambios

- 17. MTTFs segun TUV

- 18. El máximo MTTFs El MTTFS Es la frecuencia en la que el Sistema de control va disparar la planta de proceso sin razón alguna. El MTTFs te predice la frecuencia de disparos en falsos, tienen un impacto directo en la productividad e integridad de la operación de la unidad. ¿Con que frecuencia los usuarios no toman en cuenta el MTTFs al seleccionar el SIS para su Planta?

- 19. Diagnósticos = Integridad Diagnósticos continuos realizados con cada escaneo hacen posible probar la: Integridad de los módulos procesadores Integridad en las comunicaciones Integridad en el backplane, actuador y en cableado de campo Integridad en las tarjeta de entrada / salida

- 20. Cambios ilimitados en Línea El sistema soporta los siguientes cambios en línea: - Forzamientos. - Cambios simples y complejos en la programación - Agregar nuevos módulos de E/S. - Agregar nuevos chassis

- 21. Nuevas características de sistema RTP3000TAS N+ N+

- 22. Node/Chassis Processor Card 3200T Processor - Basado en el procesador de nodo Atom 3000/06, el procesador 3200T funciona como procesador de nodo y procesador de chasis. • Arquitectura Multiprocesador. • Capacidad de operar en modo simple, doble, triple o cuádruple redundante. • Software integrado para realizar proof test en línea. • Comunicaciones al Host, comunicaciones peer to peer y comunicaciones modbus TCP

- 23. SIL-3 16-Channel Analog Output Card 3144/3145/3146 Three versions of the card are available: 3144 - 0 to 20 mA Current Output 3145 - 4 to 20 mA Current Output, HART Enabled 3146 - +/- 10V Voltage Output 1. SIL-3 Approved 2. 4 to 20 mA Output with HART 3. 0 to 20 mA Output 4. ±10V, 0-10V Output 5. 16-Bit Digital to Analog Conversion 6. Single, Dual, or Triple Redundancy 7. Channel Readback Validation

- 24. SIL-3 32-Channel Digital Input Card 3147 3147-1 SIL-3 32 Ch Digital Input Card 24 VDC 3147-2 SIL-3 32 Ch Digital Input Card 48 VDC 3147-3 SIL-3 32 Ch Digital Input Card 120 VDC 3147-4 SIL-3 32 Ch Digital Input Card 120 VAC 3147-5 SIL-3 32 Ch Digital Input Card 240 VAC 3153 SIL-3 32 Ch Supervised Digital Input Card 24 VDC • SIL-3 Approved • Supports 24, 48 and 120 VDC Sinking Input Signals • Supports 120 to 230 VAC Sinking Input Signals • Line Supervision Option • 1 msec SOE resolution • Single, Dual, or Triple Redundancy

- 25. SIL-3 32-Channel Analog Input Card 3148/3149/3150/3151/3152 3148 SIL-3 32 Ch Analog Input Card w/ HART, for Single Configuration, 4 - 20 mA 3150 SIL-3 32 Ch Analog Input Card, for Single Configuration, +/- 20 mA, 4 - 20mA 3149 SIL-3 32 Ch Analog Input Card w/ HART, for Redundant Configuration, 4 - 20 mA 3151 SIL-3 32 Ch Analog Input Card for Redundant Configuration +/- 20 mA, 4 - 20mA 3152 SIL-3 32 Ch Analog Input Card +/- 10V • SIL-3 Approved • 4 to 20mA Input with HART option • 0 to 20 mA Input • +/- 10 V Input • 1 msec SOE resolution • Single, Dual, or Triple Redundancy

- 26. SIL-3 32-Channel Digital Output Card 3159 • SIL-3 Approved • Line and Load checking • Supports Source Voltages of 19 to 30 VDC • Source up to 0.5 A per Channel • 1.0 A per Channel Shorted Output Protection • Single, Dual, or Triple Redundancy • Channel Readback Validation

- 27. Chasis de 11 ranuras Chasis de 11 ranuras: proporciona una tercera opción para sistemas que requieren una sola fuente de alimentación. Los clientes ahora pueden elegir las opciones de chasis de una sola fuente de alimentación de 19 ranuras, 11 ranuras o 6 ranuras. El chasis de 15 ranuras aún está disponible para sistemas que requieren fuentes de alimentación dobles.